As semiconductor geometries shrink to 5nm and below, the industry faces a host of fresh testing challenges. Shrinking transistors, increased variability, new packaging styles, and rising system complexity all conspire to make validation harder, slower, and costlier. For teams responsible for bringing chips from design to production, mastering these hurdles is essential. In this post, we’ll walk through the principal obstacles and practical strategies that modern semiconductor testing teams use to keep pace, with a focus on pragmatic steps that semiconductor test engineers and broader test engineering organizations can adopt.

Why Advanced Nodes Break Old Assumptions

At 5nm and smaller, physical effects that were previously second-order become dominant. Process variability, quantum effects, and interconnect resistance create unpredictable behavior across lots and within wafers. Power density rises while margin shrinks, making thermal behaviors and noise coupling more severe. These changes force test engineering teams to rethink both what they measure and how they measure it.

For the semiconductor test engineer, this means test programs must grow smarter: richer stimulus, higher resolution measurements, and more context-aware algorithms that can separate benign variability from actual defects. In short, standard production test recipes are often no longer sufficient for robust semiconductor testing at scale.

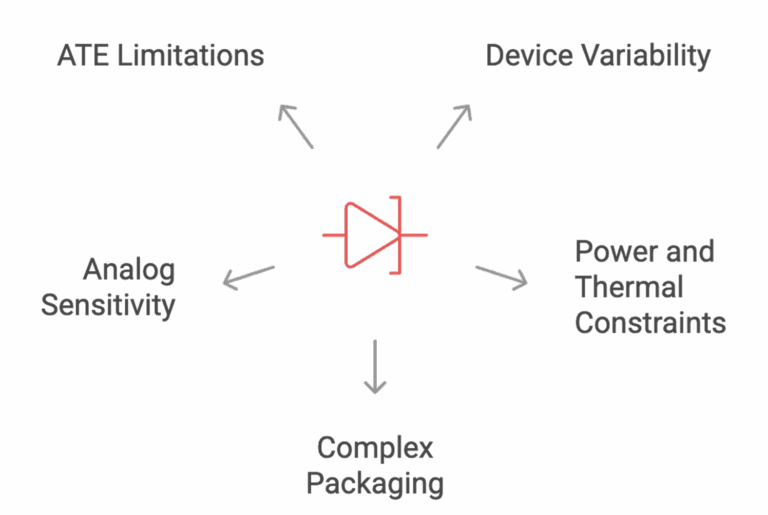

Key Technical Challenges

- Device variability and margin erosion: Smaller dimensions increase parameter spreads, requiring finer-grained statistical test methods and per-die adaptive limits so that yield loss is not mistaken for field risk.

- Power and thermal constraints: Higher power density means devices heat up during stress testing, changing characteristics. Thermal-aware test flows and on-chip temperature sensing become essential for realistic characterization and reliable manufacturing tests.

- Complex packaging and 3D integration: Chiplets, advanced packages, and heterogeneous integration add interconnect layers and new failure modes. System-level semiconductor testing and board-level validation become part of the acceptance story, not optional extras.

- Analog and mixed-signal sensitivity: With less margin, small analog errors can cause functional failures. The semiconductor test engineer must design precision measurements and carefully control test environments.

- ATE and probe limitations: Traditional automated test equipment (ATE) and probing setups may not match new demands for parallelism, low-noise measurement, and fine timing resolution. Upgrading hardware and co-optimizing test programs with ATE capabilities is a common requirement for modern test engineering groups.

Overcoming Advanced-Node Testing Challenges: Key Strategies

The Future of Test Engineering in the Semiconductor Industry

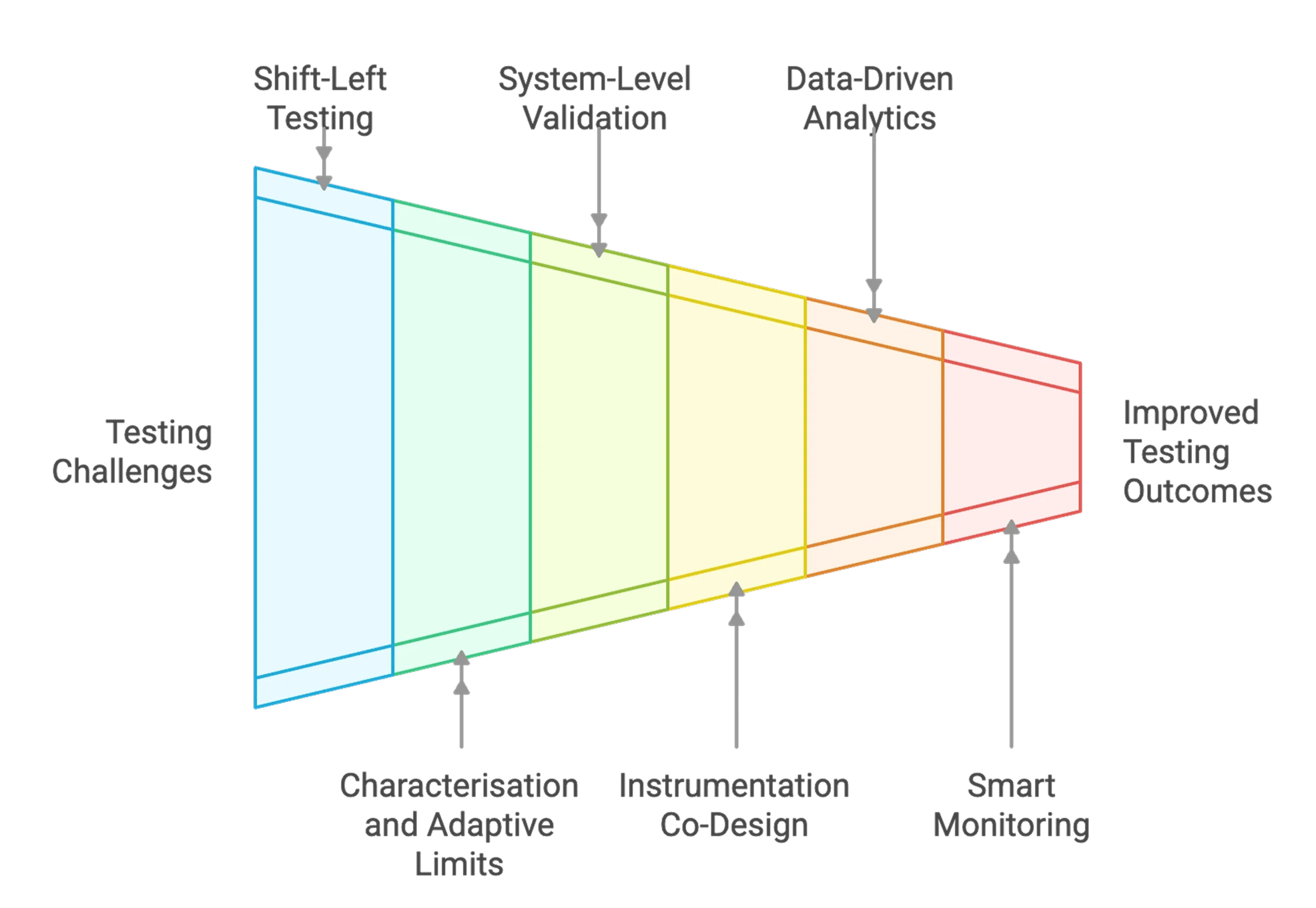

- Shift-left testing and earlier validation: To reduce late surprises, integrate testing earlier in the flow. Silicon-aware simulation, DFT (design-for-test) visibility, and early silicon bring feedback to designers sooner. When test engineering teams collaborate with design and DFT early, they can influence scan insertion, boundary-scan hooks, and observability for critical nodes, which simplifies later silicon debug and semiconductor testing coverage.

- Invest in characterisation and adaptive limits: For 5nm and below, one-size-fits-all limits fail. Instead, thorough characterization across process corners, temperatures, and voltages should feed adaptive limit methodologies. The semiconductor test engineer must build statistical models (e.g., per-lot or per-wafer models) so testing discriminates between process-induced shifts and manufacturing defects, improving both yield and field quality.

- Embrace system-level and mixed-signal validation: Advanced-node chips rarely operate alone. SLT (system-level test), hardware-in-the-loop setups, and real-application workloads will reveal interactions that simple functional patterns miss. A cohesive test engineering approach incorporates system-level scenarios into final acceptance tests and correlates system failures back to device-level metrics to close the loop on debug.

- Improve instrumentation and ATE co-design: To measure subtle effects at 5nm, both the ATE and probe infrastructure need upgrades: better thermal control, faster timing engines, and lower-noise analog front ends. The semiconductor test engineer should partner with ATE vendors and in-house hardware teams to co-design fixtures and handlers that preserve signal integrity during semiconductor testing.

- Use data-driven analytics and AI for yield learning: High-volume data from characterization, wafer maps, and in-line monitors is a goldmine. Modern test engineering groups apply statistical learning and anomaly detection to cluster failure modes, find latent correlations, and prioritize root-cause investigations. Automated triage reduces manual debugging time and accelerates corrective actions.

- Integrate Smart Monitoring and Contingent Extended Testing: To balance yield protection with deeper process insights, product and test engineers can embed targeted monitoring tests within the ATE program that do not affect production yield but provide valuable visibility into device behavior. In addition, contingent extended tests can be triggered selectively when critical datasheet parameters fail. These controlled tests help capture information on process variations and device anomalies without introducing systemic yield loss. The key is to apply such monitoring and extended routines judiciously—limiting their scope, frequency, and duration—so that test time overhead remains manageable. Once the process and device performance stabilize, these additional routines can be phased out, ensuring optimized throughput without compromising learning.

- Strengthen failure analysis and feedback loops: When a new failure mode appears, rapid failure analysis (FA), from electrical debug to package delidding and imaging, is critical. Close collaboration between FA labs and semiconductor test engineer teams ensures that lessons learned feed design and process changes quickly, shortening cycles and minimizing repeated yield loss.

Innovations in Test Engineering: Advanced Design-for-Test (DFT) Techniques for Modern ICs

People and Process: Training and Cross-functional Teams

At nodes this advanced, success is not just technical; it’s organizational. Cross-functional teams where design, DFT, PTE, and FA experts work tightly together reduce handoff delays. Investing in skill development for test engineering and hiring seasoned semiconductor test engineer talent who understand both silicon and system behavior pays off quickly.

Cost vs. Time-to-market Tradeoffs

Aggressive test coverage and characterization increase up-front cost and time, but uncontrolled escapes or repeat respins are far more expensive. Smart tradeoffs targeted stress tests, risk-based sampling, and adaptive test compression to help balance cost, quality, and schedule.

Roadmap: Where Teams Should Invest Next

- Upgrade ATE and probing for thermal and low-noise measurements.

- Expand lab capabilities for system-level validation and reliability qualification.

- Implement data platforms for yield analytics and fast root-cause feedback.

- Adopt adaptive test limits and per-die intelligence to avoid unnecessary overkill.

- Build stronger partnerships with packaging and process teams to anticipate integration risks.

Role of Test Engineering in the Semiconductor Industry

Tessolve: Partnering to Solve Advanced-node Test Challenges

At Tessolve, we understand the gap between cutting-edge chip design and manufacturing-ready test flow. As a provider of end-to-end test engineering and lab services, Tessolve offers test program development, system-level test, reliability qualification, and failure analysis, all tailored to advanced-node demands. Their teams design ATE programs, build probe and handler solutions, and run comprehensive characterization campaigns that help customers move from prototype to high-volume production with confidence. If your roadmap includes 5nm or below, collaborating with a specialist semiconductor testing partner and experienced semiconductor test engineer resources like Tessolve reduces risk, shortens debug cycles, and improves yield outcomes.