Building a reliable and robust 93K test load board is far more than just connecting a device to a tester. Engineers face a unique set of challenges that span meticulous power delivery, maintaining excellent signal behavior, and handling thermal stress during prolonged test cycles. Whether you’re a seasoned test professional or just diving into advanced board design, understanding these key areas is critical for optimizing performance and reducing costly iterations.

Let’s explore what makes modern load board design so fascinating, and demanding, and how cutting-edge approaches are transforming how we solve these challenges on platforms like 93K.

Understanding the 93K Landscape

The 93K platform from Advantest stands as one of the most powerful Automated Test Equipment (ATE) systems used in high-volume semiconductor testing. It’s widely adopted for testing complex digital, analog, and mixed-signal devices at high speeds with accuracy and repeatability.

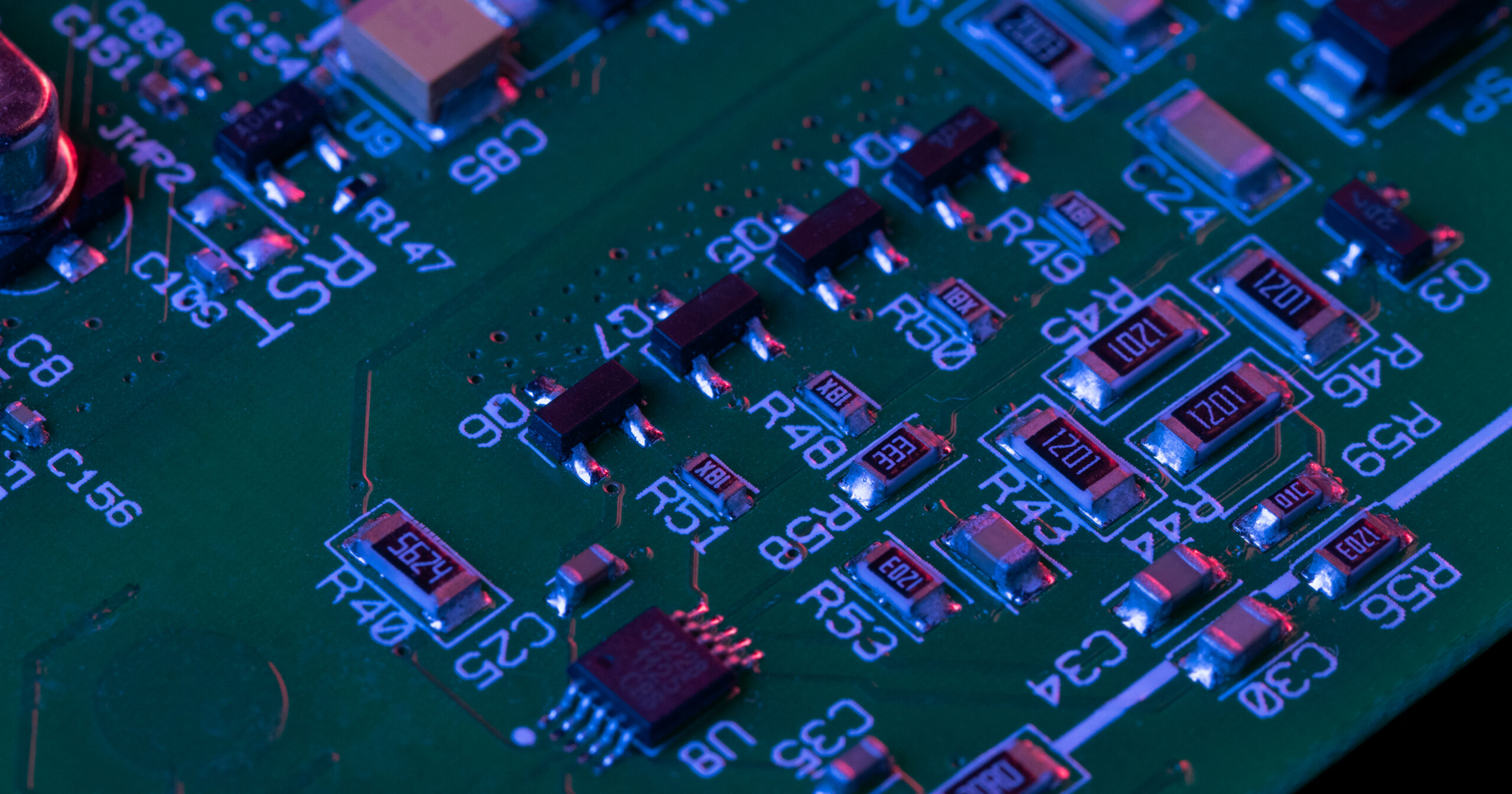

Within this environment, a load board is not just a passive connector; it’s an intelligent interface between the tester and the Device Under Test (DUT). This interface must deliver clean power, preserve signal integrity, and manage heat, each of which can make or break test results.

Power Delivery: More Than Just Voltage

When you think about the power side of a test load board, it’s tempting to focus simply on delivering the right voltages. However, high-performance boards for 93K systems must do much more:

- Stable Voltage Rails: Modern chips often require multiple power domains, from core voltages to I/O supplies, each with tight tolerances. The load board must support these domains while minimizing noise and voltage droop during dynamic switching events.

- Efficient Distribution: High current paths and plane integrity are critical. Poor layout can lead to undesired IR drops that affect both the DUT and the tester’s perception of its performance.

- Decoupling Optimization: Strategic placement of decoupling capacitors near critical nodes helps absorb transient currents and maintain cleaner power delivery over a range of operating conditions.

When these aspects are designed well, they not only ensure optimal DUT operation but also improve yield by reducing false failures that stem from poor power behavior.

Signal Integrity: Keeping Your Data Clean

Once power delivery is sorted, attention turns to the quality of the signals traveling between the DUT and tester, a domain where even small imperfections can lead to big issues.

At its heart, signal integrity testing isn’t just about preserving waveform shape; it’s about understanding how every trace, via, connector, and interface will affect high-speed digital signals. In a 93K load board, this means carefully managing:

- Impedance control: Maintaining consistent impedance as traces traverse layers, interconnects, and connectors to prevent reflections.

- Crosstalk mitigation: Ensuring high-speed channels don’t interfere with neighboring channels, especially crucial when testing multi-lane interfaces or SoCs with parallel buses.

- Return path continuity: Designing power and ground planes such that return currents can follow the signal path without unnecessary detours that increase loop inductance and radiated noise.

It’s important to remember that at high speeds (e.g., multi-gigabit lanes), signal integrity isn’t an afterthought; it’s an integral part of design validation. Tools like TDR (Time Domain Reflectometry) and advanced EDA simulation are commonly used to anticipate issues before fabrication.

And because this area is deeply technical, many teams refer to professional signal integrity testing methodologies to catch subtle issues early in the design cycle, reducing expensive redesigns later.

3D Multilayer PCBs: Layout Techniques to Reduce Footprint Without Losing Signal Integrity

Thermal Management: Keeping Cool Under Pressure

Test systems like 93K often push devices hard, generating significant heat both on the DUT and across the load board itself. Thermal issues are often silent culprits behind inconsistent test results and reduced DUT lifespans.

Effective thermal management starts with understanding where heat is generated:

- High-current traces and planes can heat up due to resistive losses.

- Power devices and regulators on the board often become concentrated heat sources.

- Hot DUTs, especially high-performance processors or power management ICs, need to dissipate heat quickly to avoid throttling.

To tackle this, designers employ a mix of techniques:

- Thermal vias and planes: These help spread heat vertically and laterally.

- Heat sinks and interface materials: If the DUT runs hot, external cooling structures may be required.

- Component placement: Ensuring heat-sensitive components are kept away from primary heat sources.

Balancing thermal considerations without sacrificing signal integrity or power delivery performance is an art, and one that directly influences test reliability and throughput.

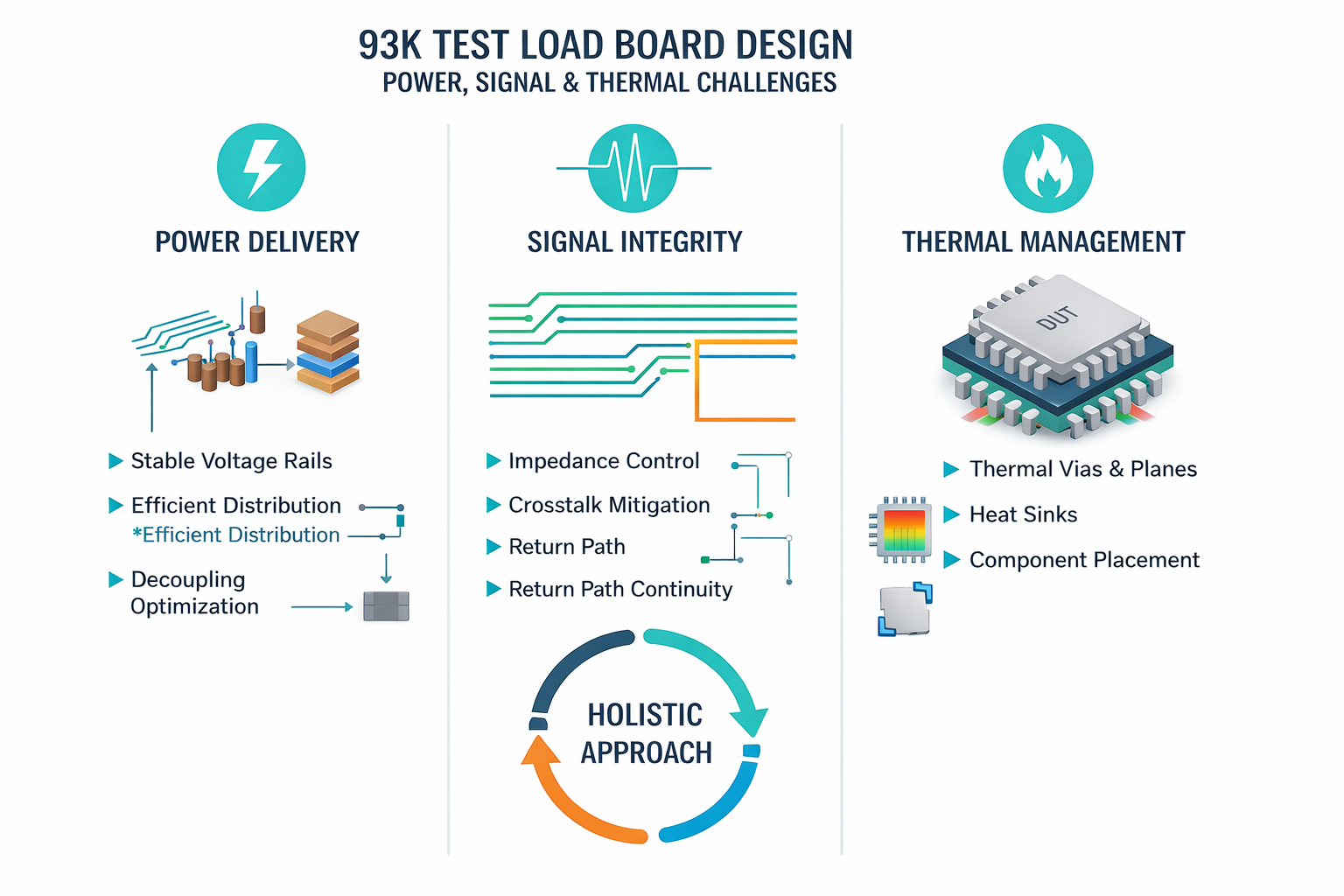

The three pillars of 93K Load Board Design: Power Delivery, Signal Integrity, and Thermal Management.

Bringing It Together: A Synergistic Approach

One of the hardest parts of load board design on 93K systems is that power delivery, signal integrity, and thermal performance don’t exist in isolation:

- Improving one area can sometimes stress another. For example, adding decoupling near a high-speed channel might improve power stability but complicate routing for clean signal paths without crosstalk.

- Layout decisions must be holistic, often requiring iterative simulation using tools like SI/PI and thermal modeling.

This is where having a robust test engineering workflow pays dividends, from initial schematic capture to final verification. Top teams blend simulation and measurement data to make informed decisions throughout the design cycle.

Tessolve’s Perspective: Engineering Excellence You Can Rely On

At Tessolve, we understand the critical role that advanced load board design plays in semiconductor test success, especially on complex systems like the 93K. With over two decades of experience in silicon engineering and testing, we offer comprehensive services across test development, PCB design, post-silicon validation, and advanced lab infrastructure that help customers navigate even the most demanding test challenges.

Our expertise spans semiconductor testing, advanced power delivery strategies, signal integrity testing, and thermal analysis, enabling engineers to accelerate time-to-market with confidence. Leverage our seasoned team of professionals and world-class facilities to optimize your load board designs, improve test throughput, and ensure consistent, high-quality results in high-volume environments.

Partner with Tessolve and take advantage of proven know-how that transforms complex testing requirements into efficient and reliable solutions from concept to production.

Frequently Asked Questions

1. What is a test load board, and why is it important for 93K systems?

A test load board interfaces the DUT with the tester, ensuring accurate power, signals, and thermal handling during semiconductor testing.

2. How does signal integrity affect high-speed testing on load boards?

Poor signal integrity can cause reflections, crosstalk, or errors, impacting test reliability and yielding misleading results in signal integrity testing.

3. Why is thermal management critical in load board design?

High currents and active DUTs generate heat, which can reduce test accuracy, damage components, or cause intermittent failures.

4. How do test engineers optimize power delivery on 93K load boards?

They use decoupling capacitors, plane design, and voltage rail isolation to maintain clean, stable power across all device domains.