| Conference: | Verification Futures 2024 (click here to see full programme) |

| Speaker: | Sreejith Sudhakaran |

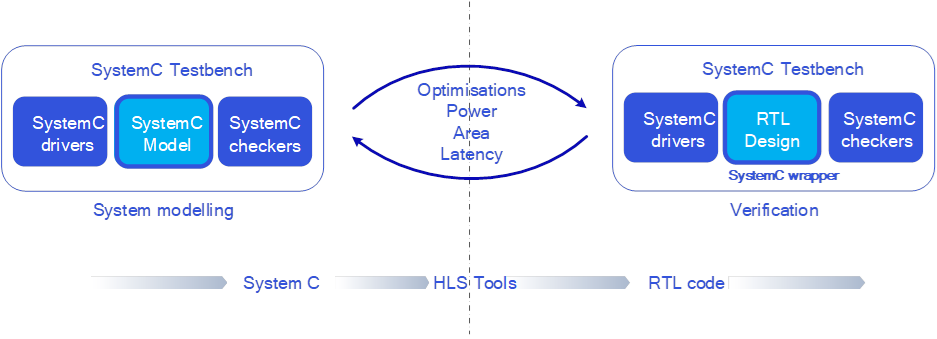

| Presentation Title: | Challenges and opportunities in SystemC and HLS based functional verification |

| Abstract: | Sreejith Sudhakaran is currently leading Digital Design and Verification of IPs/SOCs in Qualcomm Technologies International, Ltd, Cambridge. He is a proud postgraduate of University of Essex and has more than 20 years of domain experience in Design and Verification of SOCs from strategy, architecture, planning, execution and sign off. His area of expertise includes System Architecture, System C based design, Low power sims, Gate level, PG-Gate level and Formal verification.

|

| Speaker Bio: | Sreejith Sudhakaran is currently leading Digital Design and Verification of IPs/SOCs in Qualcomm Technologies International, Ltd, Cambridge. He is a proud postgraduate of University of Essex and has more than 20 years of domain experience in Design and Verification of SOCs from strategy, architecture, planning, execution and sign off. His area of expertise includes System Architecture, System C based design, Low power sims, Gate level, PG-Gate level and Formal verification. |

| Key Points: |

|