This presentation contains forward-looking statements based on current expectations or beliefs, as well as a number of preliminary assumptions about future events that are subject to factors and uncertainties that could cause our actual results to differ materially from those expectations or results described in the forward-looking statements. You are cautioned not to put undue reliance on these forward-looking statements, which are not a guarantee of future performance and are subject to a number of risks, uncertainties and other factors, many of which are outside Cadence's control.

# Agentic AI: Continuing Evolution of EDA

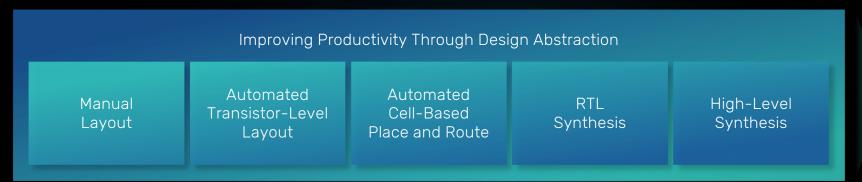

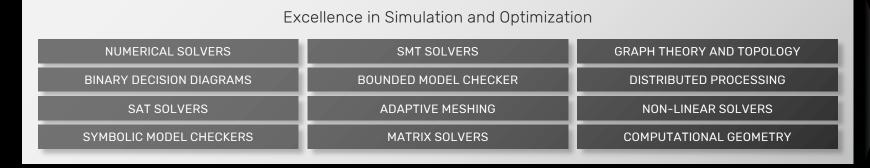

EDA's 40-Year History

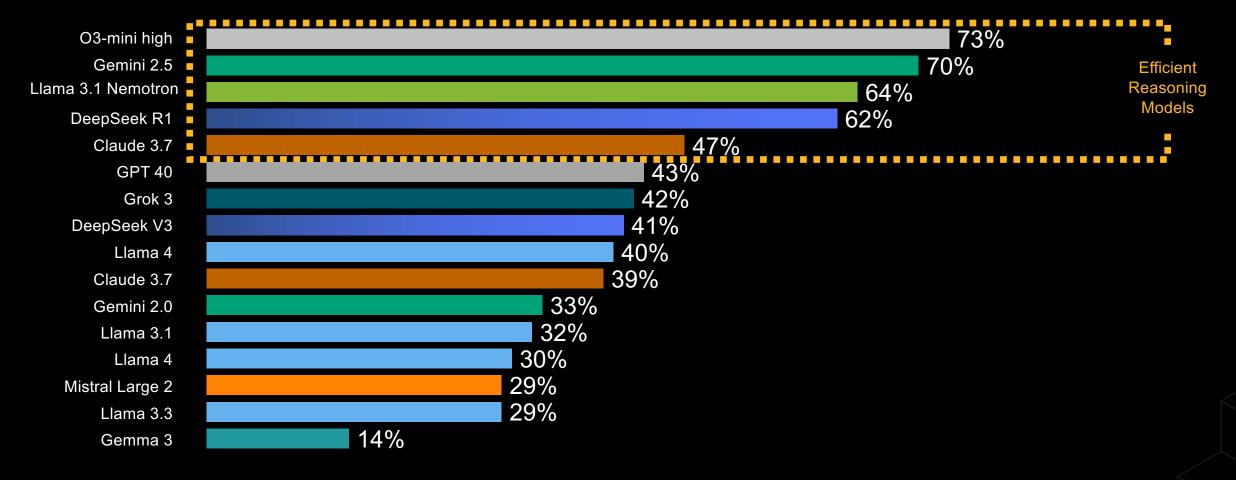

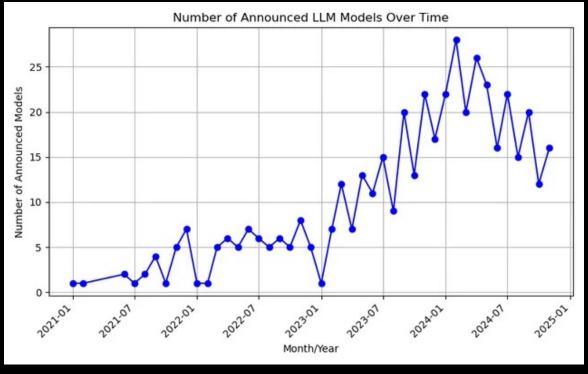

# The Emergence of Reasoning Models

LiveCodeBench (Coding) Results

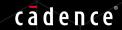

# New Protocols Are Enabling Plug-and-Play Agentic Systems

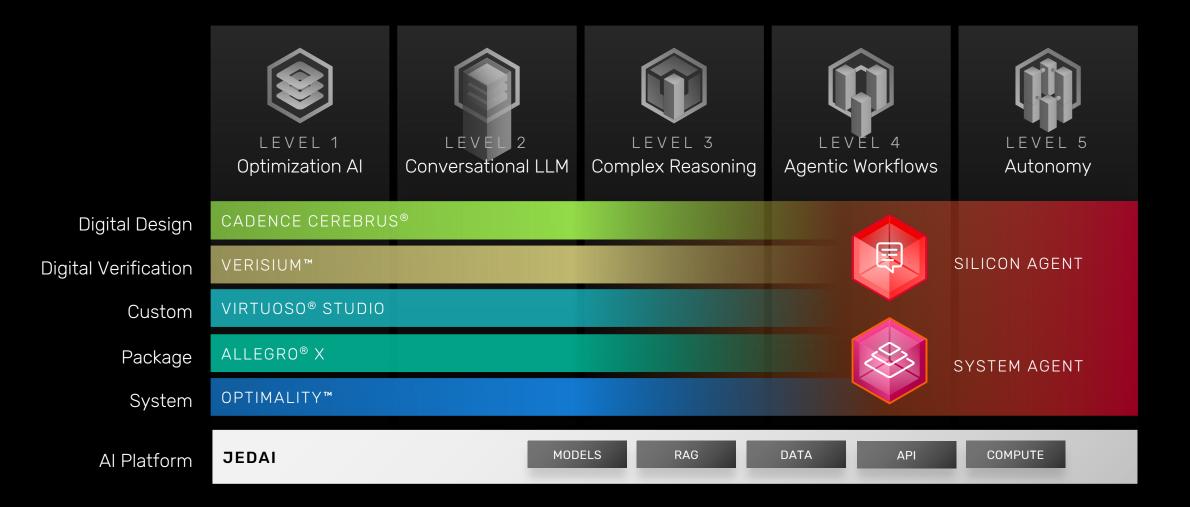

## The Journey to Autonomous Design

# Optimization AI in Digital Verification: Verisium SimAI

Xcelium™

LEVEL 1

Optimization AI

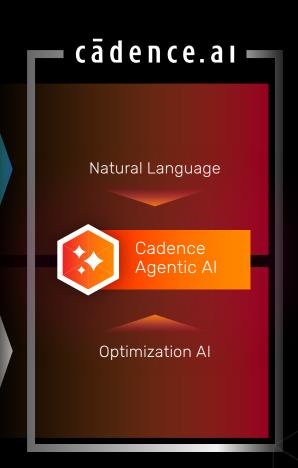

Cadence al

Chips-to-systems intelligent design acceleration

AGENTIC AI

Cadence OPTIMIZATION AGENTS

Verisium TM SimAl 10x

Verification Productivity

Al-driven automation and analysis for digital chip verification

Al-ENHANCED DESIGN ENGINES

Jasper™

| Design Type    | Speedup |

|----------------|---------|

| Modem IP       | 20X     |

| Mobile SoC     | 7X      |

| AI IP          | 8X      |

| AI IP          | 3X      |

| Memory IP      | 5X      |

| Base Station   | 18X     |

| NOC IP         | 5X      |

| Automotive SoC | 5X      |

| CPU IP         | 3X      |

| Network IP     | 4X      |

| CPU IP         | 9X      |

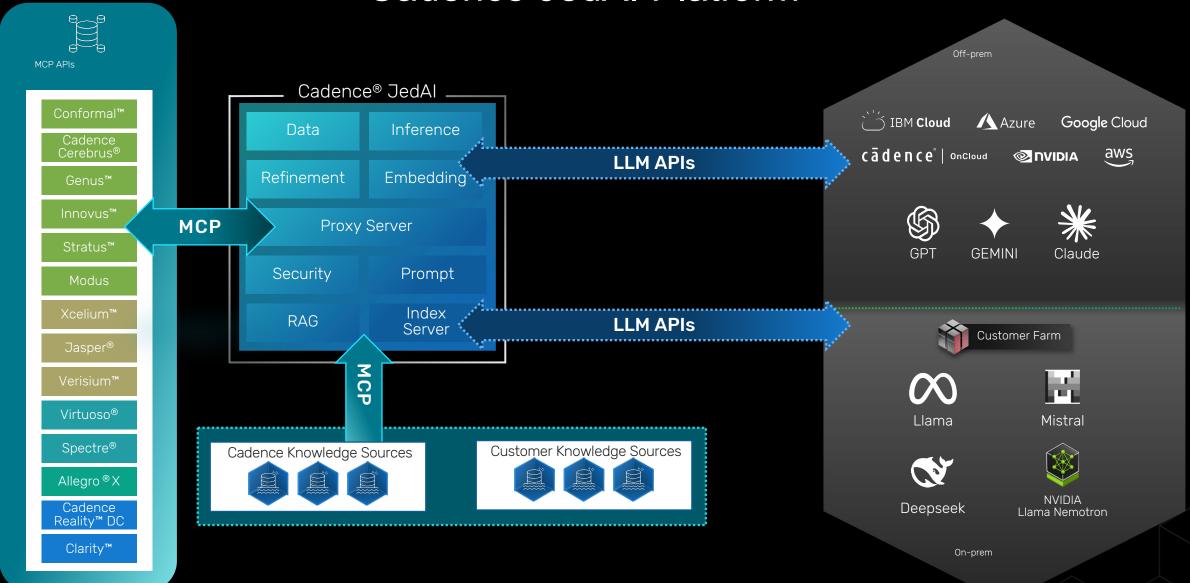

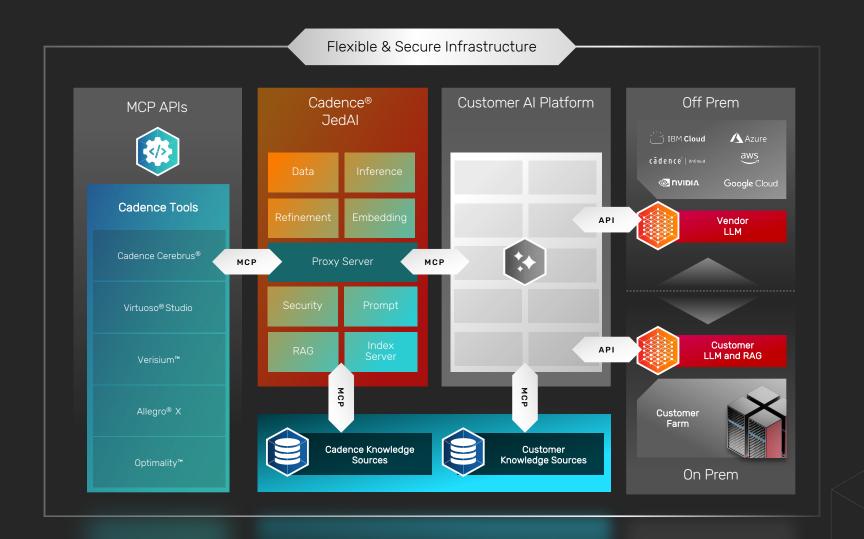

## Cadence JedAl Platform

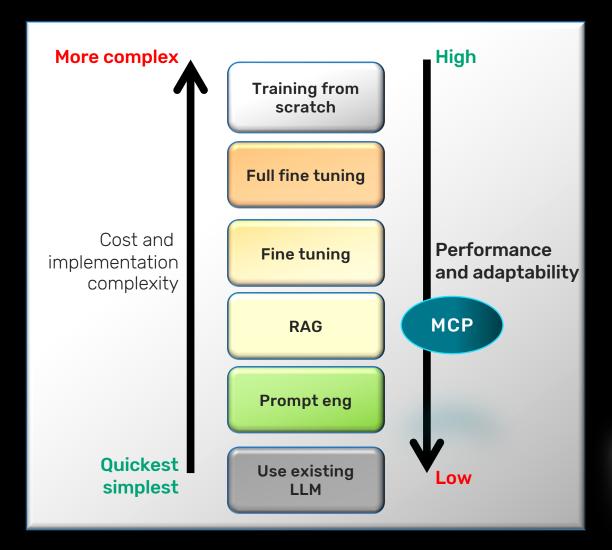

# The Deployment Dilemma

#### Complex Reasoning

#

## **Level 3 - Code Generation**

000

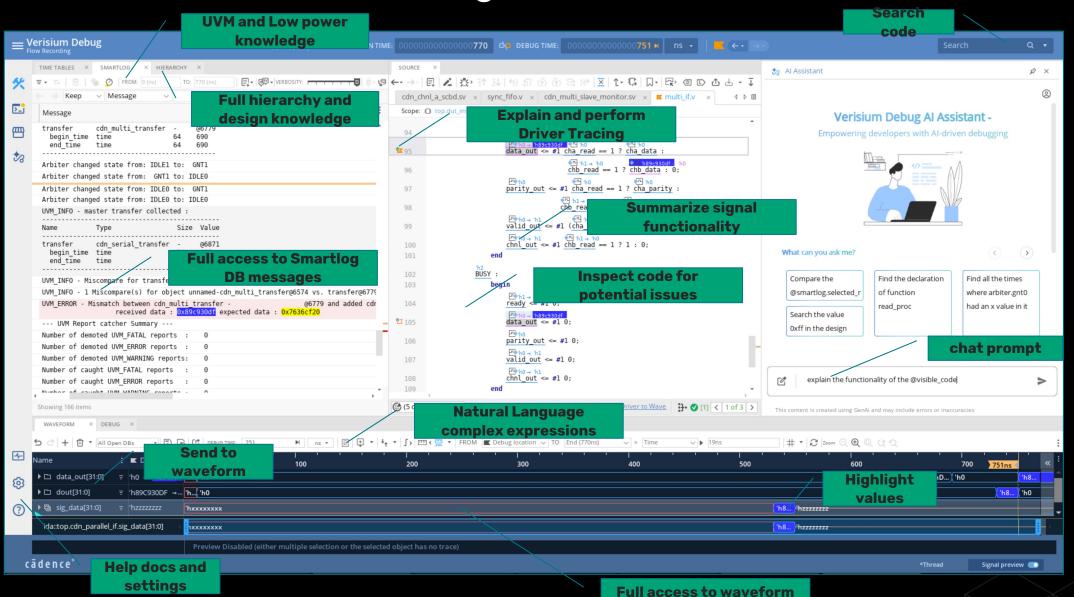

## vDebug Al Assistant

**DB** values

## The Agentic Al Investment Dilemma

SOURCE Reddit Dec 2024:

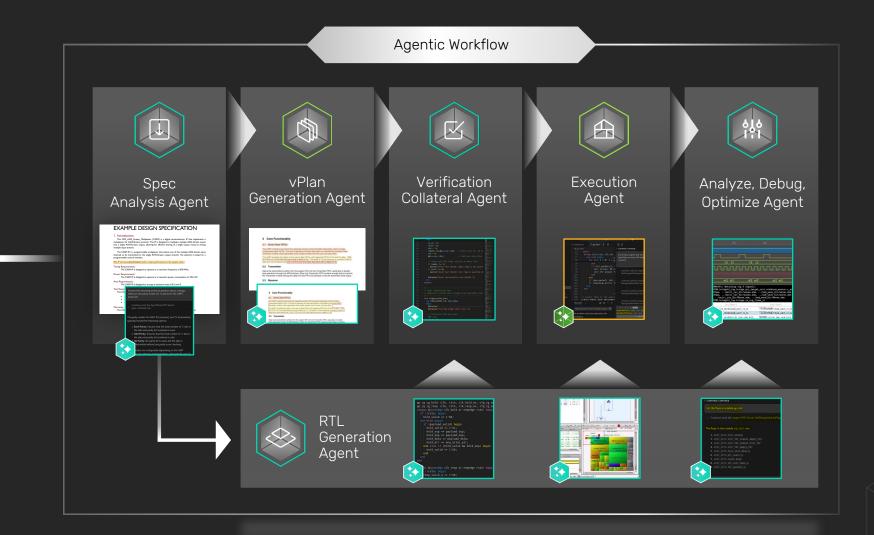

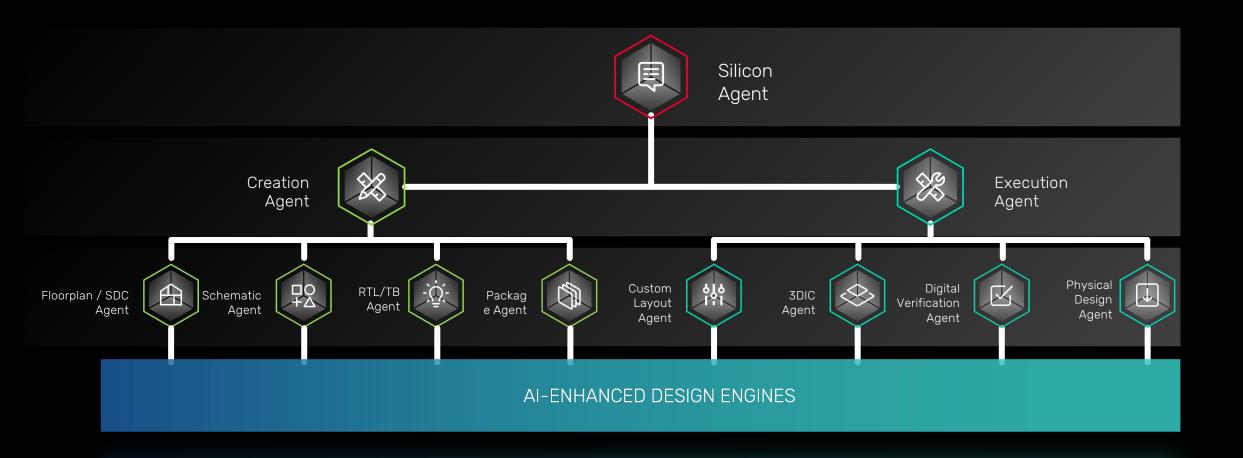

## Level 4 - Frontend Silicon Agent

Frontend Silicon Agent

From Spec to RTL Signoff

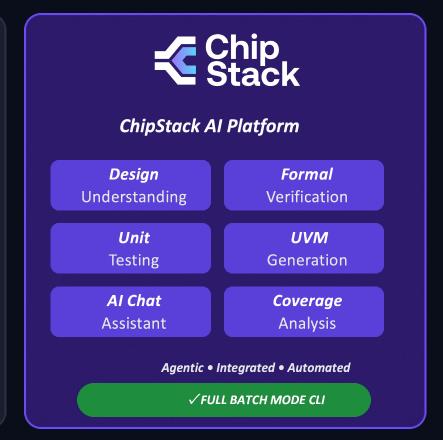

## Meet Chipstack: the World's First AI Verification Engineer

An army of Al junior verification engineers — integrated, production-ready

#### **Business Impact**

#### 10× Faster

Testbench and coverage generation

#### 60-80% Automation

Eliminates manual DV engineering tasks

#### **Production Ready**

Deployed at Qualcomm, battle-tested at scale

#### **Enterprise Security**

On-prem or cloud, your IP stays secure

#### From Design Understanding to Signoff — Fully Automated, Deeply Integrated

Reduce verification time by 10× • Scale your team instantly • Deploy in weeks, not months

ChipStack Confidential www.chipstack.ai

## System of Agents

## Challenges and Opportunities for Further Work

## Scaling complexity

- What works for a FIFO will not scale to real examples

- New reasoning models help close the gap

## Preventing auto-accept

- Easy to just click accept on whatever the AI provides

- How to keep the user involved in an active review

### Automated evaluation is hard

- Good benchmarks available for SVA generation

- Much harder for testbench generation

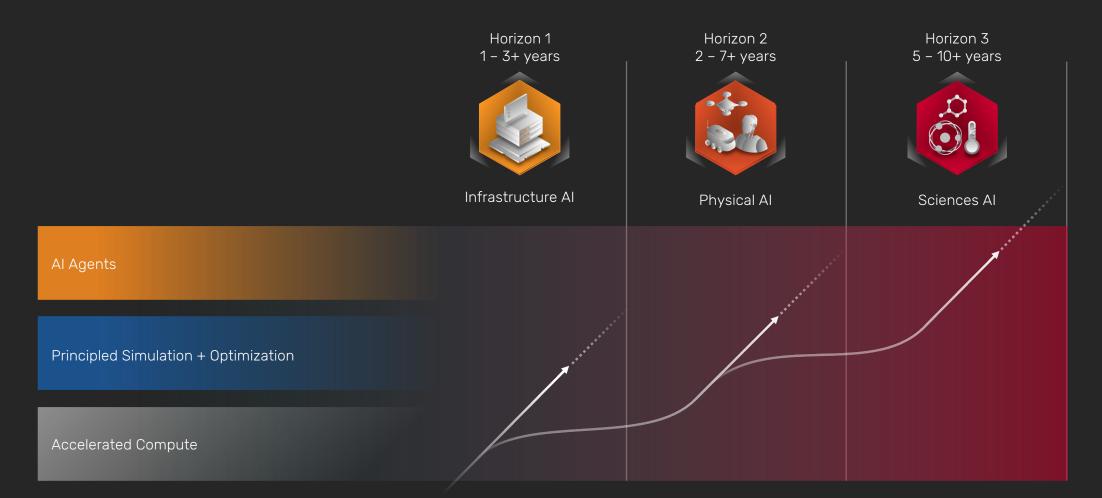

## Phases of Al Adoption

Silicon and System Volume and Complexity

## Design for AI and AI for Design

Al Agents

Principled Simulation + Optimization

Accelerated Compute

## Al Opportunities Are Endless