# Revolutionizing Verification With GenAl-Powered Automation A Paradigm Shift Towards Agentic Workflows

Dr Andy Penrose April 2025

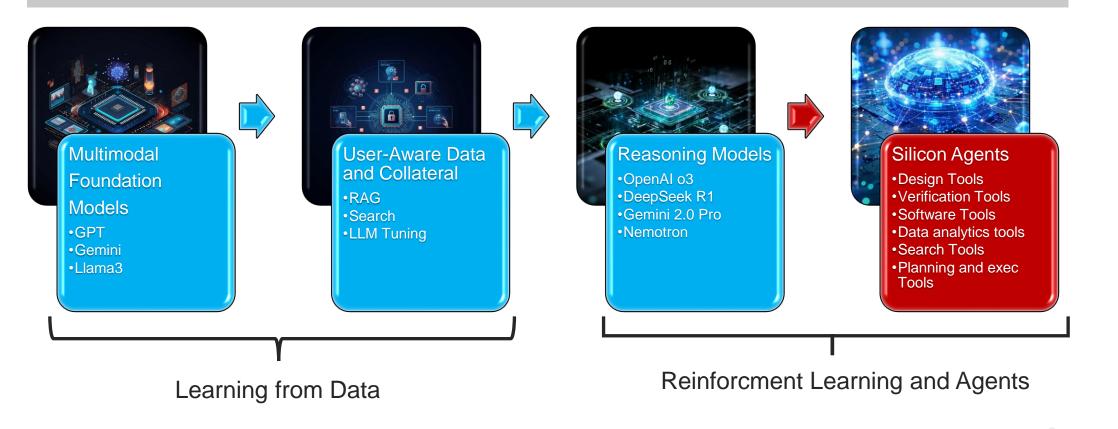

#### The Agentic AI Opportunity

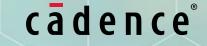

EDA 40-year History

Improving Productivity Through Design Abstraction

ADAPTIVE MESHING

MATRIX SOLVERS

NON-LINEAR SOLVERS

COMPUTATIONAL GEOMETRY

cādence

A new generation of

SAT SOLVERS

SYMBOLIC MODEL CHECKERS

#### **RTL Design Agent - Arbiter Design**

Arbiter: A design clocked with *clk* and reset *rst*, has four requesting agents, each able to request a shared resource using one bit of *req* signal. The *gnt* signal indicates which agent is currently authorized to use the resource. There is also an *opcode* input, allowing certain commands that override the normal behavior of the arbiter, such as forcing a particular agent to get priority or cutting off access to the resource, for a period of time. There is an *op\_error* output as well to signify that a bad opcode or illegal sequence of opcodes has been sent.

#### % j given this specification, generate a plan how to implement it in System Verilog

Below is a plan with a detailed logical sequence for a SystemVerilog implementation:

1. Define the top-level module and interface signals

- 2. Create an internal state machine

- 3. Normal arbitration logic

- 4. Opcode processing

- 5. Timing and separation of control

- 6. Error mechanism

- 7. Integration and verification

Feel free to ask for further details or help with coding specific parts of the module!

% Senerate SystemVerilog module interface definition using parameters

#### Below is an example SystemVerilog interface definition for the given arbiter design: module arbiter#( Draw top level schematics - **1** parameter int WIDTH = 4, // Number of request/grant lines // The index of the highest priority request (0 is highest) parameter int HIGH PRIORITY INDEX = 0 input logic clk. // active high reset input logic rst, // Arbiter interface gnt[3:0] req[3:0] // request signals vector input logic [WIDTH-1:0] req, arbiter // grant signals vector (one-hot encoded) clk output logic [WIDTH-1:0] gnt, valid op // Opcode processing interface rst input logic [7:0] opcode, // 8-bit opcode input op error opcode // asserted when an allowed opcode is received output logic valid op, // asserted when an illegal opcode is detected output logic op error cādence

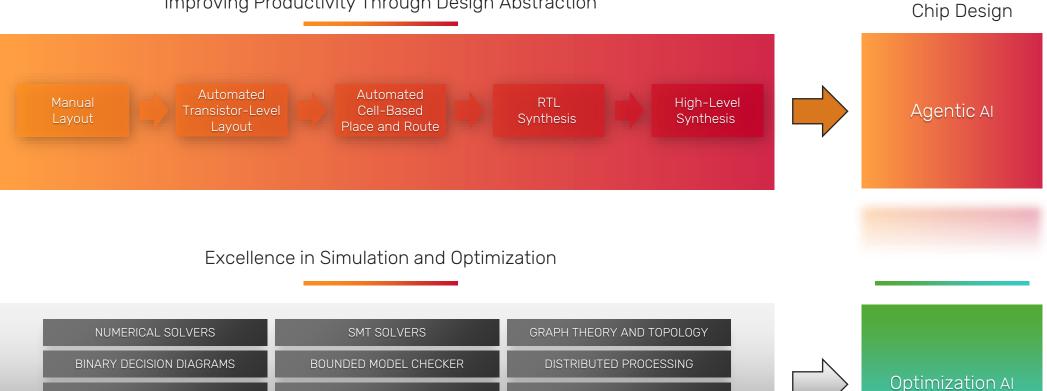

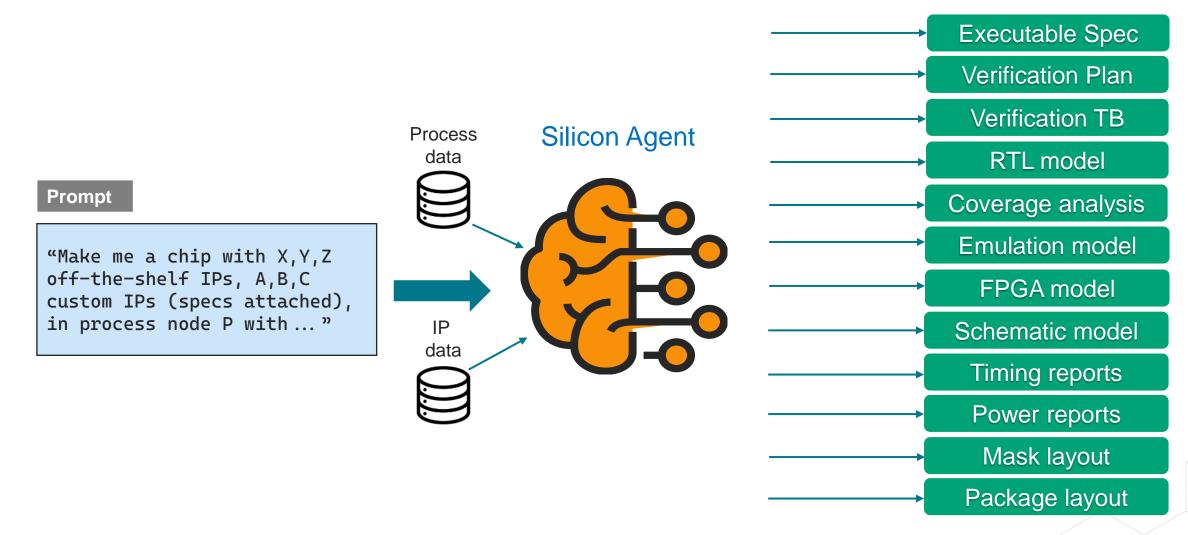

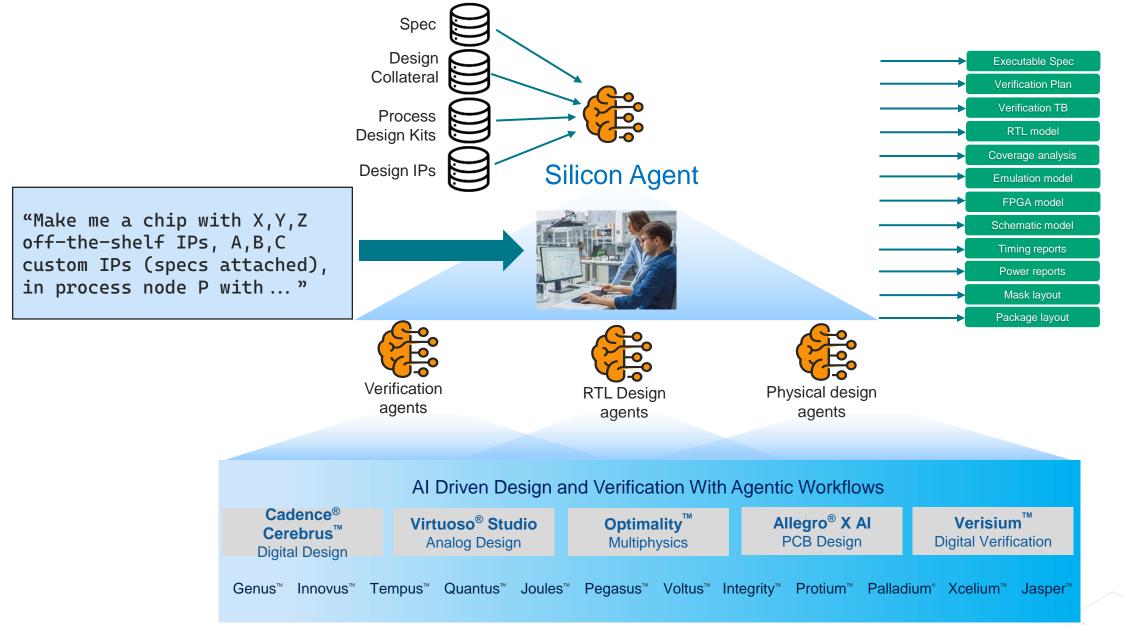

# New EDA Vision: Silicon Agents for Chip Design

Leverage Artificial Intelligence technologies to seamlessly integrate with Cadence's Al-optimized software, hardware, and IP for creating data-driven Agentic Workflows and Silicon Agents

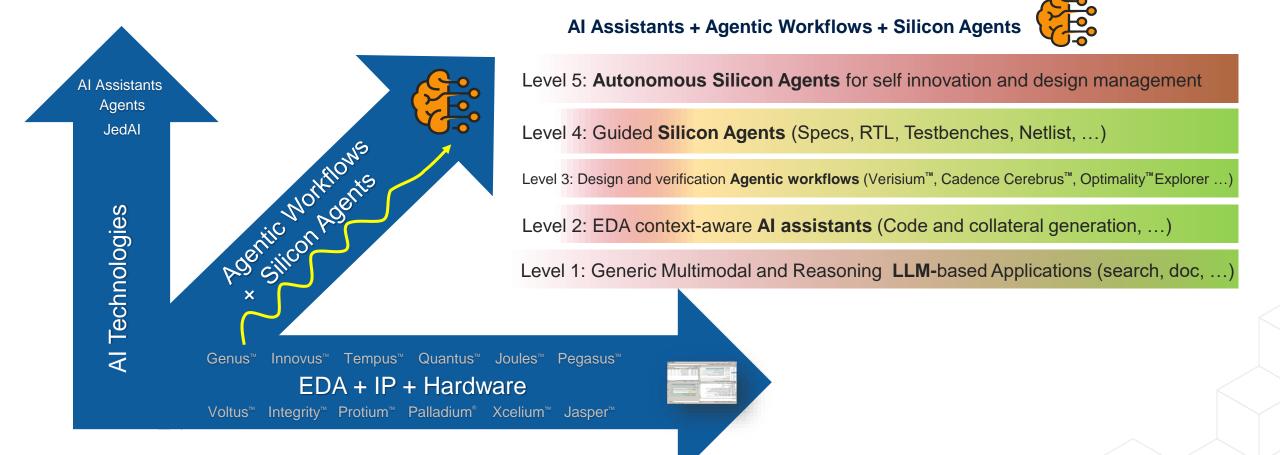

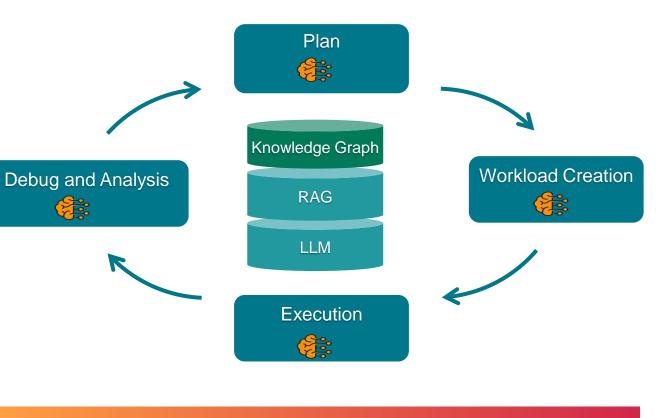

#### What Does "Agentic AI" Mean?

Autonomious and Competenece-Aware AI Software

**Plan**: understand its goals within a context and create or adapt an execution plan of single or multistep tasks to ensure successful goal attainment in dynamic conditions

**Execute**: dynamically and independently takes decisions to allocate resources, execute tasks, and possibly pass control to other agents

**Evaluate**: incrementally evaluates results against plan and context and streams out results

Cadence<sup>®</sup> JedAI Data and AI platform + AI Assistants

#### What Does "Agentic Workflow" Mean?

- Agentic AI technologies in traditional workflow tasks

- Integrated with AI Assistants

- Deterministic flow designed by experts, retaining the same methodology

- Aiming for productivity boost and better execution goals (PPA)

- Combining LLMs, AI Assistants, and guided AI Agents in selected tasks

Cadence<sup>®</sup> JedAI Data and AI platform + AI Assistants

### What Does "Silicon Agent" Mean ?

Al Agent for Chip Design

#### Silicon Agent – Assisted by a Hierarchy of Domain-Specific Agents

#### **Capabilities Pipeline and Agentic Platform**

Agentic Workflows and Silicon Agents

Cadence<sup>®</sup> JedAl Agentic Al Framework

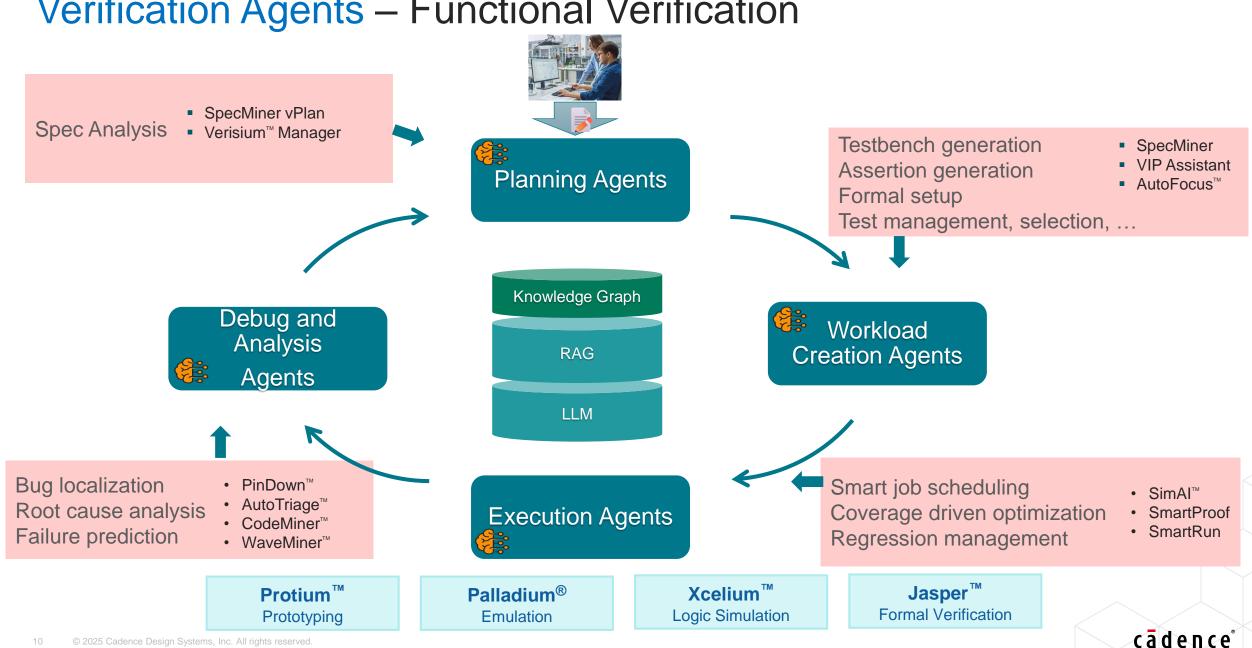

#### **Verification Agents** – Functional Verification

© 2025 Cadence Design Systems, Inc. All rights reserved.

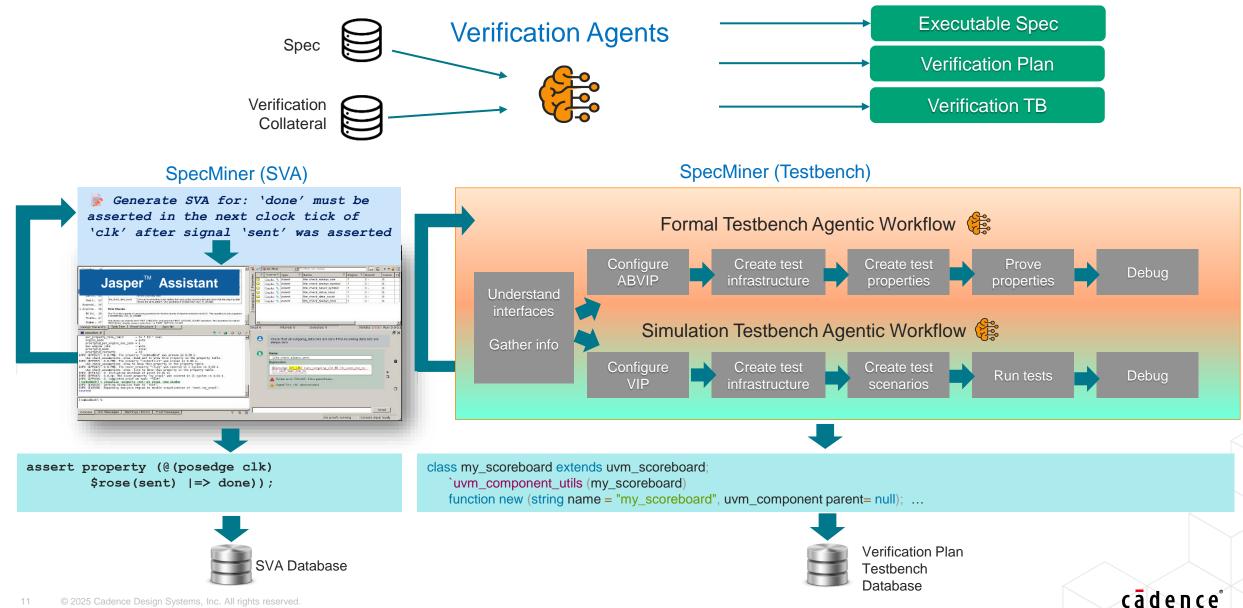

#### **SpecMiner**– Spec Analysis, Verification Plan, Testbench Gen

# cādence

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>https://www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.