# Modelling a 4-Level DCDC Converter Using EEnets

Paul Denny

Confidential. Copyright ©2025 pSemi Corporation. All rights reserved.

## Contents

- What is a Multi-level DCDC Converter

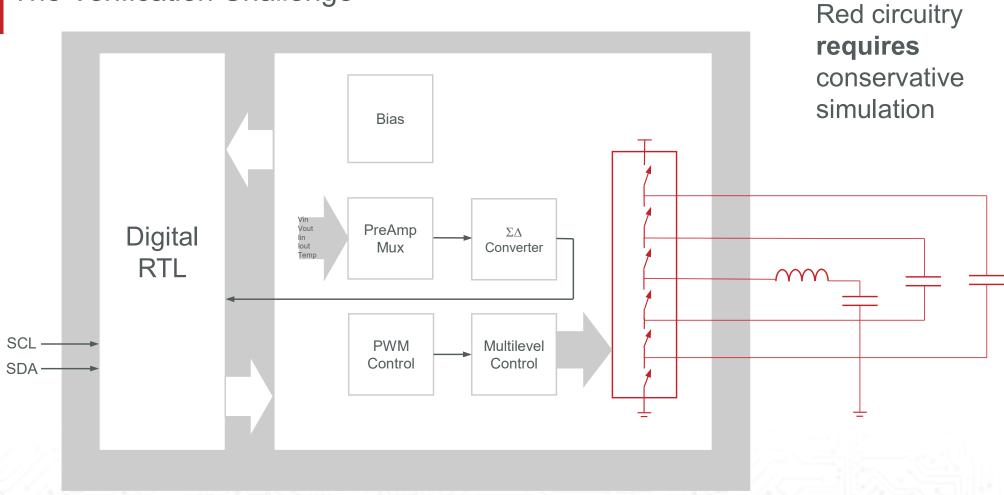

- The Verification Challenge

- Limitations of Traditional Modelling methodologies

- What are EEnet models?

- Accuracy of EEnet methodology

- Speed of EEnet methodology

- Pros and Cons

- Q&A

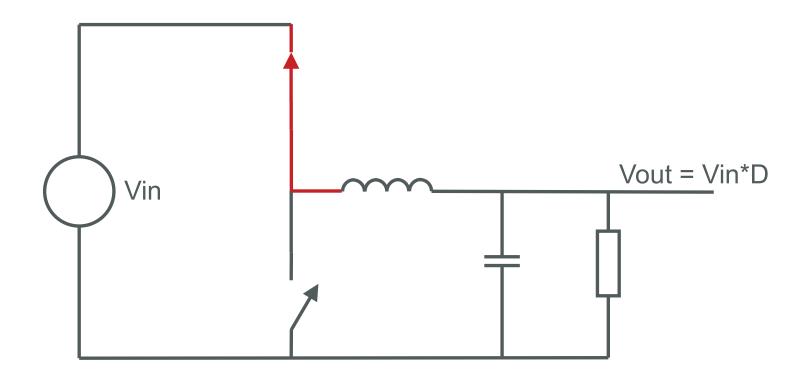

# Basic Buck Converter Output Stage

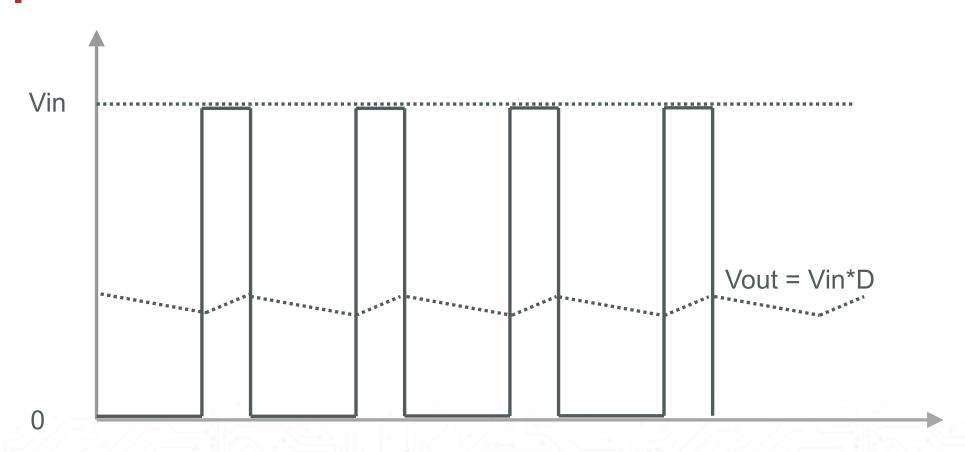

# Basic Buck Converter Output Switching Waveform

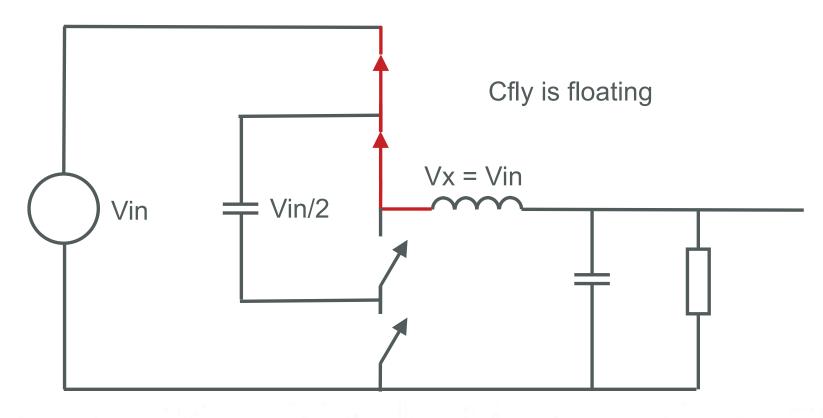

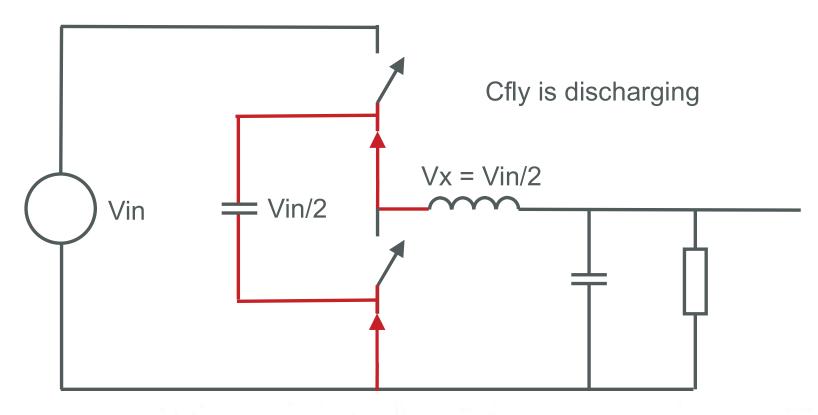

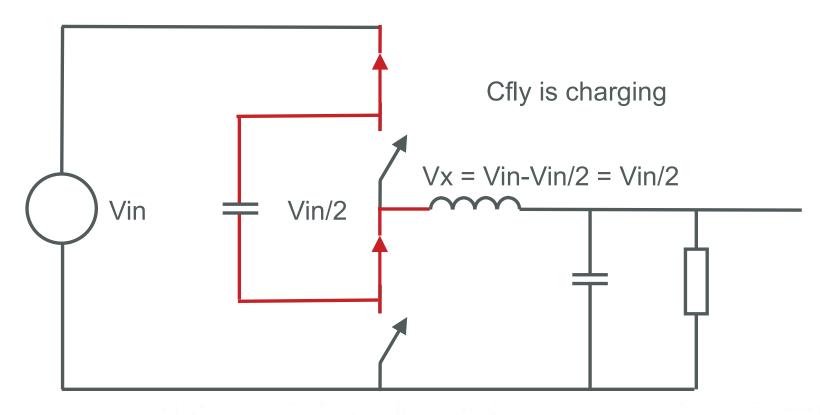

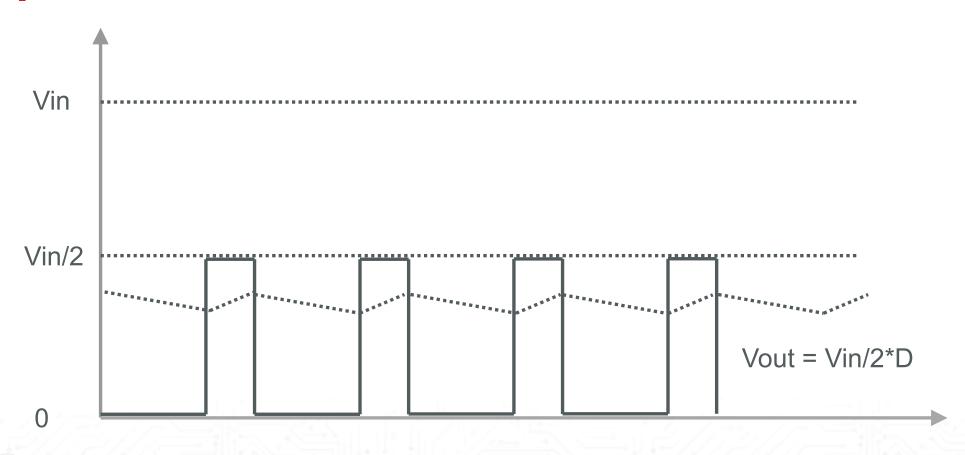

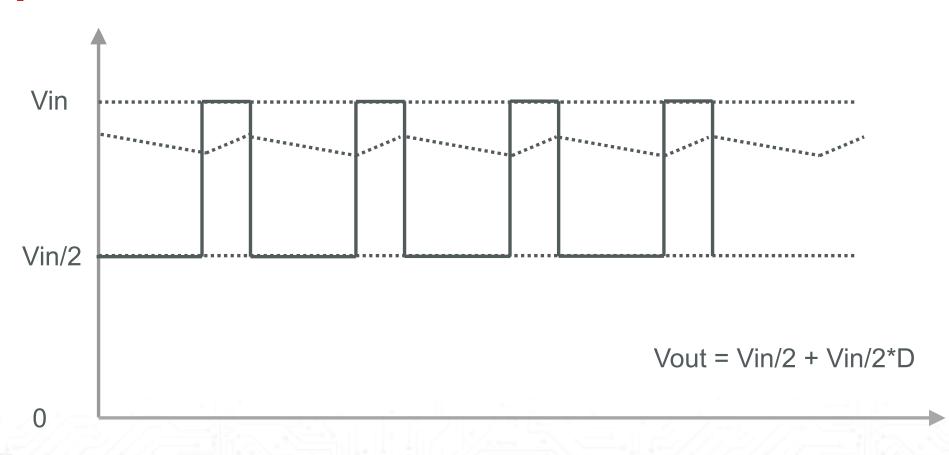

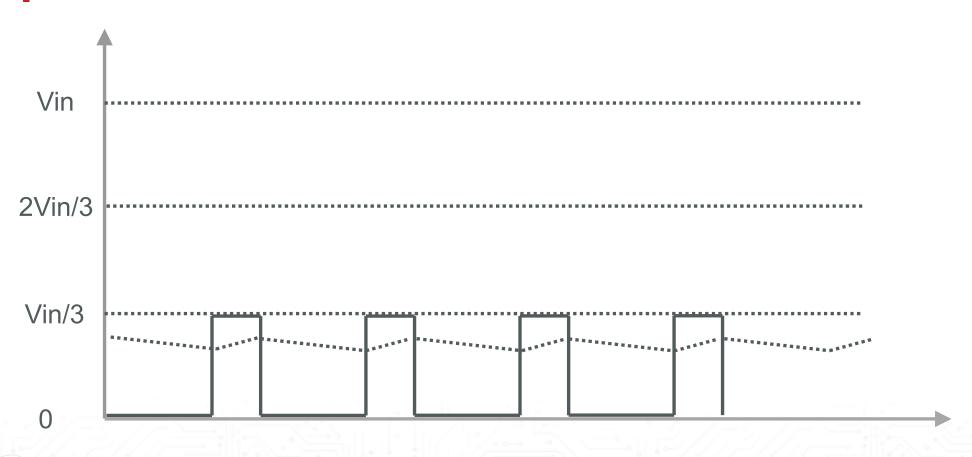

# 3 Level Converter Output Switching Waveforms

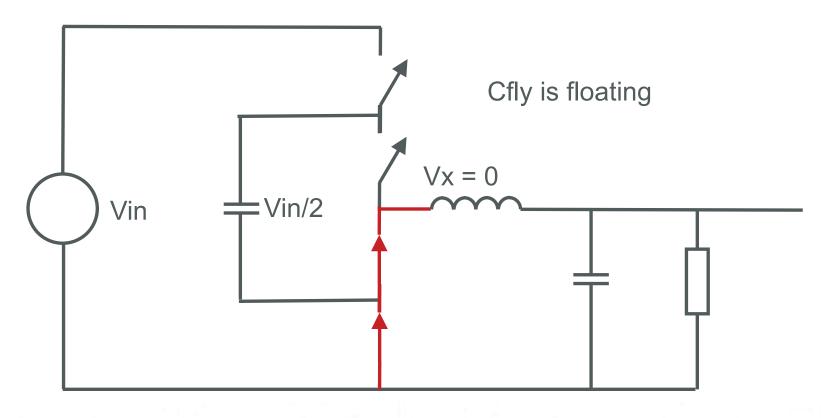

# 3 Level Converter Output Switching Waveforms

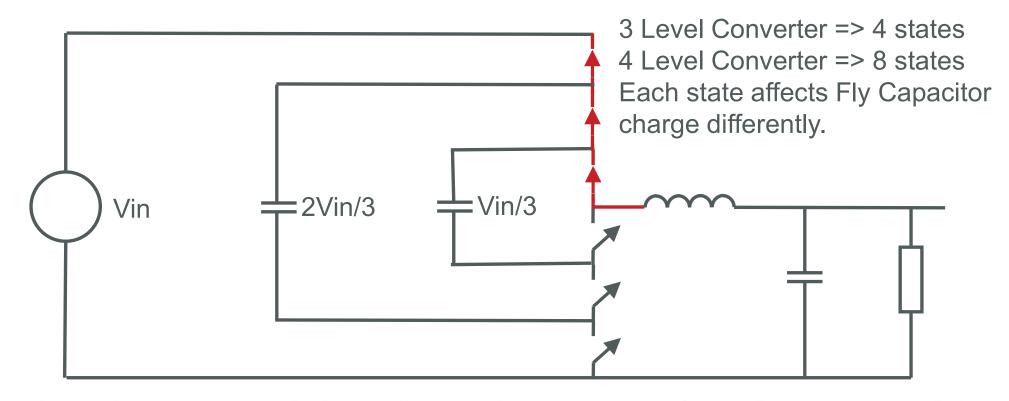

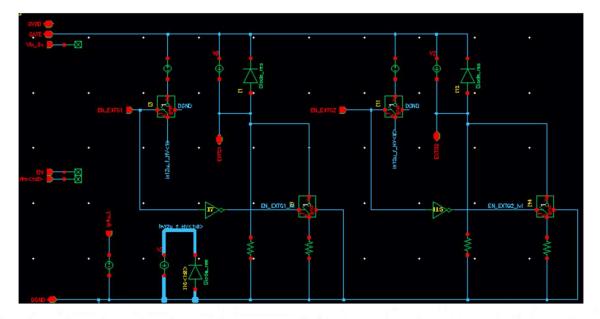

# 4 Level Buck Converter

## The Verification Challenge

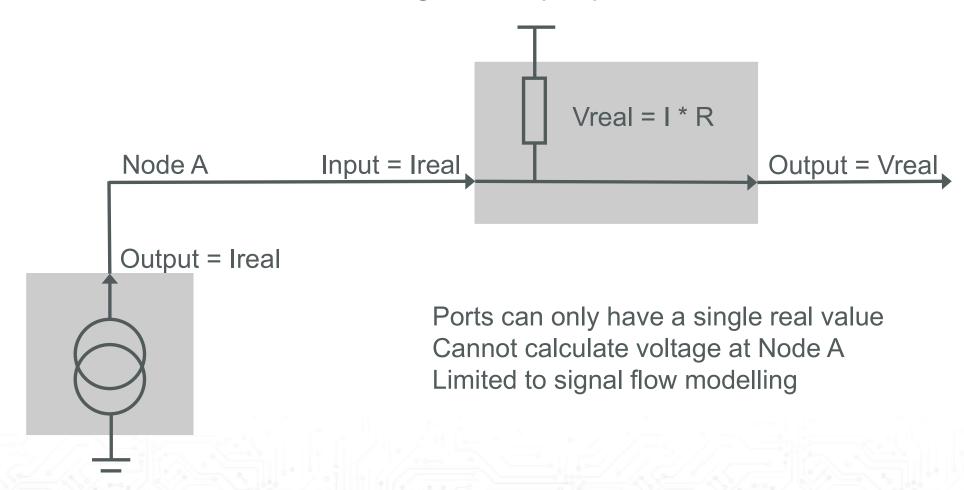

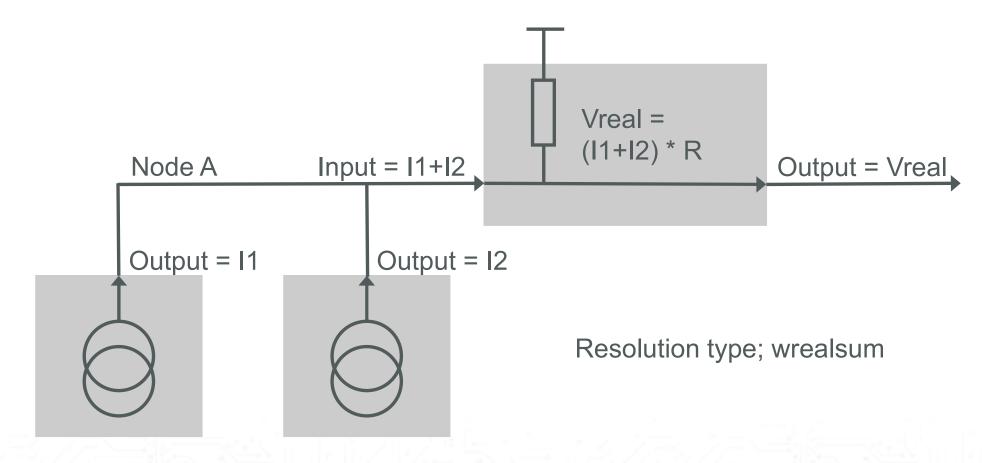

#### Limitations of WREAL models – single value per port

#### Limitations of WREAL models – limited resolution functions

## What are EEnet models?

- EEnets employ SystemVerilog language features;

- User Defined Types (UDT)

- User Defined Nets (UDN)

- User Defined Resolution Functions (UDR)

## SystemVerilog UDN and UDR

- Integral part of SV language definition

- User Defined Nets (UDN)

- Allow any number of independent variables to be assigned to a port

- real

- logic

- Int

- User Defined Resolution Functions (UDR)

- Allow any function to resolve multiple drivers on net

## What are EEnet models?

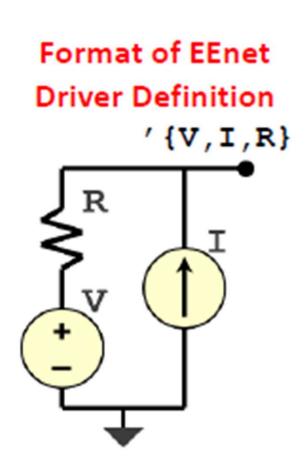

```

User (Cadence) Defined Type (UDT)

typedef struct {

real V;

real I;

real R;

} EEstruct;

```

- User Defined Resolution Function (UDR)

function automatic Eestruct res\_EE (input Eestruct

driver[]);

<lots of function code here>

- User Defined Net (UDN)

nettype EEstruct EEnet with res EE;

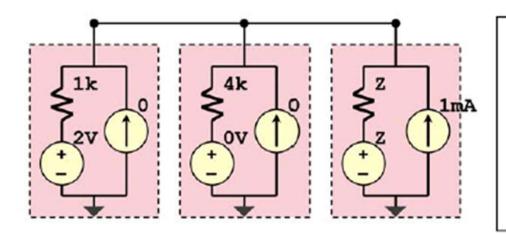

## EEnet Resolution Function

#### **Output Evaluation:**

$\Sigma I = 2mA + 0mA + 1mA = 3mA$

$\Sigma G = 1m + 0.25m + 0 = 1.25m$

Vout =  $\Sigma I / \Sigma G = 3m/1.25m = 2.4V$

Rout =  $1/\Sigma G = 800 \Omega$

Resulting EEnet value: '{2.4, 0, 800}

• Acknowledgement – Reproduced from Cadence's EEnet Rapid Adoption Kit

## What about Capacitors?

```

V = Integ(I * dT) / C

V1 = V0 + ((I0 + I1)/2 * dT) / C

```

- V1 = [V0 + I0 \* dT/2C] + [I1 \* dT/2C]

- V1 = [ Veq ] + [I1 \* Req]

- This simple difference equation fits directly into the EEnet driver model

- Similar arithmetic allows for Inductors

- NB this provides an exact solution equivalent to Spice

- Need to provide suitable internal event clock

### **EEnet Library**

- Library is included in Cadence installation

- Models are pre-written and include advanced modelling features

- Convergence limits

- Automatic timestep control

- Floating (differential) components

- Covers vast majority of analog modelling needs

- Greatly eases adoption

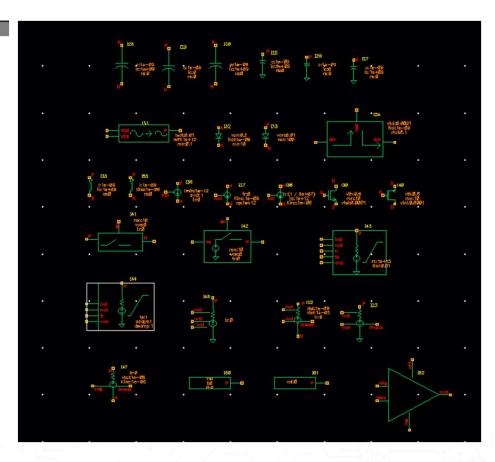

## EEnet Simulation Speed

- Extremely fast ~2000x in like-for-like comparison

- Top level SOC simulation in minutes, not days

```

module GateDriveSW_mirr_ES7

import EE_pkg::*; import cds_rnm_pkg::*;

( DGND, DVDD, EXTG1, EXTG2, GATE, in4u_f, EN_EXTG1,

EN_EXTG2, ip4u_t, PSUB, EN, Vin_5v, Itrim );

input logic EN_EXTG2;

inout EEnet DGND;

input logic EN_EXTG1;

input logic EN;

inout EEnet PSUB

inout logic EXTG2;

input real Vin_5v;

input real ip4u_t;

inout EEnet GATE;

inout EEnet DVDD;

input logic [1:0] Itrim;

inout wreal4state in4u f;

inout logic EXTG1;

/ Shorthand for standard real constants:

define Z 'wrealZState

define X `wrealXState

parameter real R4 = 2.0e3;

parameter real R1 = 1.0e6;

parameter real R0 = 49.1;

parameter real R5 = 2.0e3;

parameter real R3 = 1.0e6;

parameter real R2 = 49.1;

assign EXTG1 = ((real'(EN_EXTG1) * (GATE.V - (iref * R4))) > ((DVDD.V - DGND.V) / 2)) ? 1 : 0;

assign EXTG2 = ((real'(EN_EXTG2) * (GATE.V - (iref * R5))) > ((DVDD.V - DGND.V) / 2)) ? 1 : 0;

always @*

case(Itrim)

2'b00: iref = real'(EN) * ip4u t * (6/8) * 4;

2'b01: iref = real'(EN) * ip4u_t * (6/4) * 4;

2'b10: iref = real'(EN) * ip4u_t * (6/16) * 4;

2'b11: iref = real'(EN) * ip4u_t * (6/12) * 4;

default: iref = 0;

function real max(input real a,b); max = (a>b) ? a : b;

endfunction

```

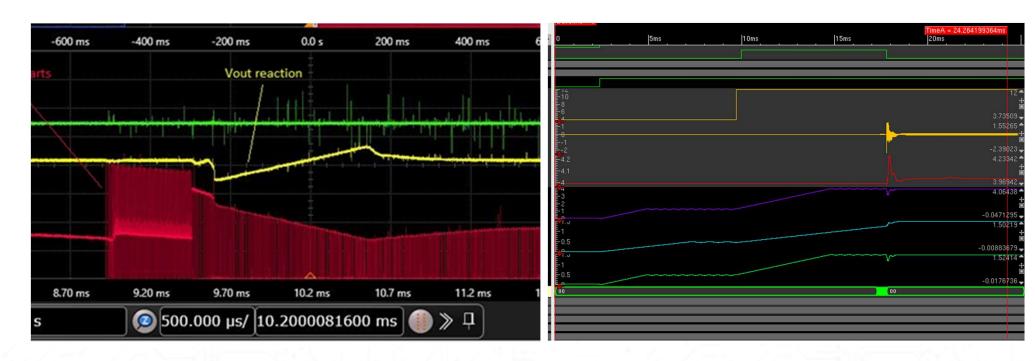

## Accuracy of EEnet methodology

- Extremely accurate modelling of behaviour

- Allows high confidence in algorithms, system stability and functionality

# Pros and Cons

| Advantages                                           | Challenges                                                             |

|------------------------------------------------------|------------------------------------------------------------------------|

| Very Accurate – SPICE level accuracy possible        | Requires expert modelling ability (timesteps, convergence)             |

| Very wide range of abstraction possible              | Verification engineer must straddle<br>Analog and Digital domains      |

| Extremely Fast System Simulation Speeds              | Project team and database must be managed as Top Down - Digital on Top |

| Only requires single simulation kernel (and license) | Who to lead methodology in mixed signal team                           |

## **THANK YOU**

www.psemi.com

Q&A

25