## Use of Prototyping & Emulation in the Semiconductor Industry in 2025

Michael O' Sullivan, Cadence 1<sup>st</sup> July 2025

## Cadence

An AI Computational Software Leader

**OUR MISSION** is to innovate technology and productivity solutions for an Al-enabled world

**OUR SOLUTIONS** enable engineers and scientists to bring innovative new products to life

Hyperscale Data Centers and Communications

Transportation, Robotics, and Machines

> Al-Enabled Sciences

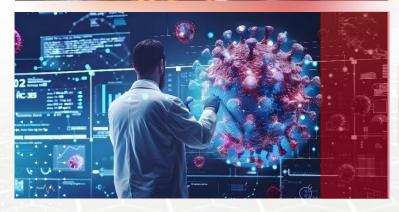

## Cadence at a Glance

An AI Computational Software Leader

## Agenda

- Use of emulation/prototyping in the semiconductor industry

- Cadence platforms for emulation/prototyping

- Summary

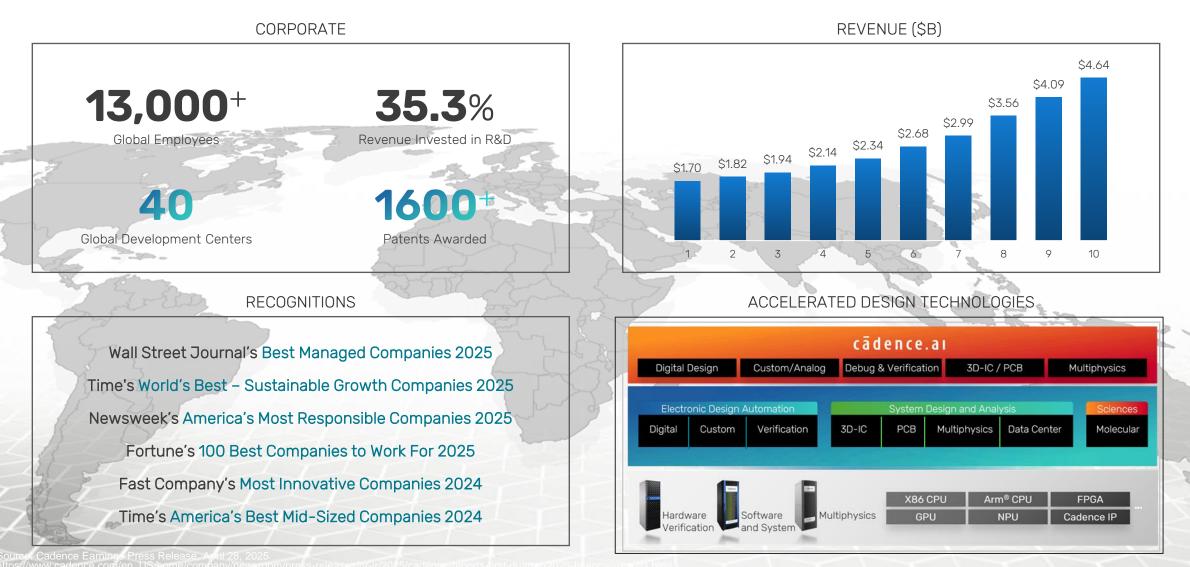

## Software Verification Challenge

75%+ project costs in software and verification

IBS July 2022

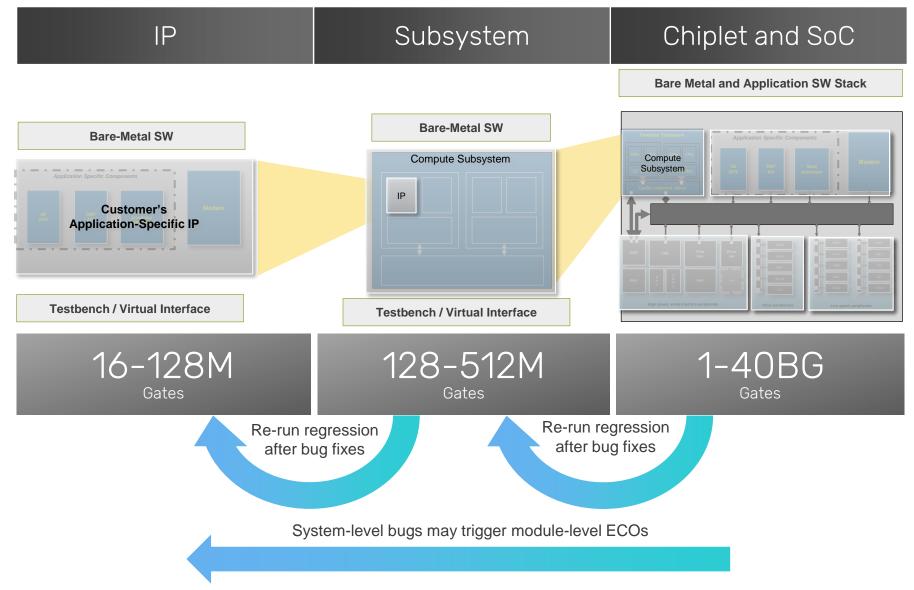

## Verification for Different Sizes of Payloads

6 © 2025 Cadence Design Systems, Inc. All rights reserved.

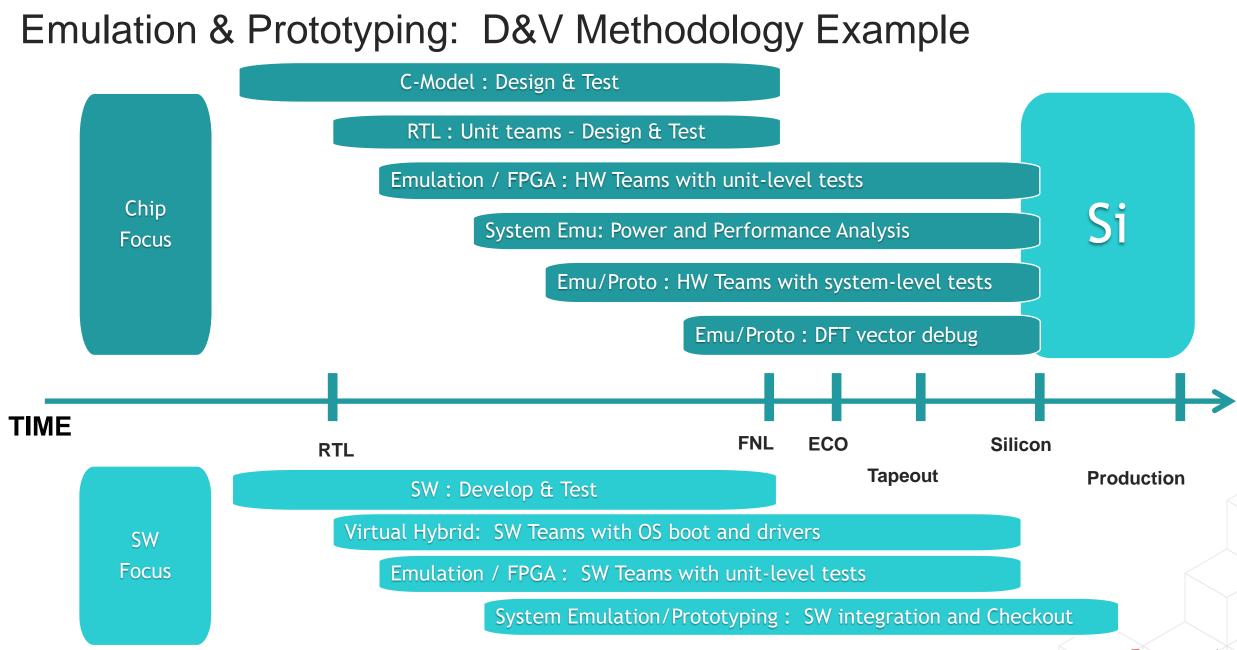

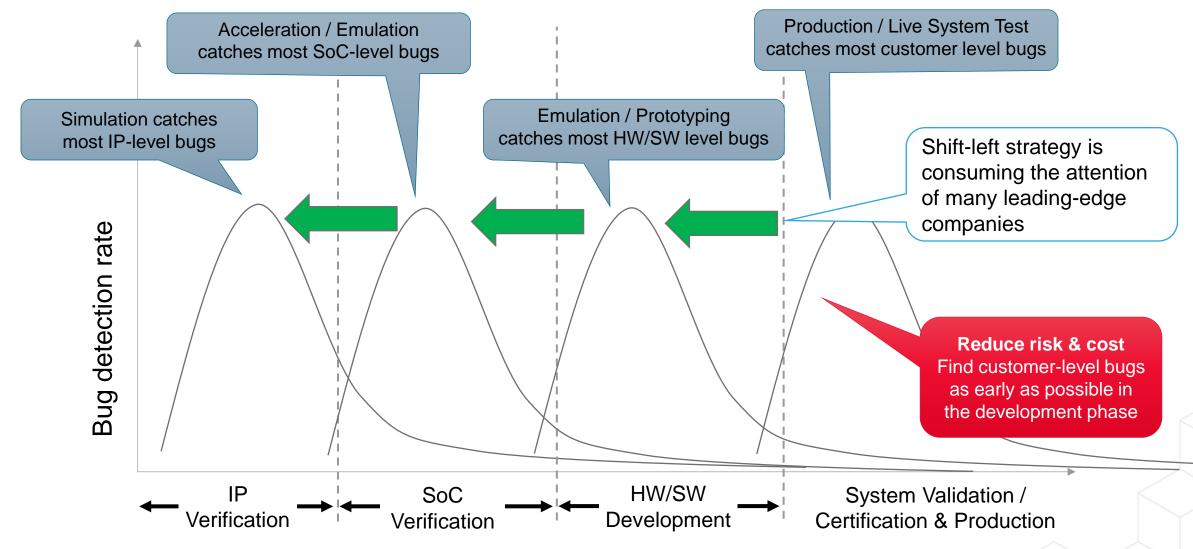

#### Challenge: more silicon and system development in less time Bug detection still not as early as possible

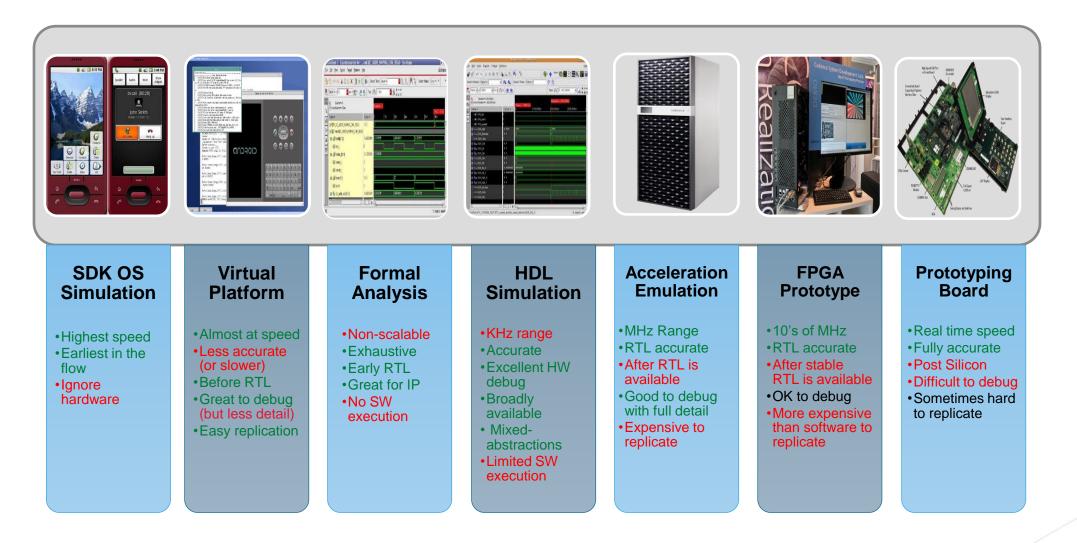

## There is no "One Size Fits All"

Verification and software platforms need to interoperate

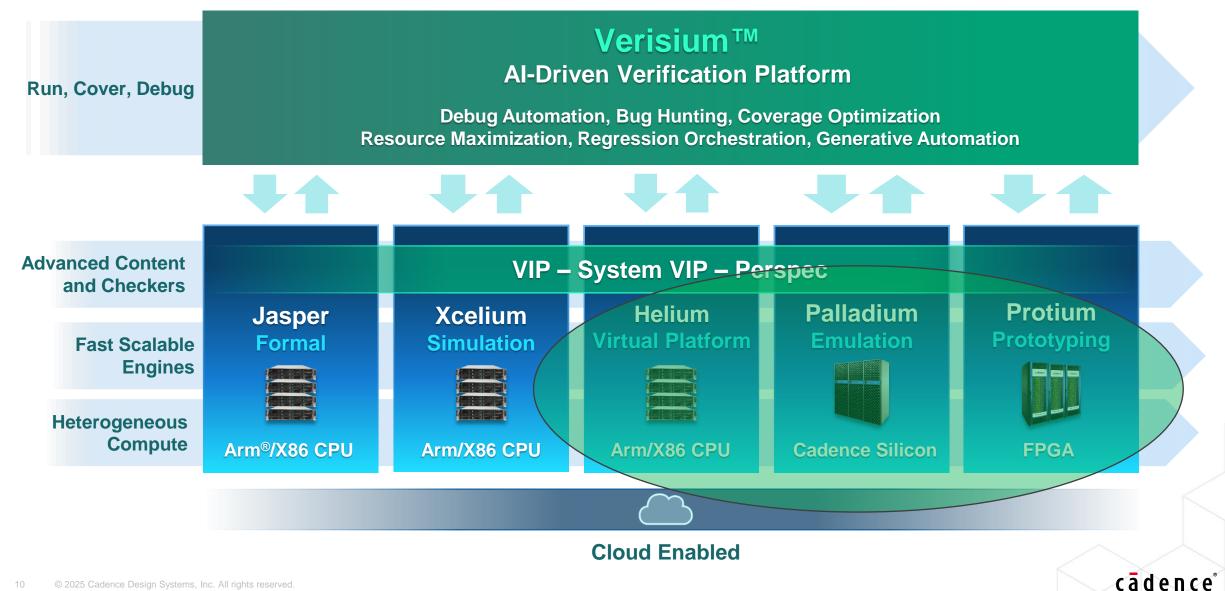

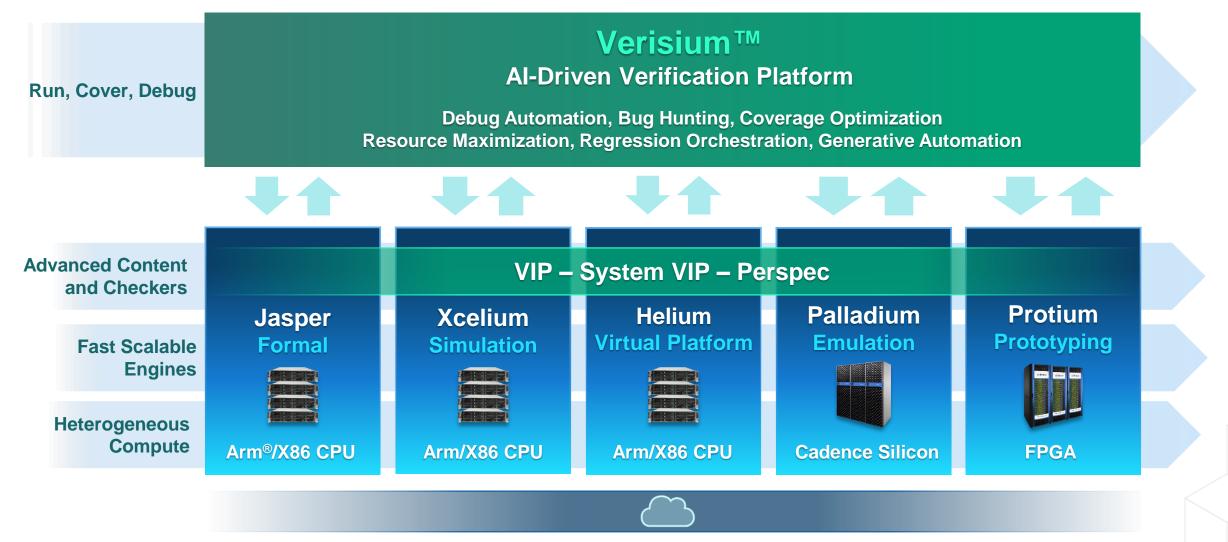

## Cadence AI-Driven Verification Full Flow

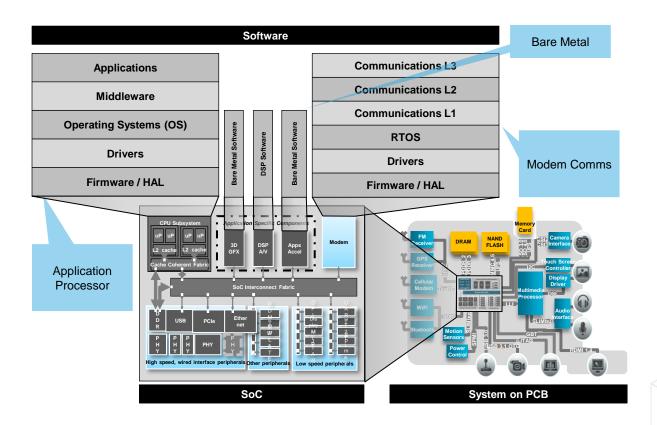

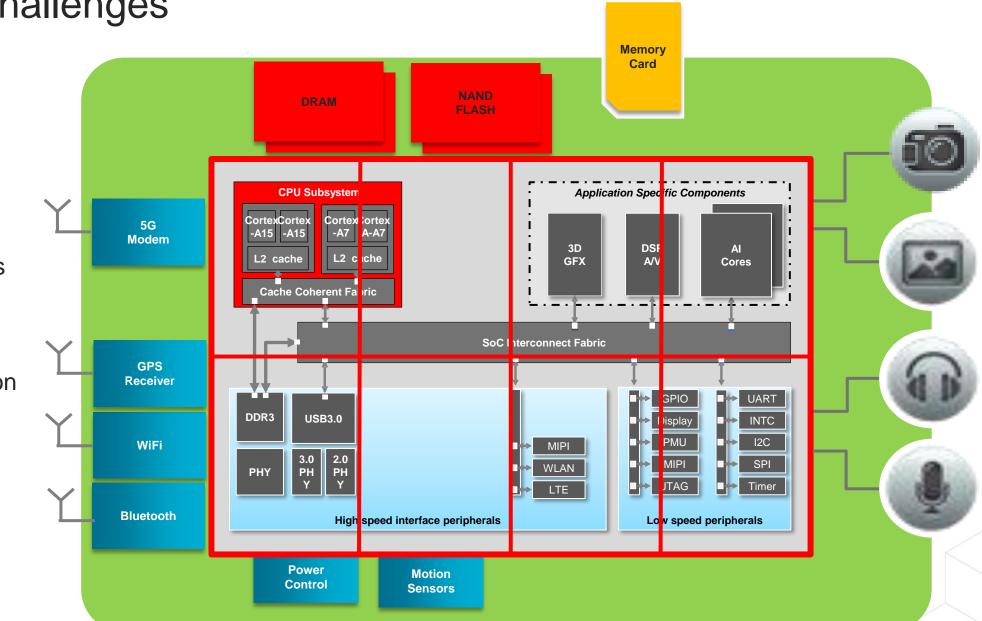

## System and Chip Design Trends

#### **Business challenges**

- Time-to-market

- Development cost reduction

#### Technical challenges

- Multi-core design and verification complexity

- Integration of new IP, subsystems in derivatives

- Software stack development and bring-up

- Hardware-software convergence

- More than 60% of effort in software

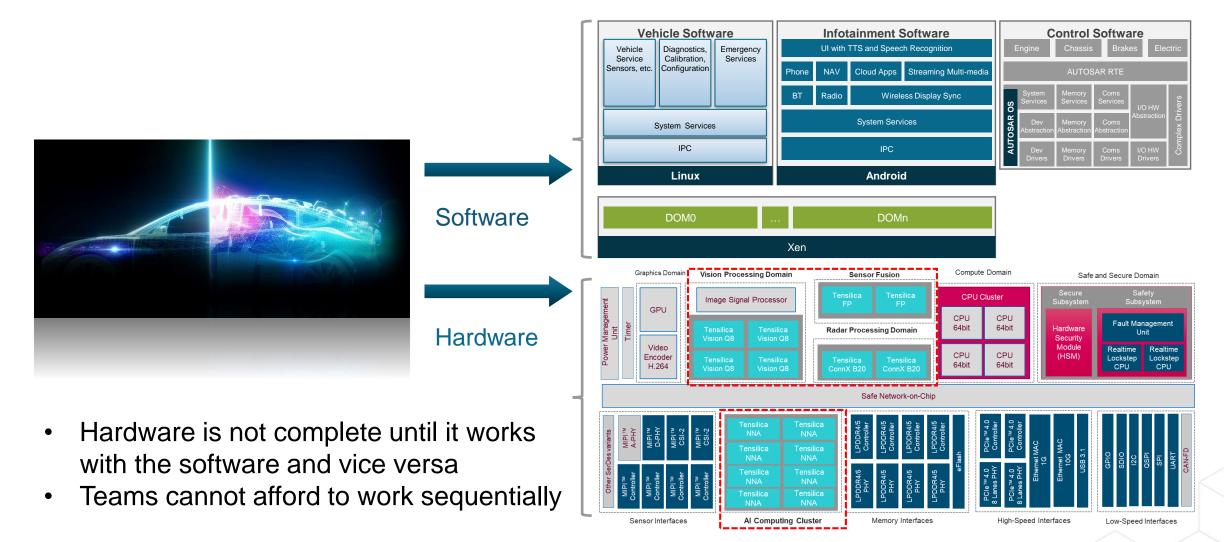

## **Design Trends Practical Result**

Formerly separate projects must converge, software is a fundamental component

Color coding:

Cadence

Services I

3rd-Party IP

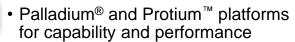

## **Cadence Helium Digital Verification Process**

#### Virtual Platforms

- Software development and verification *in parallel with* hardware development and verification

- Validated software simplifies verification

#### Hybrid Platforms

- Software development and verification *foundationally integrated with* hardware development and verification

- Start both before either are complete

- Accuracy and speed where you need them

#### Virtual Platforms Transforming software development

Controllability, Observability, Repeatability

#### Instruction Accurate

Target software runs without changes

- Full programmers view

- Memory, registers, and interrupts

Fast enough for OS Boot

Available Early

6-12 months before silicon

All in Software

Run on standard x86 workstations

## Hybrid Platforms

Transforming software-driven verification

#### Mixed Accuracy

• RTL for DUT

• TLM for context

Full Programmers' ViewMemory, registers, interrupts, and pins

#### Mixed Abstraction

- Fast enough for OS Boot

- Detailed enough verification

#### Available Early

• As soon as the DUT is ready

#### Integrated with Hardware

#### Balance of Speed and Accuracy

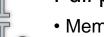

## Helium Virtual and Hybrid Studio

The key to a flow that connects verification and software together

## Helium<sup>™</sup>

#### Cadence + VLAB Works

105 (D\*)

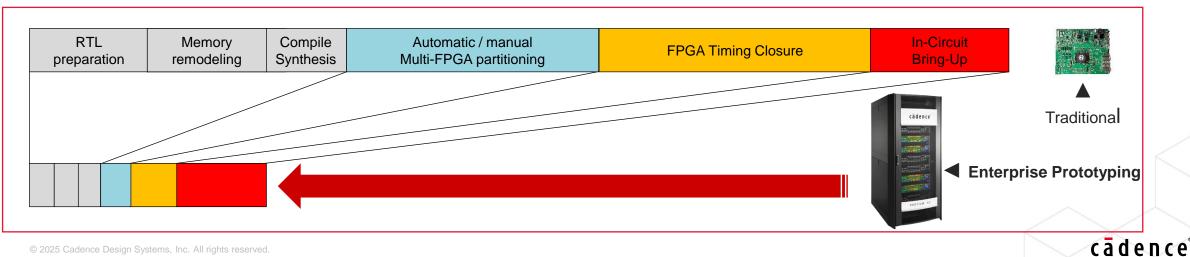

## Prototyping challenges

- Mapping ASIC clocking into FPGAs (RTL changes)

- Mapping ASIC memories into FPGAs (RTL changes)

- Interfaces that require speed-adaption (RTL changes)

- Design > 40MG (FPGAs partitioning)

- Debug HW+SW (Tools support)

## So ... Traditional prototyping is not suitable anymore

- Too many gates

- Too much memory

- Too many peripherals

- Too much software

- Not enough time

. . .

Needs to be remotely accessible

#### And That Brings Us To Enterprise Prototyping ... Addressing Those Challenges!!!

Compiler Automation takes the pain away from mapping to FPGA

- Takes ASIC RTL and with little or no modification maps it into FPGAs

- Clocks, Memories

- Fully automatic, multi-FPGA partitioning 0

- FPGA timing closure 0

- Fully integrated FPGA PnR 0

- Speed Bridges, Virtual Bridges, Memory models

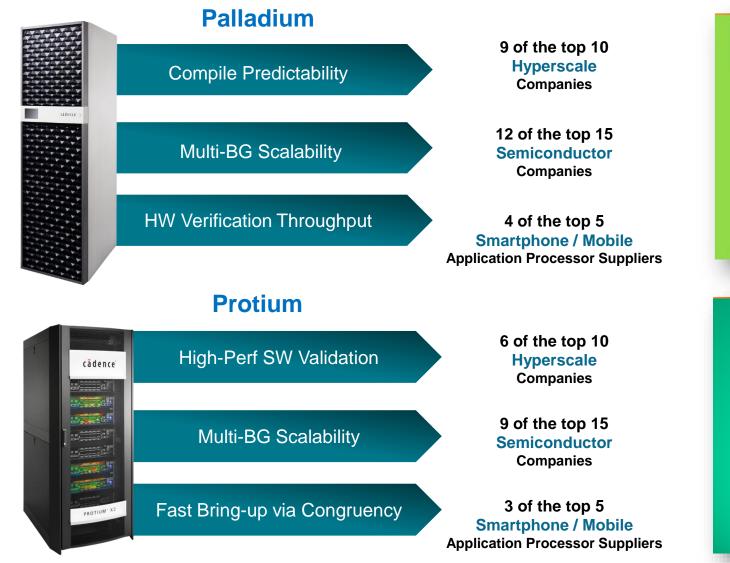

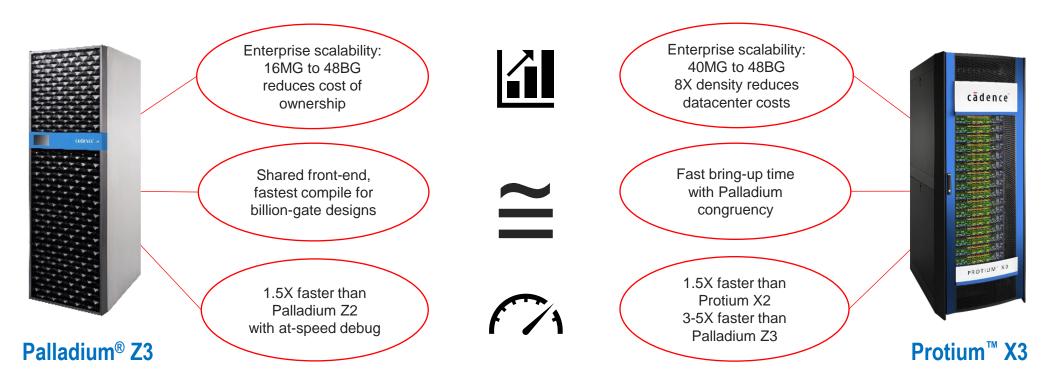

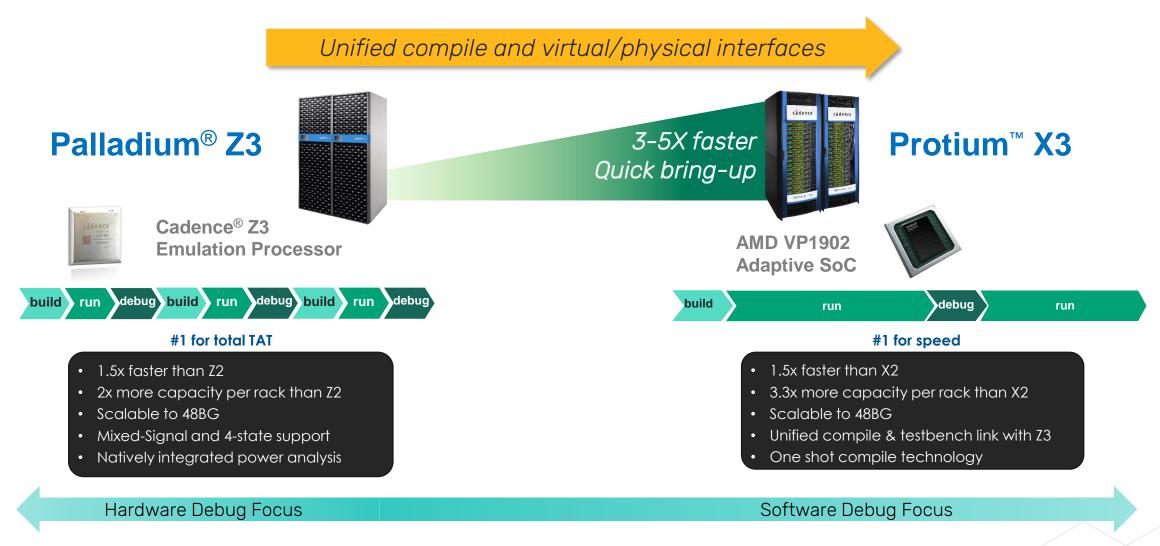

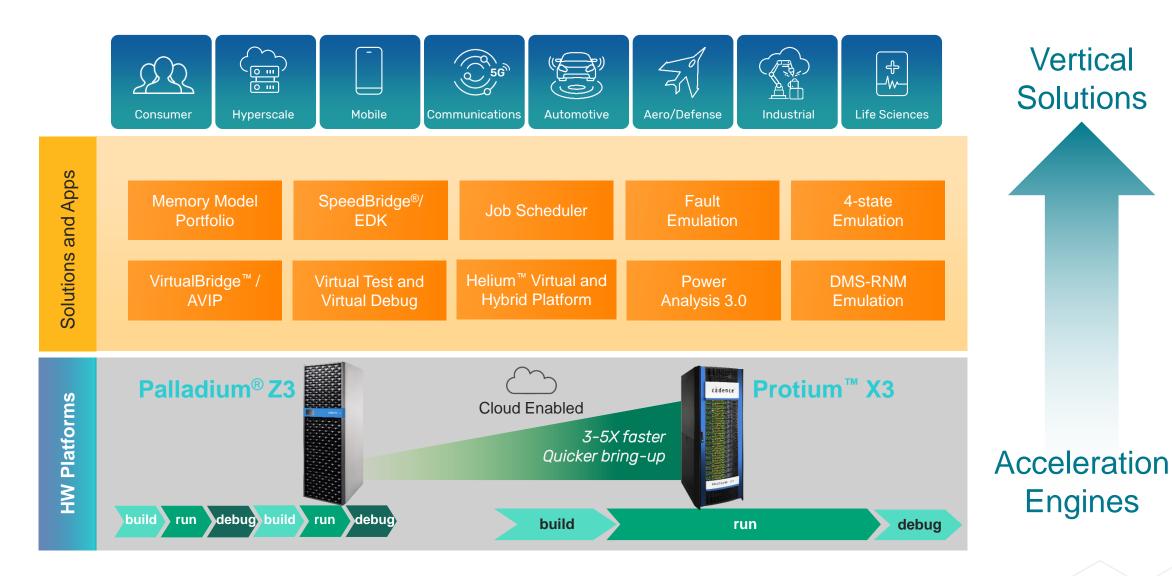

## Cadence's Dynamic Duo

## **Dynamic Duo III Verification Platforms Benefits**

#### Scalability, Congruency, High performance

#### **Emulation Features and Applications**

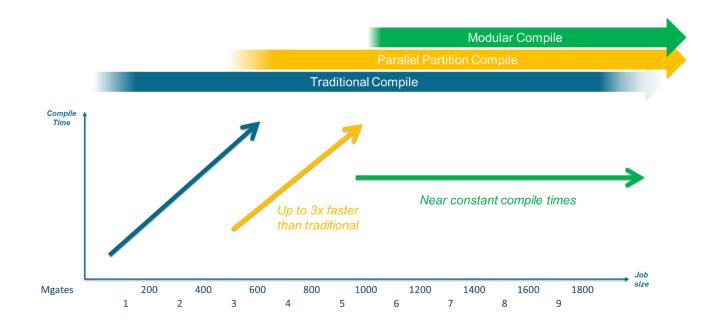

- Modular Compile: 8-hour TAT for any size design

- FullVision Debug: observe any signal with at-speed triggering

- Exclusive use models: 4-state and mixed-signal emulation, 95% accurate power analysis

#### Prototyping Features and Applications

- Modular Compile: 24-hour TAT for designs up to 20 BG

- FullVision Debug: observe any signal without recompile

- Shared Virtual and Physical interface and debug solutions with Palladium

### Cadence Dynamic Duo III

## New! Palladium Z3 System Studio

- Standalone emulator with capacity of 128 million gates

- No Cadence install required unpack and go

- Standalone 4U form factor

- Air-cooled with front-to-back airflow

- Powered from typical lab outlets: 110/220V 15/20A

- Supports up to 8 concurrent users per unit

- Supports up to 4 SpeedBridge ports

- Same software and flow as Enterprise Z3 rack system

**Palladium® Z3** Model: System Studio Standalone 4U form factor

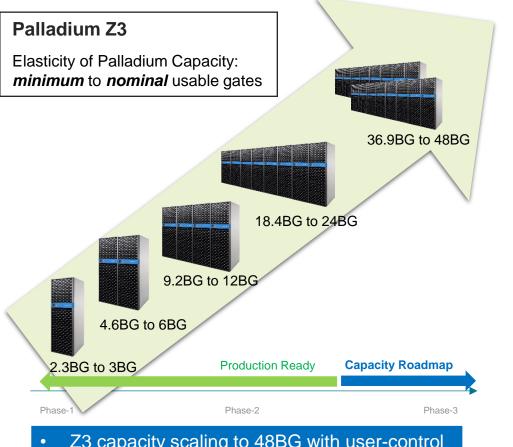

## Scaling both Capacity and Compiler to accommodate rapid design growth

- Z3 capacity scaling to 48BG with user-control granularity of 16MG increments

- Capacity utilization at 100% guaranteed due to processor-based mapping technology

- Modular Compile enables nearly constant compile times based on massively parallelized processor-based compiler with no timing closure required

- Design performance is 100% predictable after compilation

cādence

#### 25 © 2025 Cadence Design Systems, Inc. All rights reserved.

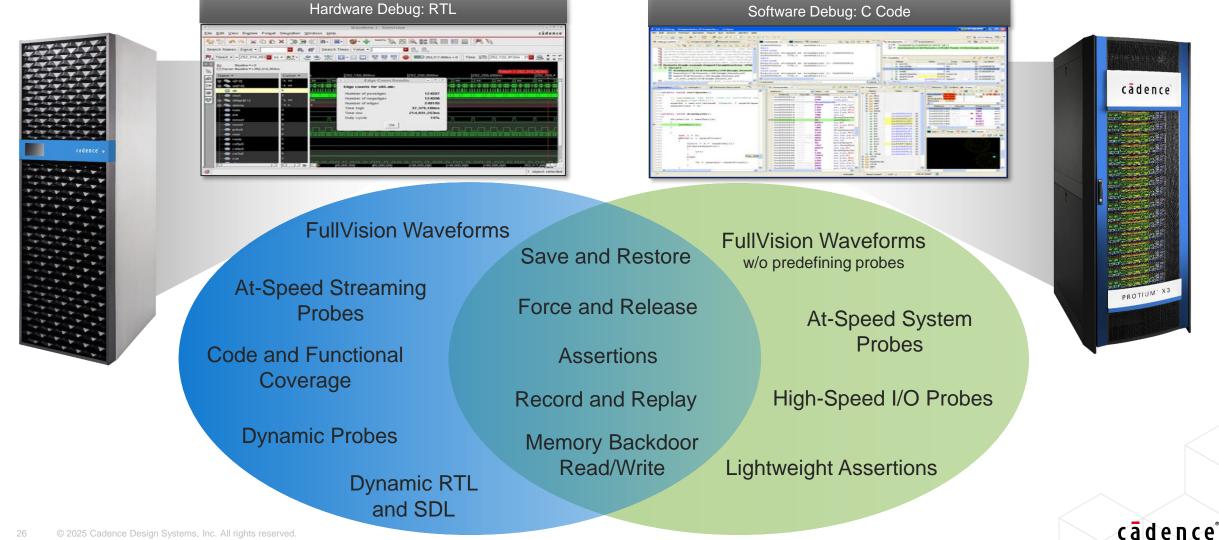

## Dynamic Duo III Debug Productivity

#### **Palladium<sup>®</sup> Hardware-Focused Debug**

**Protium<sup>™</sup> Software-Focused Debug**

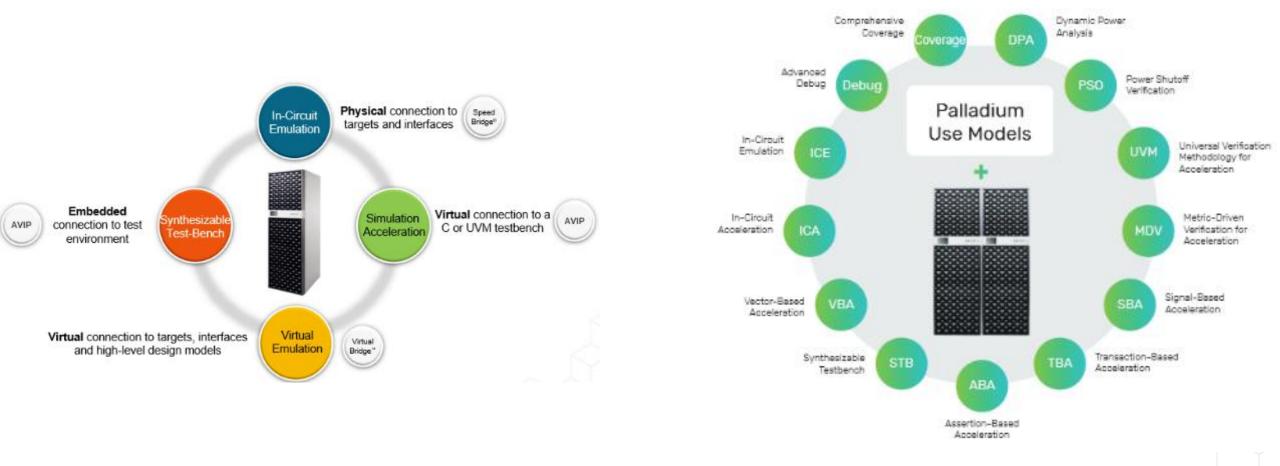

#### The Many Use Cases of Palladium® Emulation

cādence

27 © 2025 Cadence Design Systems, Inc. All rights reserved.

## HW Product Portfolio and Solutions

## Summary

- Software becoming even more important

- The scope and scale are growing exponentially

- Timelines are shrinking

- Modern Software Engineering Practices Are Required

- Cloud-based development environments

- Automated and continuous integration and regression

- Use the different platforms at different stages of the project

- Virtual Prototyping

- Emulation

- Enterprise Prototyping

## Cadence AI-Driven Verification Full Flow

#### **Cloud Enabled**

# cadence

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>https://www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.