# Al Powered Design Verification

Mike Bartley, CEO, Alpinum Consulting

Marmik Soni, Manager, CoE, Tessolve

**Custom Silicon**

Pre Silicon

Post Silicon

Embedded Systems & Software

### Outline

- Tessolve Al Strategy

- 1: UVM AI Training Tool

- 2: Assertify Tool

- 3: Spec Extraction

- Collaboration Opportunity

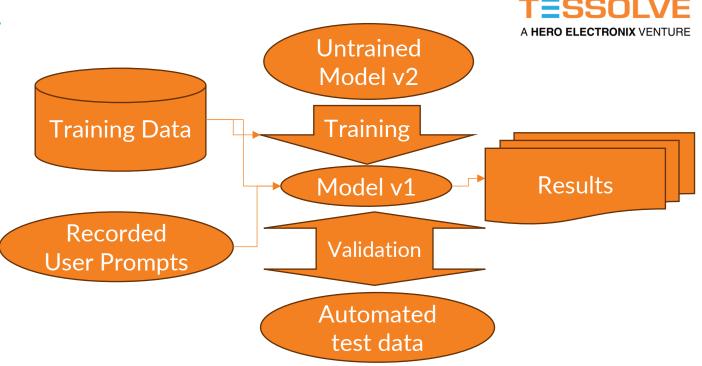

## Tessolve's Effective AI Strategy

- Models are replaceable

- Ensure our data is stored to re-train new model releases

- Maintaining security

- Different set of infra for various security needs

- Centre supports innovation at the edge

- Bot infra design/ suggestions

- Prompt expertise

- Model selection

- Model adaptation

- Al infra migration

- Custom solution design

- Access control

- External tool/ vendor scrutiny

©Tessolve 2025 — Confidential —

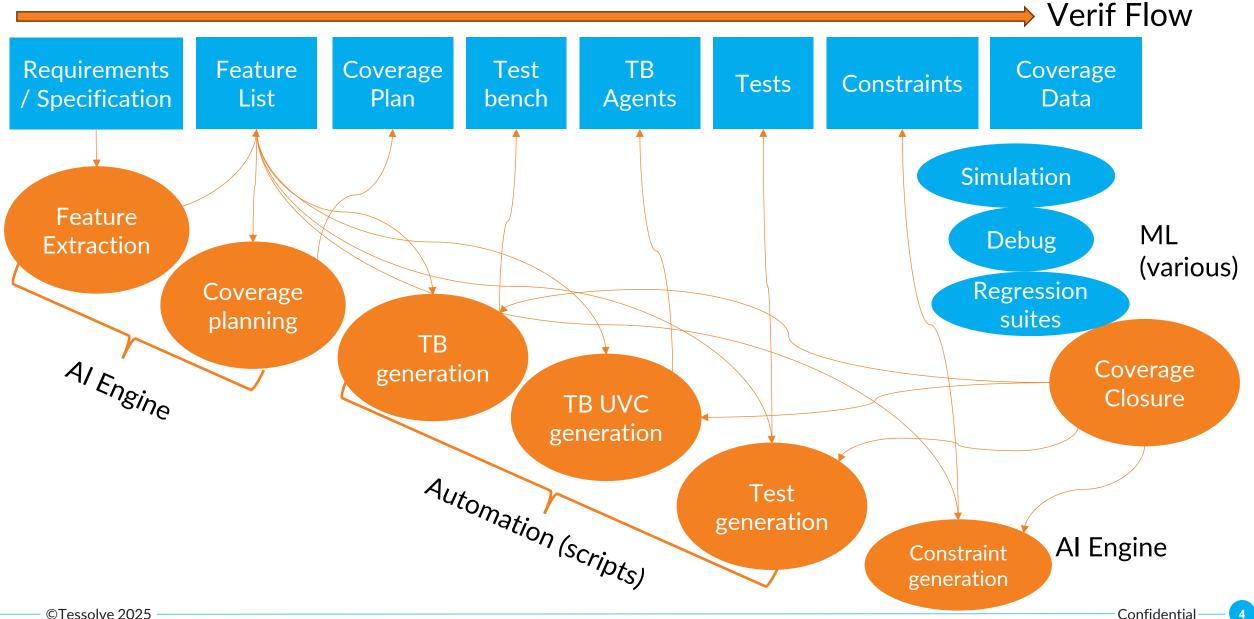

## AI/ML Experiments in IP Verification

## Al Ecosystem

### Knowledge Bots:

- Features: Faster to develop & deploy

- Use case: With less confidential data, Project CoPilot

- Security: Low

- Cost: Low,

- Reasonable accuracy

- Project: UVM Chatbot, Automotive FUSA Assistant

#### Clouds

- Feature: Faster develop & deploy

- **Use case:** Client projects, highly confidential data.

- **Security:** High

- Cost: High

#### Local

- Features: Slower to develop & slower to deploy

- Use case: For highly confidential data

- **Security:** High

- Cost: High

- Challenge: Less

Adaptability, less

Scalability, Upfront Cost

### Al Apps

- •DV Spec Analysis Tool

- DV AI TB Tool

- Assertify Tool

- Code converters (e.g. SV to Cocotb code converters)

- Domain/ Project basedAl models & applications

- PDK AI Training Tool

- •UVM Training Tools

- •Al Code Copilot

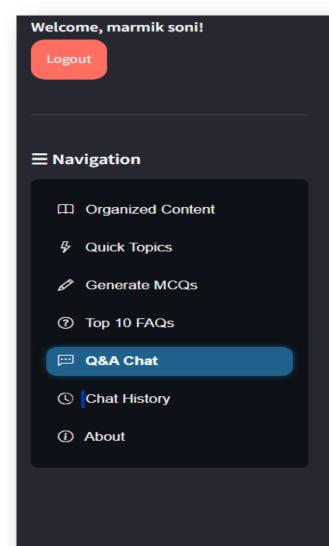

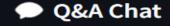

## 1: UVM AI Training Tool

### **Organized Content**

Follows planned flow

### **Quick Topics**

Most important topics' explanation

### **MCQs**

• Test, Evaluation, weak concept suggestions

### **FAQs**

• Clarifies on common important doubts

### Q&A

ANY question support

### About

Tool briefing for effective use

### Dashboards

• Analytics, time spent, evaluation results

### **Benefits:**

- Self guided and self paced flow

- Analytics & custom topic suggestions

- Ask anything about UVM

- Improved accessibility

- Reduced training time

- Scalable for other domains

## 1: UVM AI Training Tool

### **Tessolve UVM AI Training Tool**

- Explain UVM Sequencer please!

- UVM Sequencer

### Introduction

In Universal Verification Methodology (UVM), the sequencer is a key component responsible for controlling the flor sequences that generate complex stimulus and the drivers that convert these stimuli into pin-level activities.

**Role of the Sequencer**

Developed by AI CoE team

## 1: UVM AI Training Tool

©Tessolve 2025 — Confidential

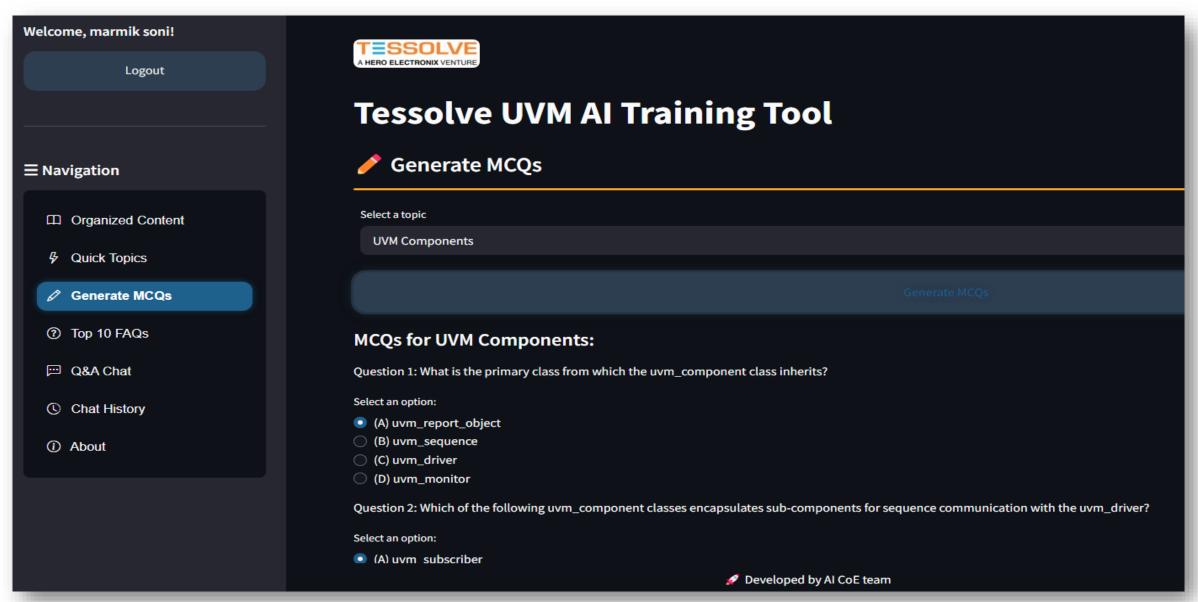

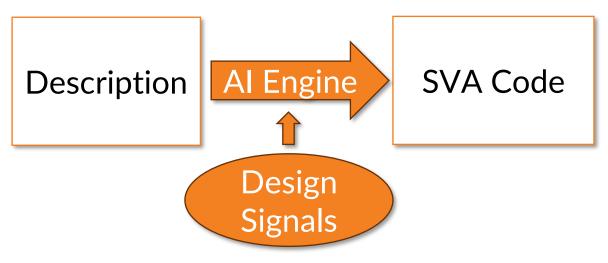

Problems around Assertions are:

| Growing Complexity in Verification | Time intensive asks

| Human Errors | Lack of Consistency and Skill Gap

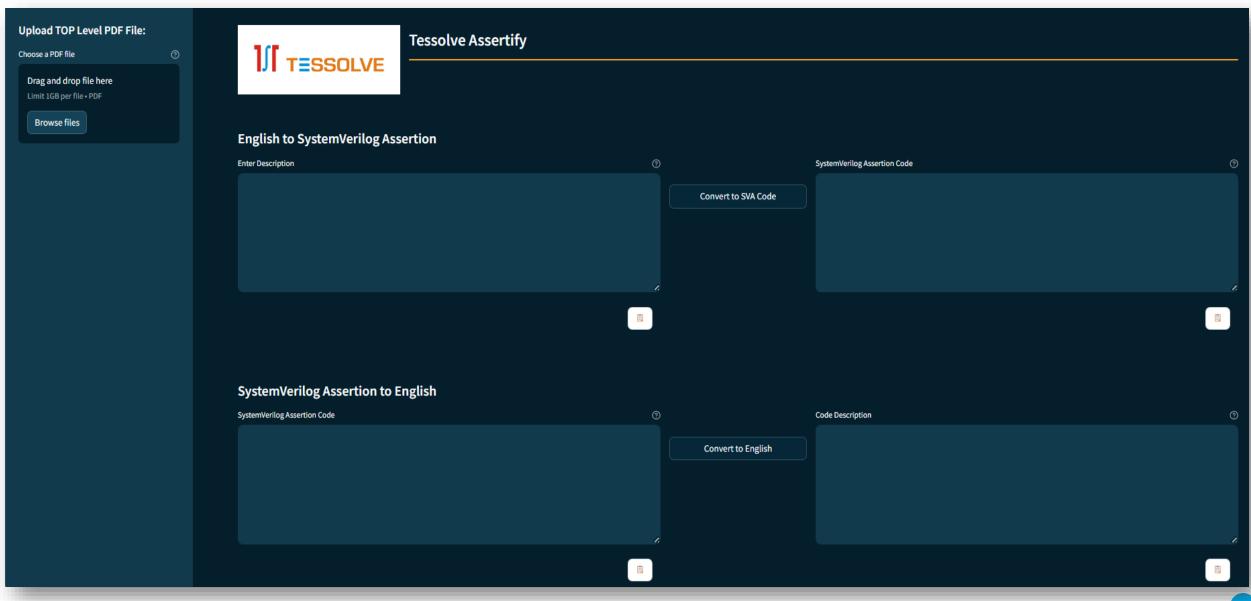

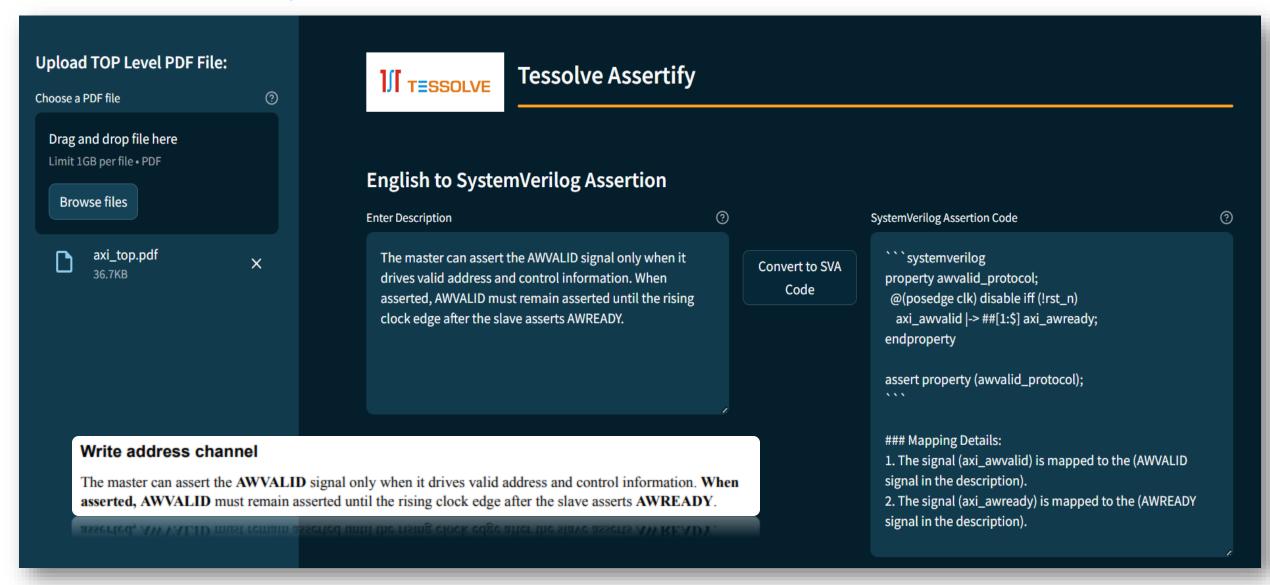

#### Use case:

- 1. Generate Assertions from spec/engineer's simple description using Al models.

- 2. Generate description from the SVA code.

©Tessolve 2025 —

©Tessolve 2025 — Confidential —

## Tool 2: Assertify Tool - Signal match analysis

| # | Approach             | Top signal  | Assertify tool input english description signal | Signal in generated SVA |  |

|---|----------------------|-------------|-------------------------------------------------|-------------------------|--|

| 1 | Case mismatch        | axi_awvalid | AXI_AWVALID                                     | axi_awvalid             |  |

|   |                      | axi_awready | AXI_AWREADY                                     | axi_awready             |  |

| 2 | Additional character | axi_awvalid | AXIVALID                                        | axi_awvalid             |  |

|   |                      | axi_awready | AXIREADY                                        | axi_awready             |  |

| 3 | Partial match        | axi_awvalid | AXIVLD                                          | axi_awvalid             |  |

|   |                      | axi_awready | AXIRD                                           | axi_awready             |  |

| 4 | Partial match        | axi_awvalid | valid                                           | axi_awvalid             |  |

|   |                      | axi_awready | ready                                           | axi_awready             |  |

| 5 | Highly mismatch      | axi_awvalid | VLD                                             | axi_awvalid             |  |

|   |                      | axi_awready | RDY                                             | axi_awready             |  |

©Tessolve 2025 — Confidential —

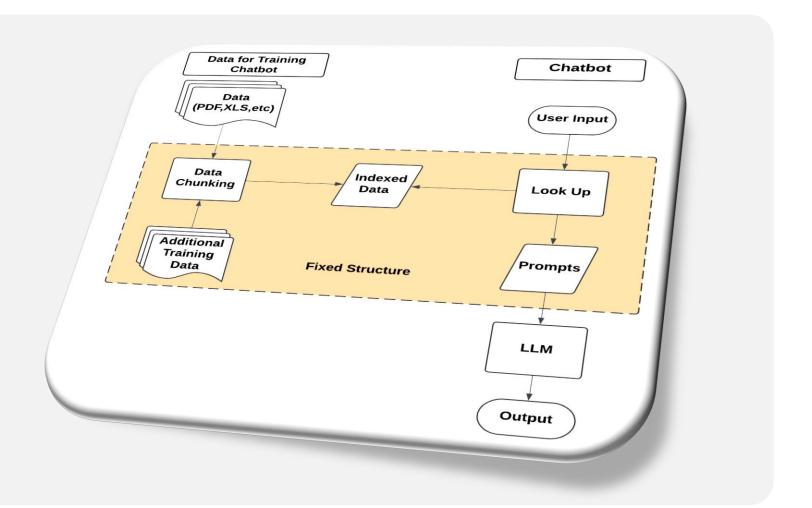

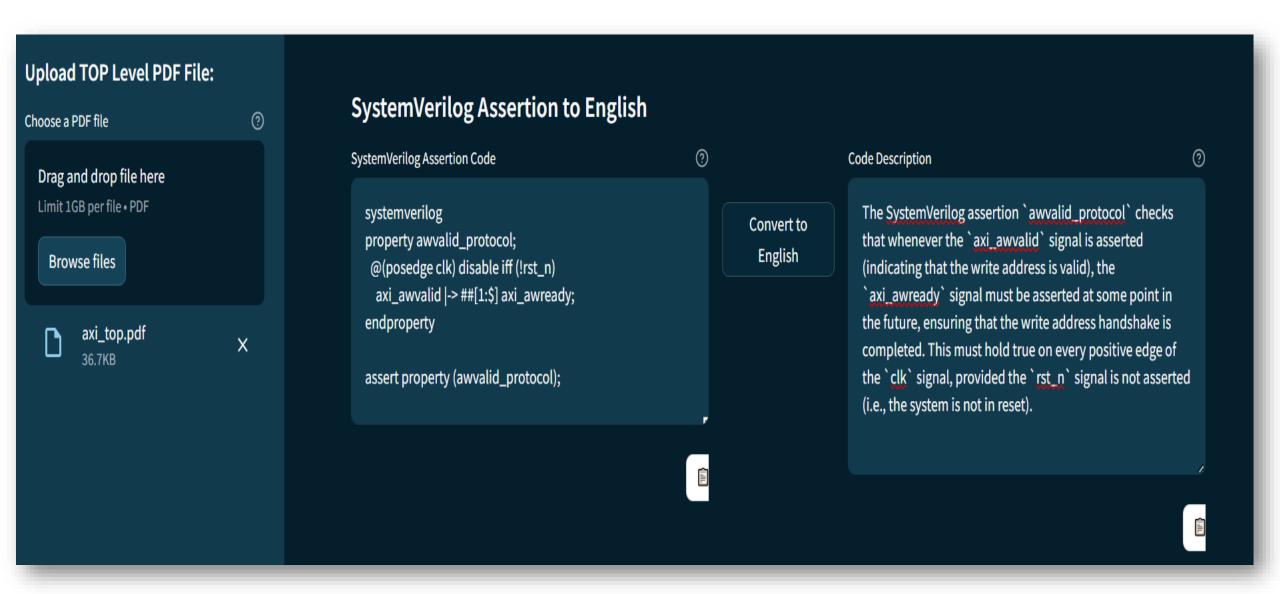

## **Tool 3: Spec Extraction Tool**

- RAG (Retrieval Augmented Generation)

Tool for DV Spec Extraction

- Inputs: Project Spec, Training Data,

- Prompt (Character)

- User Prompt

- LLM Intelligence

- Output

### **Flow**

Spec PDF Review

Model benchmarking

Prompt and response recording

Filtering by manual validation

Excel sheet with confidence score

## **Tool 3: Spec Extraction Tool**

### **Extraction Process**

### **Tessolve Chatbot v6.0**

please generate detailed AXI4 feature list with different bus channels, unaligned data transfers, burst based transactions with more details on burst type, burst size and length from the uploaded pdf

#### **Detailed AXI4 Feature List**

#### 1. AXI4 Bus Channels

The AXI4 protocol defines several independent transaction channels to facilitate high-performance and high-frequency system designs. These channels are:

- Read Address Channel: Carries control information describing the nature of the data to be transferred for read operations.

- Read Data Channel: Transfers data from the slave to the master during read operations.

- Write Address Channel: Carries control information describing the nature of the data to be transferred for write operations.

- Write Data Channel: Transfers data from the master to the slave during write operations.

- Write Response Channel: Signals the completion of the write transfer from the slave to the master.

These channels allow for the separation of address/control and data phases, which helps in achieving high-frequency operation without using complex bridges.

#### 2. Unaligned Data Transfers

The AXI protocol supports unaligned data transfers using byte strobes. This feature is crucial for accessing mixed-endian data structures in a single memory space. The protocol uses a byte-invariant endianness scheme, which ensures that any multi-byte element in a data structure:

- Uses the same continuous bytes of memory, regardless of the endianness of the data.

- The order of bytes in memory is determined by the endianness, indicating whether the first byte in memory is the most significant byte (MSB) or the least significant byte (LSB) of the element.

- Any byte transfer to a given address passes the eight bits of data on the same data bus wires to the same address location, regardless of the endianness of any data element.

#### 3. Burst-Based Transactions

The AXI protocol is burst-based and defines three burst types:

- Fixed Burst: The address remains constant for every transfer in the burst.

- Incrementing Burst (INCR): The address increments by the size of the transfer for each transfer in the burst.

- Wrapping Burst: The address increments like an incrementing burst but wraps around to a lower address when a wrap boundary is reached.

Burst Size

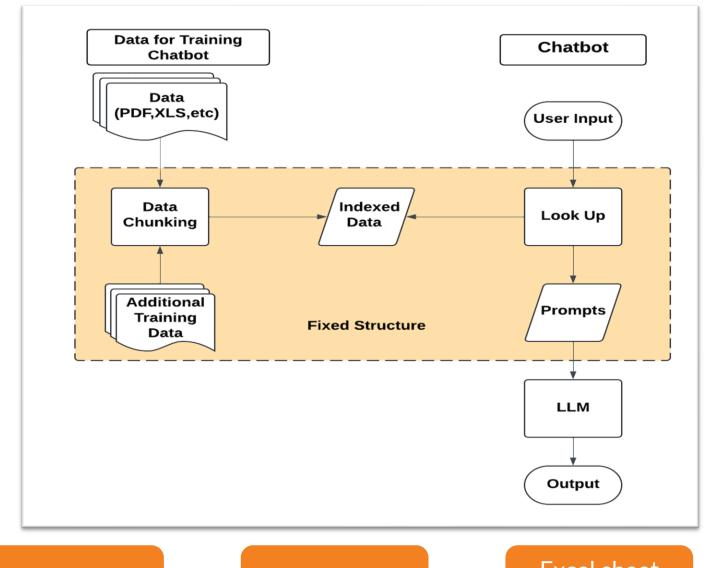

## **RAG** Assessment

Manual validation **RAG** The generated content is manually validated by the engineers and Assessment tagged with confidence score (How satisfied they are with the response?) **RAG Pipeline Assessment** Retrieval Generation **Data for Training** Chatbot Context Recall Context Faithfulness Answer Chatbot Precision (SNR (Continuity to Relevancy (with (Factual Data of the content) the question) answers) accuracy) (PDF,XLS,etc) **User Input** Data Indexed Look Up questions from Faithfullness Chunking Data test datatset Context Recall **RAGAS Context Precesion** Answer Relevancy Additional answer for **Prompts** Training evaluation **Fixed Structure** Data LLM Existing RAG application Output **Test Set** Generation

## **RAG** Assessment

| question                                                | answer                                                  | contexts                                             | ground_truth                                            | faithfulness | answer_relevancy | context_recall | context_precision |

|---------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|--------------|------------------|----------------|-------------------|

| What role do integrated circuits (ICs) play in          | Integrated<br>circuits (ICs) are<br>used in virtuall    | [Applications in<br>Electronics\nThe ability<br>to c | Integrated<br>circuits (ICs) are<br>fundamental<br>buil | 1.000000     | 0.946481         | 1.00           | 1.0               |

| What are the potential future developments in           | The future of semiconductors will likely invol          | [Future Directions\nThe<br>future of<br>semiconducto | The future of semiconductors is poised for exc          | 1.000000     | 0.992269         | 1.00           | 1.0               |

| How does<br>Moore's Law<br>relate to the<br>development | Moore's Law<br>predicts that the<br>number of<br>transi | [The Role in<br>Technological<br>Advancement\nThe co | Moore's Law<br>predicts that<br>the number of<br>transi | 0.833333     | 0.936722         | 1.00           | 1.0               |

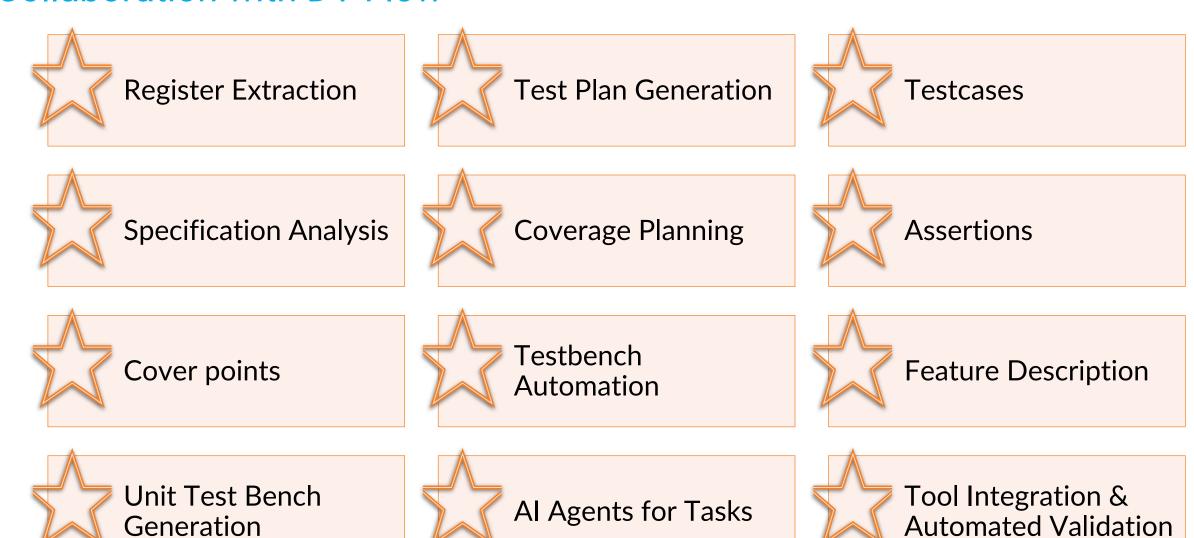

### Collaboration with DV Flow

## Collaboration with AI Research

©Tessolve 2025

### A HERO ELECTRONIX VENTURE

# **THANK YOU**

www.tessolve.com

mike@alpinumconsulting.com, marmikbhupendrakumar.soni@tessolve.com

+44 7796 307958 +91 9033967780

Chip Design

Test Engineering

Hardware Design

Embedded Systems