# REPsemiconductor

# VISC

#### Versatile Intrinsic Structured Computing In-Line Accelerator for AI, Maths and Cryptography

Boom in 'Always-on' Real-Time Edge Processing applications is driving demand for Performance with Security

VISC solves the challenges of Real-Time Algorithmic Processing for Edge Al

James Lewis Chief Executive Officer

james.lewis@redsemiconductor.com +44 (0)7903 849974

semiconductor

# RED semiconductor

# VISC

#### Versatile Intrinsic Structured Computing In-Line Accelerator for AI, Maths and Cryptography

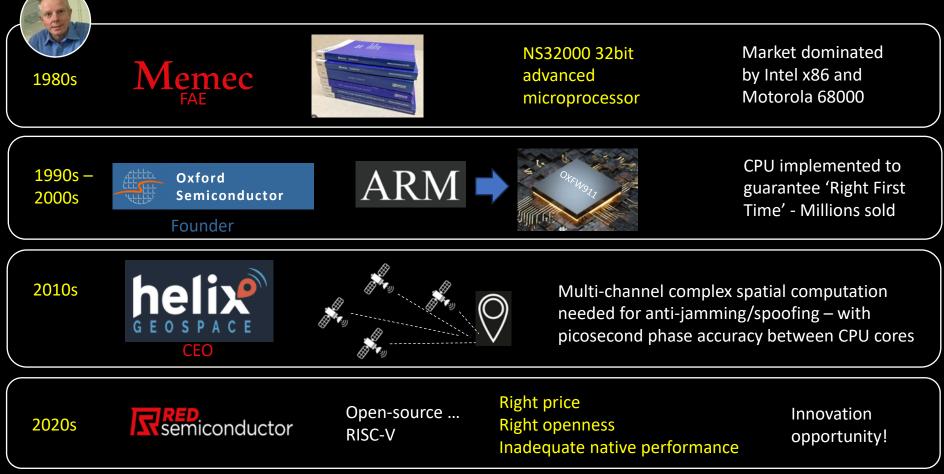

# **RISC-V: Innovating Within an Established Architecture**

Solving the challenges of Real-Time Algorithmic Processing for Edge Al

James Lewis Chief Executive Officer

james.lewis@redsemiconductor.com +44 (0)7903 849974

Serniconductor

# RED semiconductor

# VISC

#### Versatile Intrinsic Structured Computing In-Line Accelerator for AI, Maths and Cryptography

Boom in 'Always-on' Edge Real-Time Processing applications is driving demand for Performance with Security

VISC solves the challenges of Real-Time Algorithmic Processing for Edge Al:

- Novel Pre-Pipeline Technology Processor Independent

- Enables Maximum Efficiency and Simultaneous Execute

- Best Maths per Watt per Dollar

- Patent filed

James Lewis Chief Executive Officer

james.lewis@redsemiconductor.com +44 (0)7903 849974

semiconductor

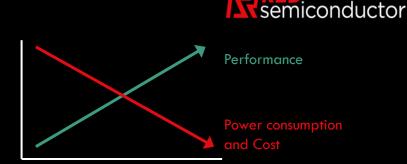

# We always need more processing performance!

#### Processor requirement persist:

- More performance

- Lower power consumption

- Lower cost

Remiconductor

We always need more processing performance!

#### Processor requirement persist:

- More performance

- Lower power consumption

- Lower cost

#### Traditional solution – chase Moore's Law:

- Clock the processor faster to get performance (but increases power consumption)

- Make the transistors smaller to reduce power consumption (but latest processes are hugely expensive)

We always need more processing performance!

#### Processor requirement persist:

- More performance

- Lower power consumption

- Lower cost

#### Traditional solution – chase Moore's Law:

- Clock the processor faster to get performance (but increases power consumption)

- Make the transistors smaller to reduce power consumption (but latest processes are hugely expensive)

Now Moore's Law has hit physical limitations and/or prohibitive costs – Other ways of performance/Power improvement are needed:

• Accelerators

# Performance demands will continue to increase – Smart solutions required

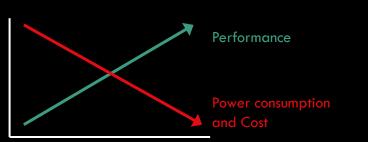

# Traditional acceleration vs. VISC acceleration

#### Traditional co-processor acceleration:

# Traditional acceleration vs. VISC acceleration

# Processor Processor burden is increased by co-processor management Accelerator/ Co-Processor Accelerator usage Inefficient accelerator usage Wasted silicon area- cost inefficient

#### Traditional co-processor acceleration:

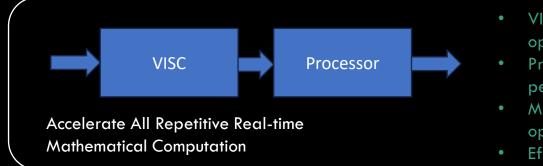

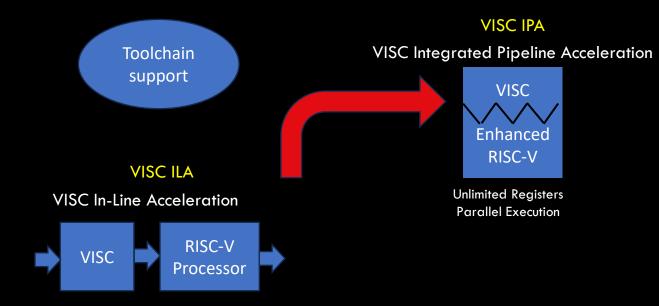

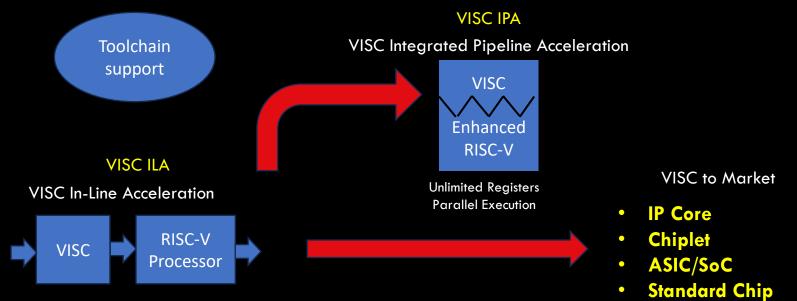

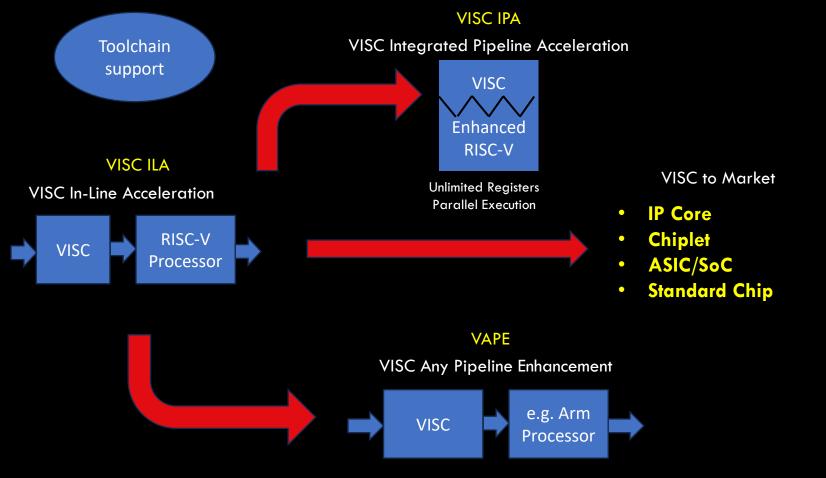

#### VISC In-Line Acceleration (VILA):

- VILA makes processor execution highly efficient optimises performance

- Processor unburdened by accelerator optimises performance

- Minimises clock cycles and memory accesses optimises power usage

- Efficient use of silicon optimises cost

#### Target for VISC is PPAS (Power, Performance, Area, Security) Optimisation

REPiconductor

#### Inspiration, Contextualisation, Non-linear thinking ... Customer NEED

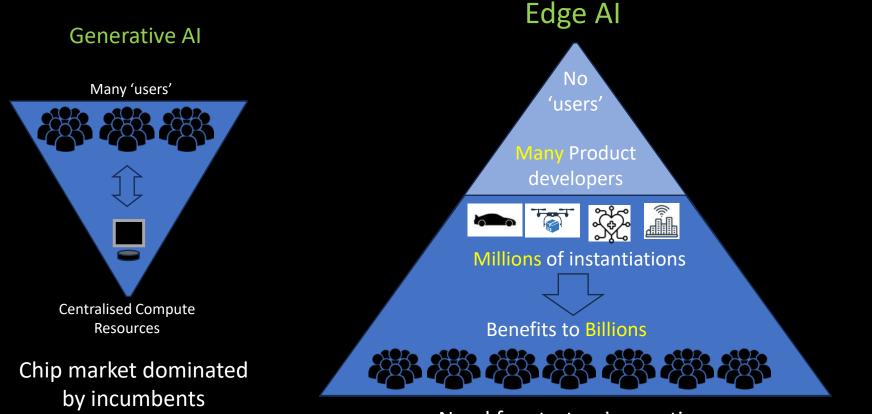

RED Semiconductor - Focusing on AI at the Edge

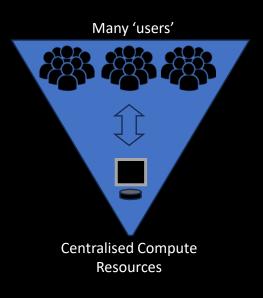

#### **Generative AI**

Chip market dominated by incumbents

## RED Semiconductor - Focusing on AI at the Edge

Need for startup innovation

Al at the Edge demands affordable real-time processing of complex data with low power consumption - And it must be secure.

## **RED's Markets and Applications**

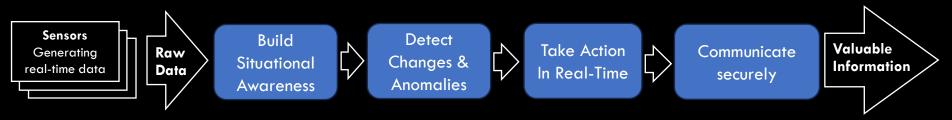

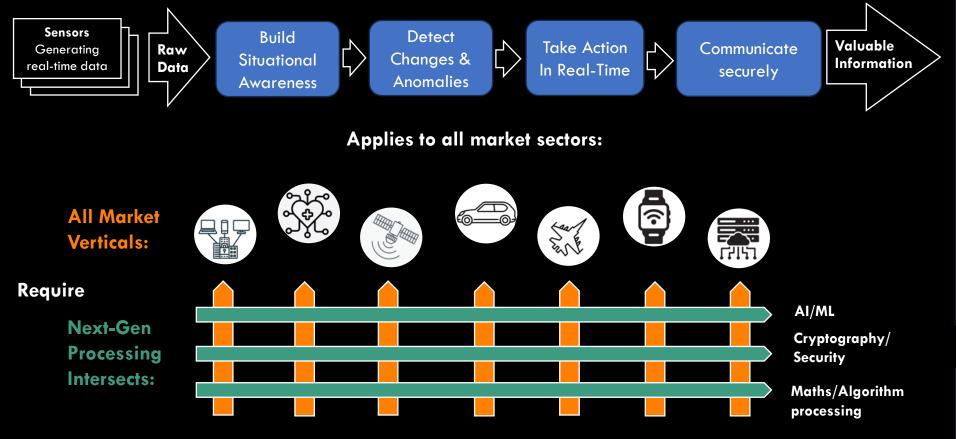

Typical Edge Processing demands:

## **RED's Markets and Applications**

**REP** semiconductor

#### Typical Edge Processing demands:

## **RED's Markets and Applications**

#### Typical Edge Processing demands:

#### **Ubiquitous demand for Improved PPA+S**

Edge AI – Innovation driven by application need

# Lives saved; Economic productivity grow; Security improved; People thrive

• What is VISC? – Maths-oriented Processor accelerator – for markets that need AI, Cryptography, Autonomous Systems computation.

- What is VISC? Maths-oriented Processor accelerator for markets that need AI, Cryptography, Autonomous Systems computation.

- How fast? Delivers >100x performance improvement (speed & power consumption) for key functions like Matrix Multiply, FFT, DCT, Big Integer Maths, etc.

- What is VISC? Maths-oriented Processor accelerator for markets that need AI, Cryptography, Autonomous Systems computation.

- How fast? Delivers >100x performance improvement (speed & power consumption) for key functions like Matrix Multiply, FFT, DCT, Big Integer Maths, etc.

- How does it do it? Using run-time Al-based re-sequencing of operands and instructions, and reordering of execution sequence, enabling parallel execution in a single pipeline.

- What is VISC? Maths-oriented Processor accelerator for markets that need AI, Cryptography, Autonomous Systems computation.

- How fast? Delivers >100x performance improvement (speed & power consumption) for key functions like Matrix Multiply, FFT, DCT, Big Integer Maths, etc.

- How does it do it? Using run-time Al-based re-sequencing of operands and instructions, and reordering of execution sequence, enabling parallel execution in a single pipeline.

- VISC instructions? Fully compatible with RISC-V, Abstracted VISC Instructions gives complex functions just 1 instruction to configure data sequencing and hardware execution.

- What is VISC? Maths-oriented Processor accelerator for markets that need AI, Cryptography, Autonomous Systems computation.

- How fast? Delivers >100x performance improvement (speed & power consumption) for key functions like Matrix Multiply, FFT, DCT, Big Integer Maths, etc.

- How does it do it? Using run-time Al-based re-sequencing of operands and instructions, and reordering of execution sequence, enabling parallel execution in a single pipeline.

- VISC instructions? Fully compatible with RISC-V, Abstracted VISC Instructions gives complex functions just 1 instruction to configure data sequencing and hardware execution.

- VISC hardware? High-performance Vector Engine vectorises and re-sequences execution of repetitive real-time operations.

- What is VISC? Maths-oriented Processor accelerator for markets that need AI, Cryptography, Autonomous Systems computation.

- How fast? Delivers >100x performance improvement (speed & power consumption) for key functions like Matrix Multiply, FFT, DCT, Big Integer Maths, etc.

- How does it do it? Using run-time Al-based re-sequencing of operands and instructions, and reordering of execution sequence, enabling parallel execution in a single pipeline.

- VISC instructions? Fully compatible with RISC-V, Abstracted VISC Instructions gives complex functions just 1 instruction to configure data sequencing and hardware execution.

- VISC hardware? High-performance Vector Engine vectorises and re-sequences execution of repetitive real-time operations.

- Technical differentiation? Comprehensive patent applied for.

VISC's key to real-time execution is processor instruction and data-flow efficiency

How can a startup innovate CPU architecture?

How can a startup innovate CPU architecture?

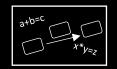

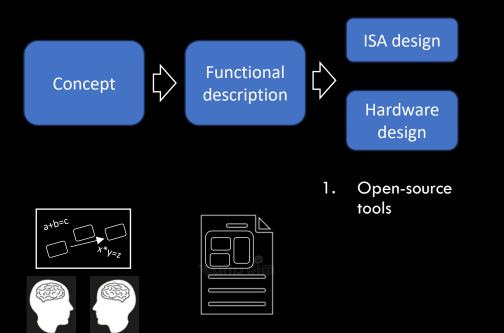

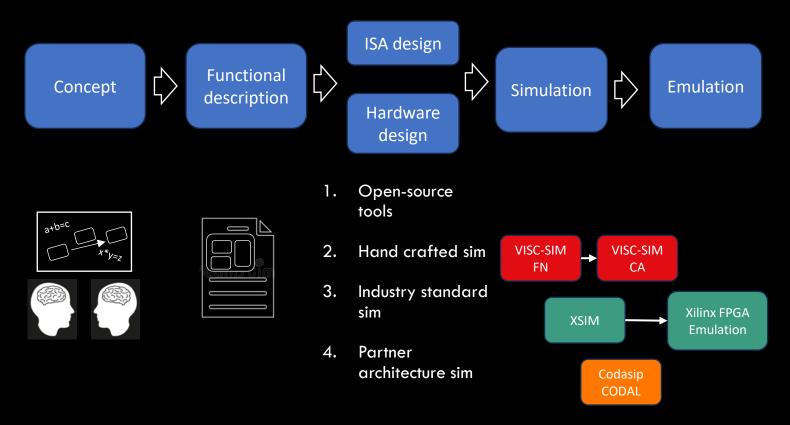

#### How can a startup innovate CPU architecture?

#### How can a startup innovate CPU architecture?

#### Innovation => Verification flow

#### Initial use of open-source tools – leading to industry-standard toolchain

# Benchmark: 4 x 4 Matrix Multiply (10 repeats)

|                                                                | Instructions<br>written/compiled | Instructions<br>fetched                               | Instructions<br>executed | Data memory<br>accesses | Clock cycles to<br>execute     |

|----------------------------------------------------------------|----------------------------------|-------------------------------------------------------|--------------------------|-------------------------|--------------------------------|

| RISC-V                                                         | 31                               | 3210                                                  | 321                      | 96                      | 4536                           |

| VISC + RISC-V                                                  | 10                               | 14                                                    | 115                      | <b>48</b>               | 1194                           |

| Performance Multiple                                           | 3x                               | <b>200x</b>                                           | <b>2</b> x               | <b>2</b> x              | <b>4</b> x                     |

| One-third of<br>the code to<br>write and<br>debug with<br>VISC | •                                | Fraction<br>memor<br>accesses g<br>huge pow<br>saving | y<br>ives<br>ver         | perfor<br>boos          | 00%<br>rmance<br>t with<br>ISC |

Big performance gains with only 15% silicon area increase

# VISC future performance roadmap

| Abstr<br>VI<br>Instru                                  | SC re-se                        | rised and<br>quenced<br>ecution | No limit to<br>egister file size     | No limit to<br>parallel execute<br>units                               |  |

|--------------------------------------------------------|---------------------------------|---------------------------------|--------------------------------------|------------------------------------------------------------------------|--|

|                                                        |                                 | $\widehat{\boldsymbol{A}}$      | $\sum$                               | $\sum_{i=1}^{n}$                                                       |  |

| Development Phase                                      | VISC Accelerator Front-end      |                                 | VISC Integrated into CPU core        |                                                                        |  |

| Timescale                                              | NOW                             | 2025/6                          | 2026                                 | 2027/28                                                                |  |

|                                                        | MVP<br>(Basic VISC<br>features) | Enhanced VISC<br>features       | Extended Registers<br>in RISC-V core | Parallel execute Units in<br>RISC-V core + additional<br>VISC features |  |

| Run-time Performance<br>Multiplier for design<br>phase | 4-10x                           | 5-10x                           | 2-5x                                 | Unlimited by architecture                                              |  |

| Total Run-Time<br>Performance Multiplier               | 5-10x                           | 25-100x                         | 50-500x                              | Unlimited                                                              |  |

VISC enables RISC-V core developers to add symbiotic features for optimal performance

Versatility in Toolchain => Alignment with Industry Standard Tools and Customer Workflow

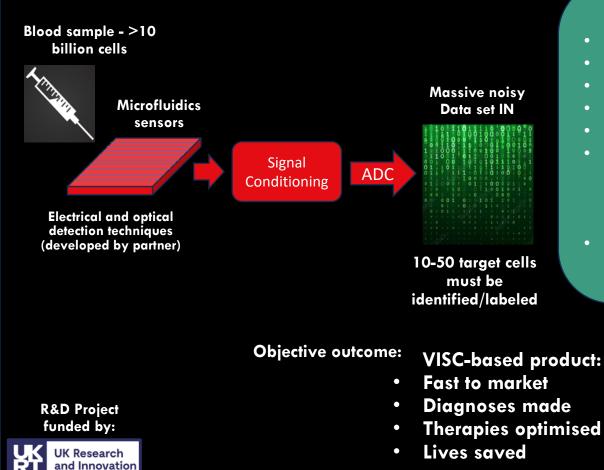

#### VISC case study – Health-tech Blood cell labeling and analysis for cancer detection and therapy

#### Lead customer application in development now...

# VISC - AI

- Multiple channels/parallel processing

- Error detection/correction

- Pattern detection/Anomaly rejection

- Needle-in-haystack artefact finding

- Real-time diagnostics/therapeutics

- Early FPGA development:

- Algorithm refinement

- Functional verification

- Execution speed assessment

- 1st training model for cancer therapeutics; subsequent training models for other diseases/conditions

#### Lessons learnt and applied

- Don't let back-end verification concerns stifle front-end innovation

- Align innovation with market need, not incumbent trend

- Focus first on functional verification

- Design-in get-outs for unanticipated bugs, and timing

- Re-focus on timing verification when technology gets close to customer adoption

- Partnerships are key Product/Market Fit; Design flow; Layout and Verification; silicon testing, application code development

- Startups can impact the domains of long-term incumbents with innovative thinking (innovate technology, <u>and</u> business model)

- VISC will positively impact AI and Edge processing

# **R**emiconductor

# VISC

Semiconductor

VISC

# **Versatile Intrinsic Structured Computing** The Powerful RISC-V AI CPU and Maths Accelerator

James Lewis

Chief Executive Officer james.lewis@redsemiconductor.com +44 (0)7903 849974