## Using AI/ML to Improve DV Productivity DVClub Bristol

Steve Hobbs April 9, 2025

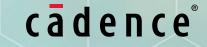

## Where Does AI/ML Fit with Hardware Design and Verification

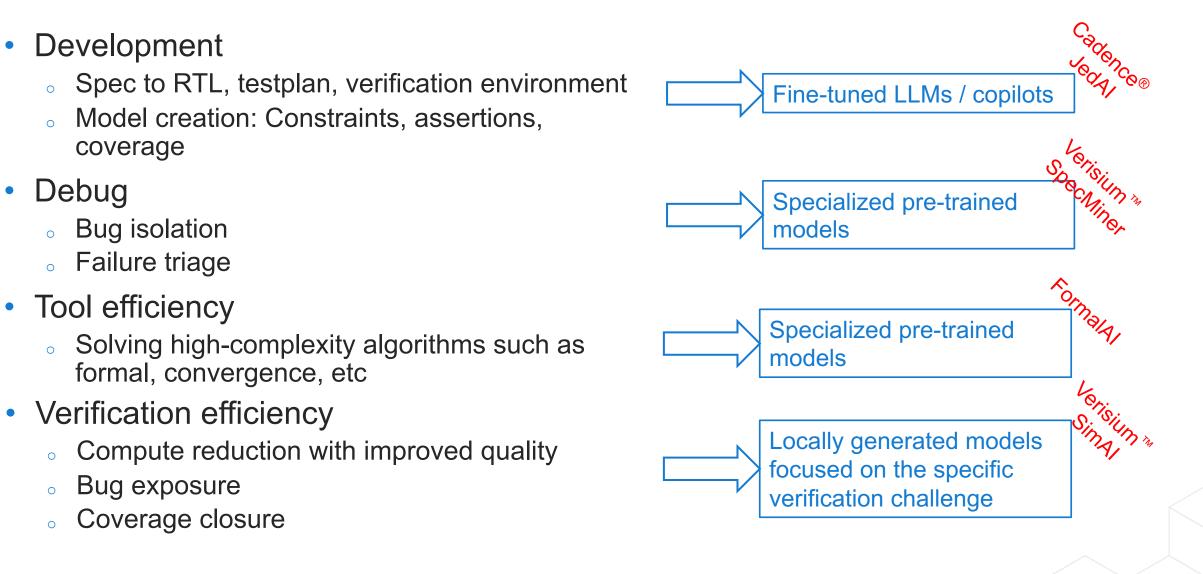

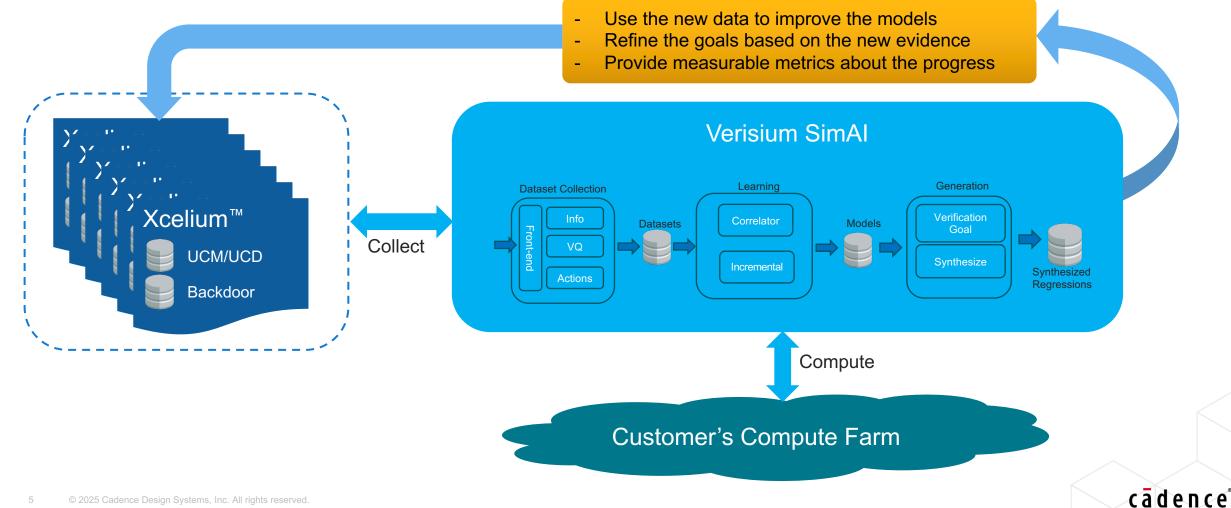

## What Verisium SimAI Does

## How Verisium SimAI Has Evolved

- Started with goal of replicating the coverage of a random regression with minimal seeds

- Expand the range of problems Verisium<sup>™</sup> SimAI can attack and its usage throughout the design/verification cycle

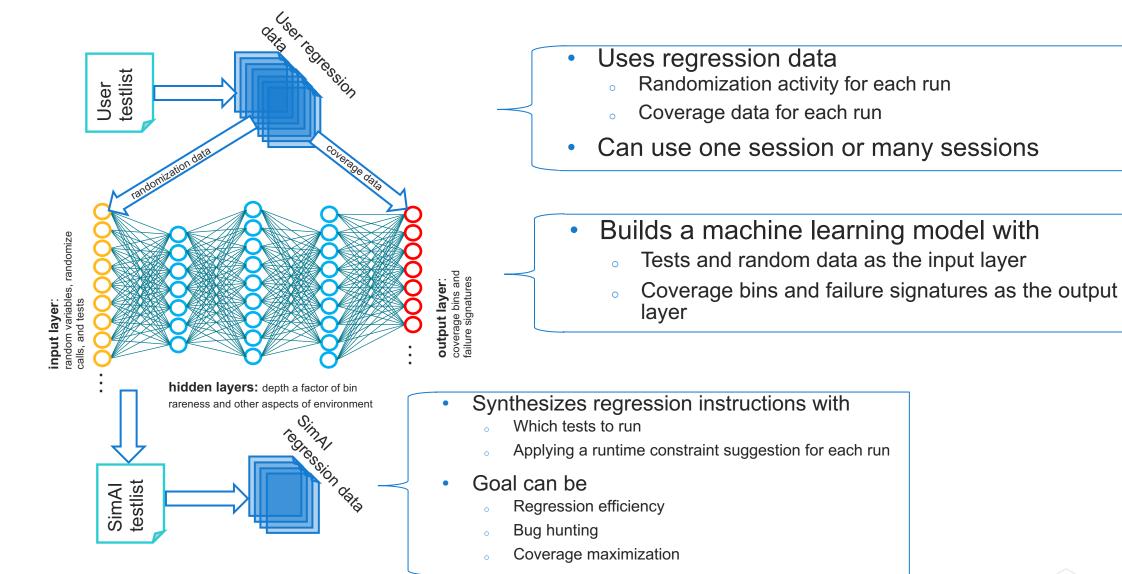

- Bug Hunting: Stress hard-to-reach scenarios, either rare coverage bins or rare failure signatures

- Coverage Maximization: Target unhit bins by means of structural information of the coverage space, with special emphasis on cross-coverage

- Bias of Input Sequences: Ensure the randomization space is fully explored, with particular emphasis on the crosscombination of relevant random variables

- Handling new goals and dealing with extremely complex environments lead to architectural changes

- Iterative (reinforcement) learning

- Scalability improvements

## How Verisium SimAl Works

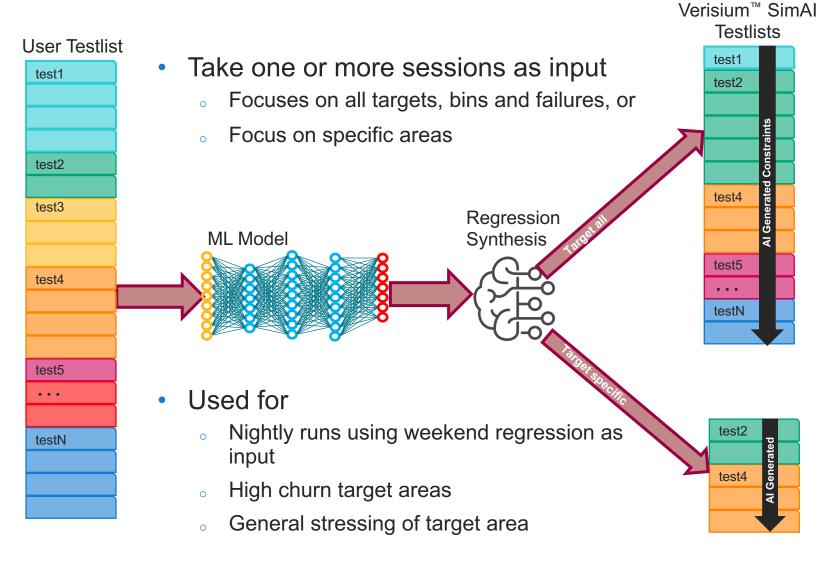

- Verisium<sup>™</sup> SimAI takes the data from regressions with many simulation runs and synthesizes a new regression targeted to verification goal

- Uses an iterative framework to update runs with new instructions

## Challenges

- Size of problem

- Tens of thousands to hundreds of thousands of simulation runs

- Tens of thousands to hundreds of thousands of random variables

- Millions of coverage bins

- Not large in the sense of what LLMs train on, but a large amount of data to build a local ML model.

- Other concerns

- Off-the-shelf big data tools don't apply

- Customers have tight requirements on CPU and memory usage

- Solutions

- Create custom ML algorithms (similar to but different from off-the-shelf solutions)

- Parallelize everything (collecting data, building models, synthesizing regressions)

- Optimize Python libraries for heavy operations (like matrix manipulation) two orders of magnitude reduction in memory

- Optimize data being stored and worked on

### Verisium SimAl for Performance Generate efficient sets of focused runs

- Prunes tests that don't aid in achieving goal

- Adds more runs of most relevant test

- Adds run specific constraint instructions to focus runs

## Example Using Verisium SimAI to Stress Failure Area

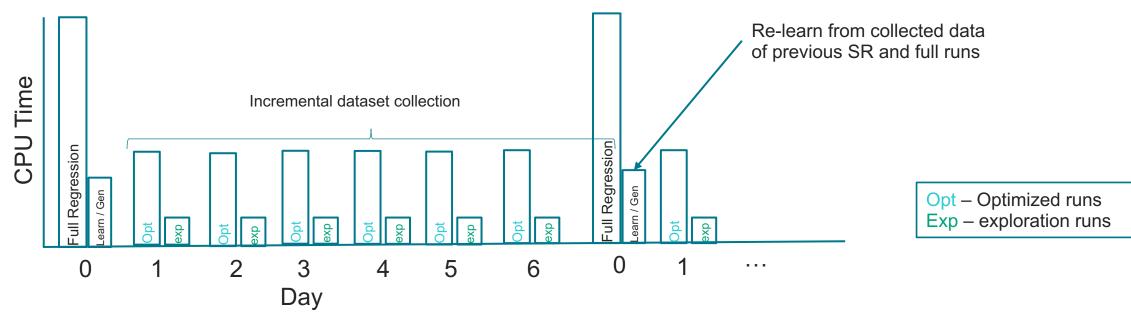

- Verisium<sup>™</sup> SimAI regressions typically 30% of the original run count

- 1<sup>st</sup> Verisium SimAI regression CPU time 30%-50% of original regression, including training and generation

- Increasing efficiency as training amortized across further regressions

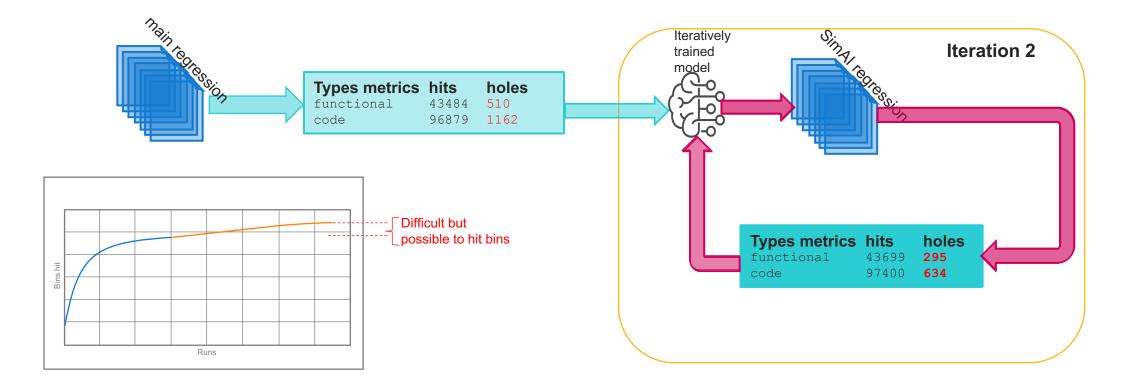

## Example of Verisium SimAI for Coverage Maximization

- When regression is largely saturated

- Use Verisium<sup>™</sup> SimAI to explicitly try to hit uncovered bins

- Each iteration learns what worked and what didn't

- Can be used for bug hunting, using holes as interesting targets

## Verisium SimAI in Project Use

- Early project

- More full regressions, possibly daily use optimization and exploration runs or other augmentation runs to generate more scenarios targeted to corner cases or other important areas, target difficult failure signatures to improve coverage of an error condition

- Middle project

- Optimization and exploration runs become daily regression with periodic runs of full regression

- Fill out CPU budget with bug-hunting runs

- Late project

- Optimization and exploration runs become primary regression with some augmentation from original regression

- Increase bug hunting

- Use ML to help hit particularly difficult bins and fill out cross-coverage bins or other bins that require large numbers of runs to hit

## Any Questions?

# cādence

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks of PCI-SIG. All other trademarks are the property of their respective owners.