# Getting started with UVM or use Formal Instead?

Delivering KnowHow

# Getting started with UVM or use Formal Instead?

# Getting started with UVM or use Formal Instead?

Copyright © 2015-2024 by Doulos. All Rights Reserved

All intellectual property rights, including copyright, patents, design rights and know-how in or relating to the course or course materials provided or made available in connection with the course remain the sole property of Doulos Ltd or their respective owners and no copies may be made of course materials unless expressly agreed in writing by Doulos Ltd.

All trademarks acknowledged.

Doulos takes great care in developing and maintaining materials to ensure they are an effective and accurate medium for communicating design know-how. However, the information provided on a Doulos training course may be out of date or include omissions, inaccuracies or other errors. Except where expressly provided otherwise in agreement between you and Doulos, all information provided directly or indirectly through a Doulos training course is provided "as is" without warranty of any kind.

Doulos hereby disclaims all warranties with respect to this information, whether express or implied, including the implied warranties of merchantability, satisfactory quality and fitness for a particular purpose. In no event shall Doulos be liable for any direct, indirect, incidental special or consequential damages, or damages for loss of profits, revenue, data or use, incurred by you or any third party, whether in contract, tort or otherwise, arising for your access to, use of, or reliance upon information obtained from or through a Doulos training course. Doulos reserves the right to make changes, updates or corrections to the information contained in its training courses at any time without notice.

Doulos Limited

Church Hatch, 22 Market Place,

Ringwood, Hampshire, BH24 1AW, UK

Tel: +44 (0) 1425 471223

Email: [info@doulos.com](mailto:info@doulos.com)

Doulos

6203 San Ignacio Avenue, Suite 110,

San Jose, CA 95119, USA

Tel: 1-888-GO DOULOS

Email: [info.usa@doulos.com](mailto:info.usa@doulos.com)

[www.doulos.com](http://www.doulos.com)

# Contents

|                                                   |    |

|---------------------------------------------------|----|

| Contents.....                                     | 7  |

| What is UVM? .....                                | 9  |

| Getting Started with UVM.....                     | 12 |

| UVM “Hello World” .....                           | 13 |

| Making a real testbench .....                     | 18 |

| Should I use Formal Instead? .....                | 22 |

| Formal is Not Hard to Use.....                    | 23 |

| Understanding Formal.....                         | 27 |

| Under-constraining versus Over-constraining ..... | 31 |

| Using Formal.....                                 | 36 |

## What is UVM?

### UVM or Formal?

- What is UVM?

- Getting Started with UVM

- Should I use Formal instead?

2

### What is UVM?

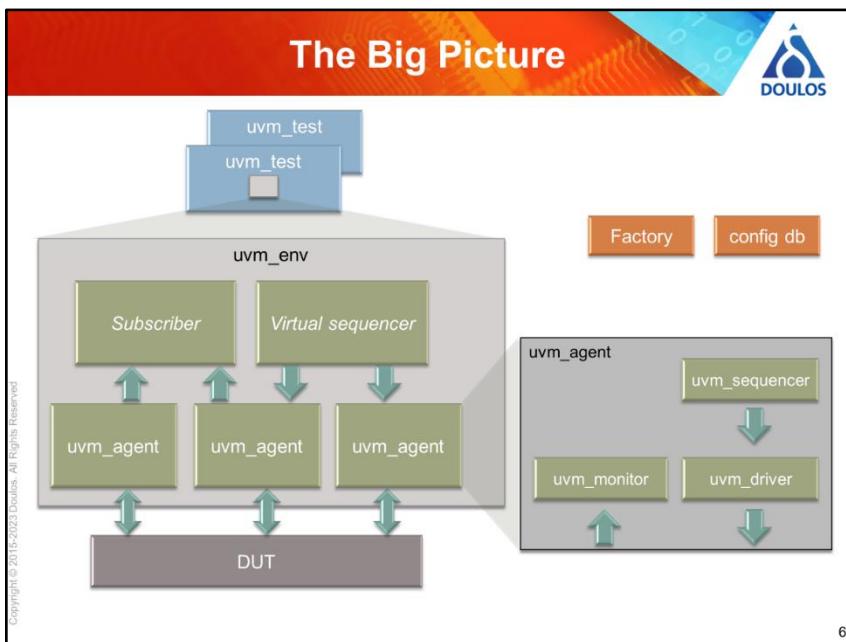

- The Universal Verification Methodology for SystemVerilog

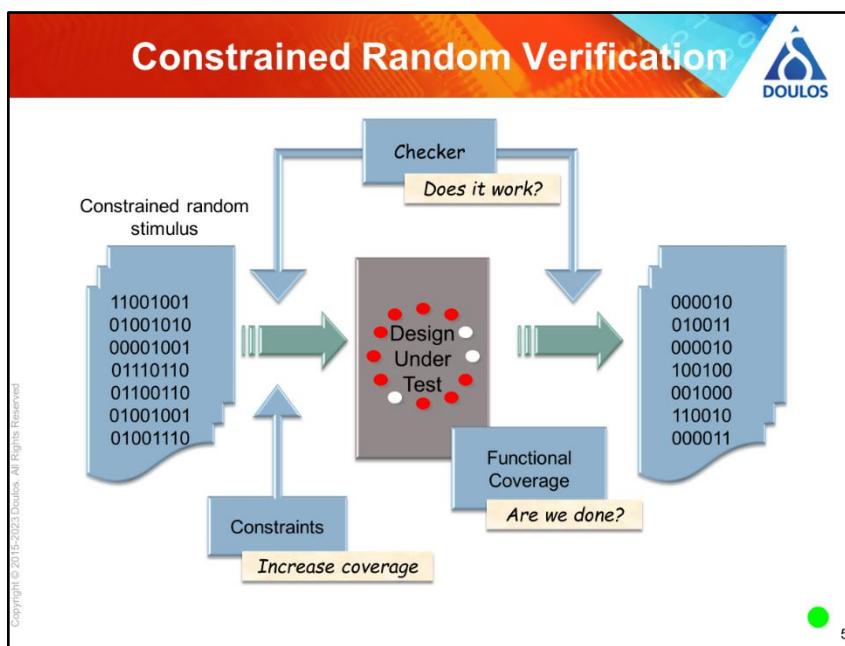

- Supports constrained random, coverage-driven verification

- An open-source (Apache 2.0) base class library

- An Accellera standard and the IEEE Standard 1800.2

- Supported by all major simulator vendors

## Why UVM?

DOULOS

- Best practice

- Consistency, uniformity, don't reinvent the wheel, avoid pitfalls

- Reuse

- Verification IP, verification environments, tests, people, knowhow

Copyright © 2015-2024 Doulos. All Rights Reserved

4

## Getting Started with UVM

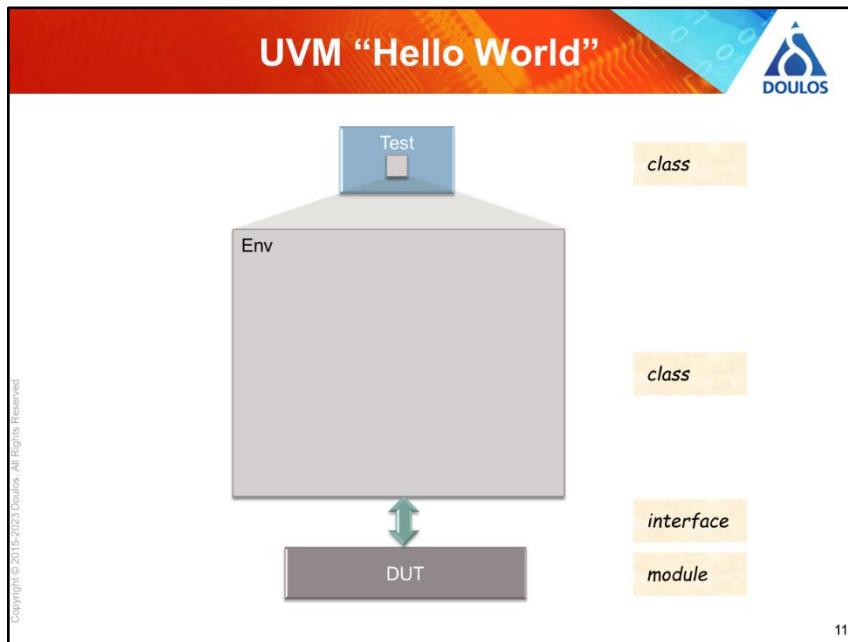

## UVM “Hello World”

### Getting Started with UVM

- UVM “Hello World”

- Making a real testbench

10

## Interface and DUT

Copyright © 2015-2024 Doulos. All Rights Reserved

```

interface dut_if;

endinterface

module dut(dut_if dif);

endmodule

module top;

...

dut_if dut_if1 ();

dut dut1 (.dif(dut_if1));

...

endmodule

```

12

## The Env

Copyright © 2015-2024 Doulos. All Rights Reserved

```

class my_env extends uvm_env;

`uvm_component_utils(my_env)

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

endclass

```

13

## The Test (1)

```

class my_test extends uvm_test;

`uvm_component_utils(my_test)

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

my_env m_env;

function void build_phase(uvm_phase phase);

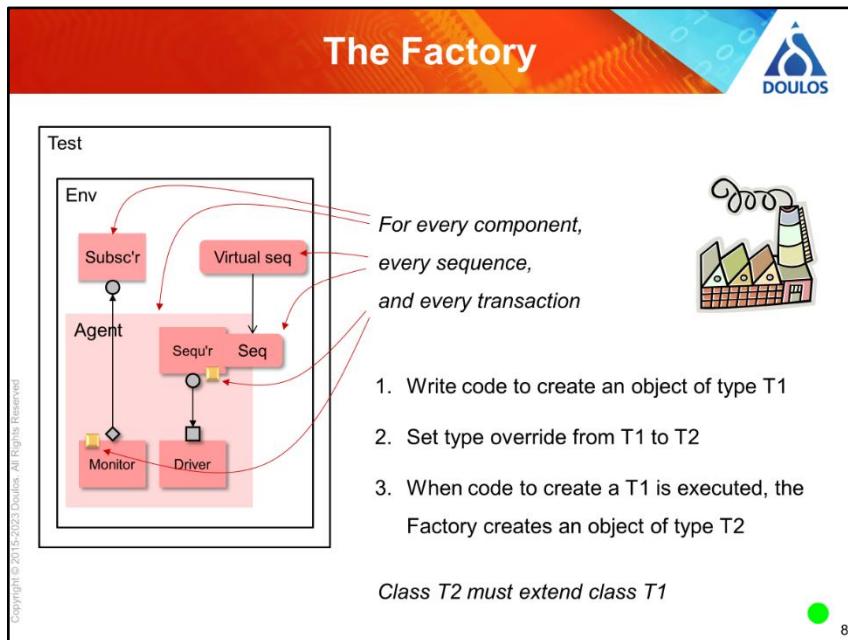

m_env = my_env::type_id::create("m_env", this);

endfunction

UVM Factory

task run_phase(uvm_phase phase);

phase.raise_objection(this);

...

endtask

endclass

```

Copyright © 2015-2024 by Doulos. All Rights Reserved

14

## The Test (2)

```

...

m_env = my_env::type_id::create("m_env", this);

endfunction

task run_phase(uvm_phase phase);

phase.raise_objection(this);

UVM Objection

#10;

`uvm_info("my_test", "Hello World", UVM_MEDIUM)

phase.drop_objection(this);

endtask

endclass

```

Copyright © 2015-2024 by Doulos. All Rights Reserved

15

## Classes in a Package

DOULOS

```

`include "uvm_macros.svh"

package my_pkg;

import uvm_pkg::*;

class my_env extends uvm_env;

`uvm_component_utils(my_env)

...

endclass

class my_test extends uvm_test;

`uvm_component_utils(my_test)

...

endclass

endpackage

```

16

## Running the Test

DOULOS

```

interface dut_if;

endinterface

module dut(dut_if dif);

endmodule

module top;

import uvm_pkg::*;

import my_pkg::*;

dut_if dut_if1 ();

dut dut1 (.dif(dut_if1));

initial

begin

run_test("my_test");

end

endmodule

```

17

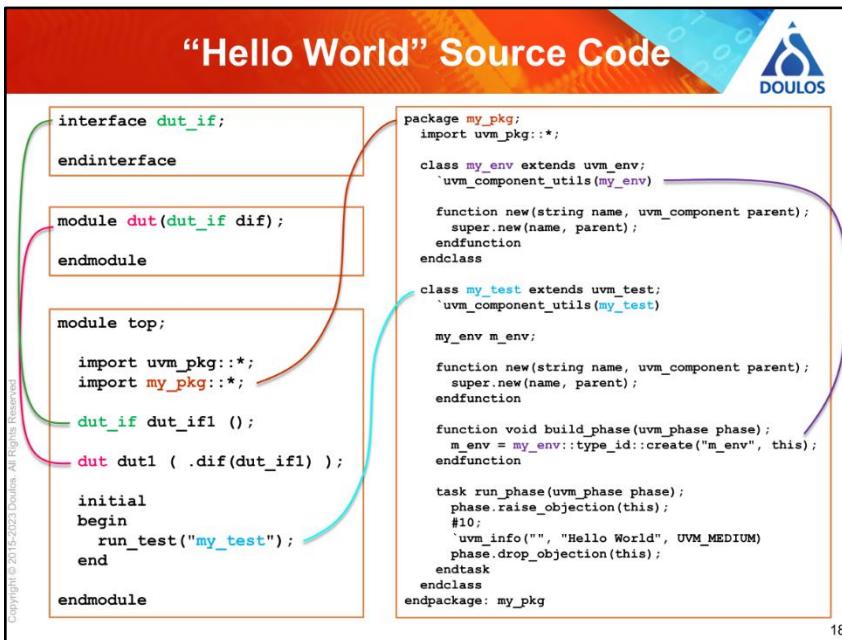

“Hello World” Source Code

```

interface dut_if;

endinterface

module dut(dut_if dif);

endmodule

module top;

import uvm_pkg::*;

import my_pkg::*;

dut_if dut_if1 ();

dut dut1 ( .dif(dut_if1) );

initial

begin

run_test("my_test");

end

endmodule

package my_pkg;

import uvm_pkg::*;

class my_env extends uvm_env;

`uvm_component_utils(my_env)

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

endclass

class my_test extends uvm_test;

`uvm_component_utils(my_test)

my_env m_env;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

m_env = my_env::type_id::create("m_env", this);

endfunction

task run_phase(uvm_phase phase);

phase.raise_objection(this);

#10;

`uvm_info("", "Hello World", UVM_MEDIUM)

phase.drop_objection(this);

endtask

endclass

endpackage: my_pkg

```

Copyright © 2015-2024 by Doulos. All Rights Reserved

18

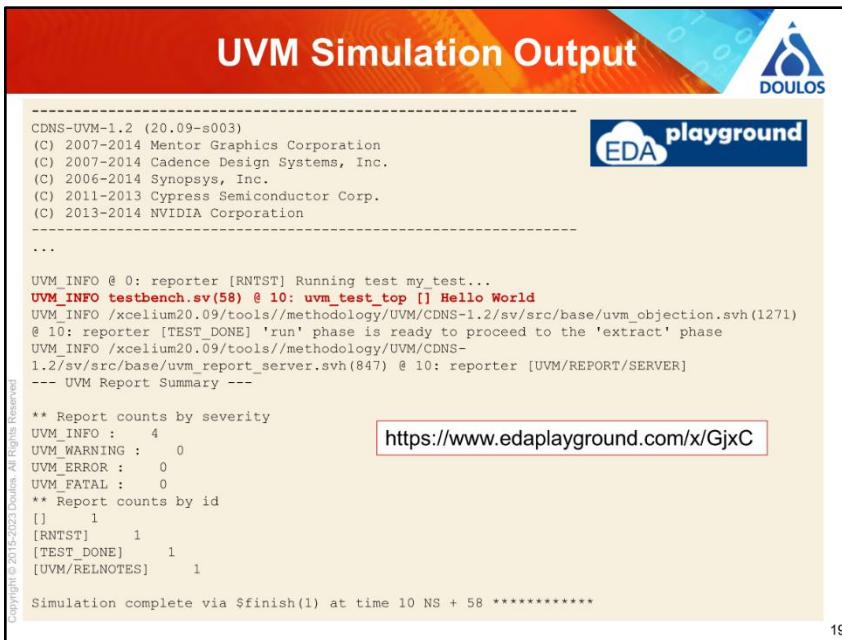

UVM Simulation Output

```

CDNS-UVM-1.2 (20.09-s003)

(C) 2007-2014 Mentor Graphics Corporation

(C) 2007-2014 Cadence Design Systems, Inc.

(C) 2006-2014 Synopsys, Inc.

(C) 2011-2013 Cypress Semiconductor Corp.

(C) 2013-2014 NVIDIA Corporation

...

UVM_INFO @ 0: reporter [RNTST] Running test my_test...

UVM_INFO testbench.sv(58) @ 10: uvm_test_top [] Hello World

UVM_INFO /xcellium20.09/tools//methodology/UVM/CDNS-1.2/sv/src/base/uvm_objection.svh(1271)

@ 10: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase

UVM_INFO /xcellium20.09/tools//methodology/UVM/CDNS-

1.2/sv/src/base/uvm_report_server.svh(847) @ 10: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 4

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[] 1

[RNTST] 1

[TEST_DONE] 1

[UVM/RELNOTES] 1

Simulation complete via $finish(1) at time 10 NS + 58 ****

```

Copyright © 2015-2024 by Doulos. All Rights Reserved

<https://www.edaplayground.com/x/GjxC>

19

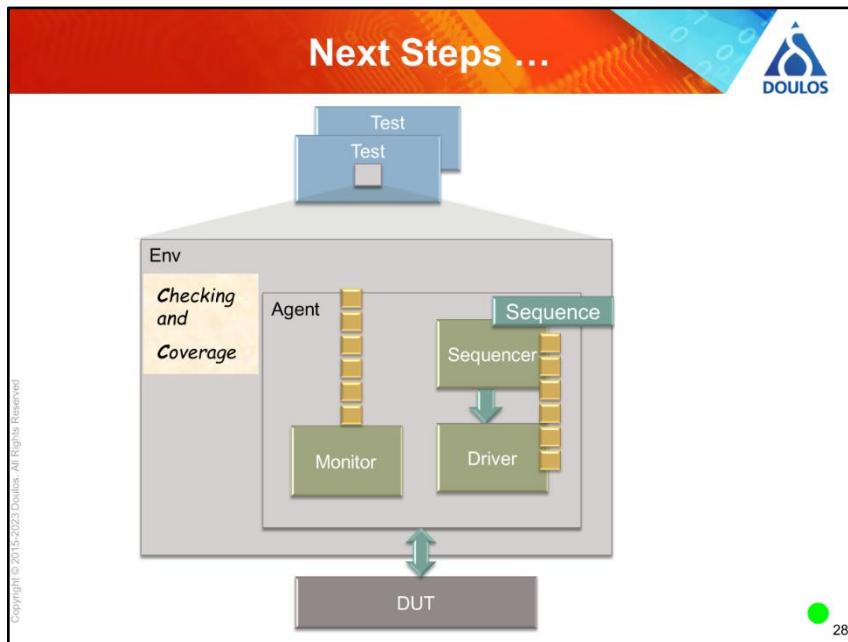

## ***Making a real testbench***

### Getting Started with UVM

- UVM “Hello World”

- Making a real testbench

DOULOS

20

### Sequence Item Class

```

class my_transaction extends uvm_sequence_item;

rand bit cmd;

rand bit [7:0] addr, data;

function new (string name = "");

super.new(name);

endfunction

`uvm_object_utils_begin(my_transaction)

`uvm_field_int(cmd, UVM_DEFAULT)

`uvm_field_int(addr, UVM_DEFAULT)

`uvm_field_int(data, UVM_DEFAULT)

`uvm_object_utils_end

endclass

```

DOULOS

21

## Sequence Class

```

class my_sequence extends uvm_sequence #(my_transaction);

`uvm_object_utils(my_sequence)

function new (string name = "");

super.new(name);

endfunction

task body;

repeat(8)

begin

`uvm_do(req)

end

endtask

endclass

```

`uvm\_do creates and sends a randomized transaction to the driver

req inherited from uvm\_sequence

22

## Sequence versus Sequencer

```

class my_sequence extends uvm_sequence #(my_transaction);

...

endclass

typedef uvm_sequencer #(my_transaction) my_sequencer;

```

A sequence runs on a sequencer

uvm\_sequence extends uvm\_sequence\_item extends uvm\_object

uvm\_sequencer extends uvm\_component extends uvm\_object

23

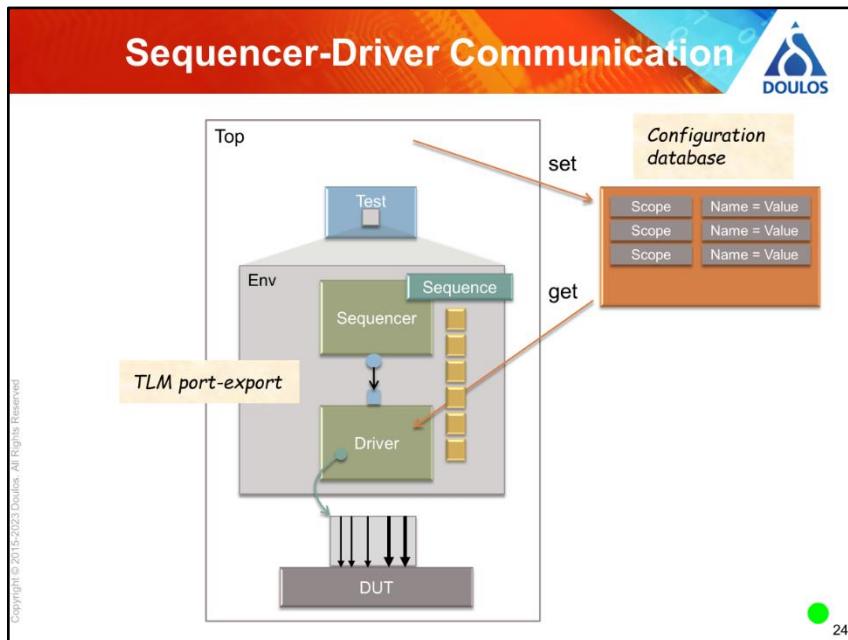

24

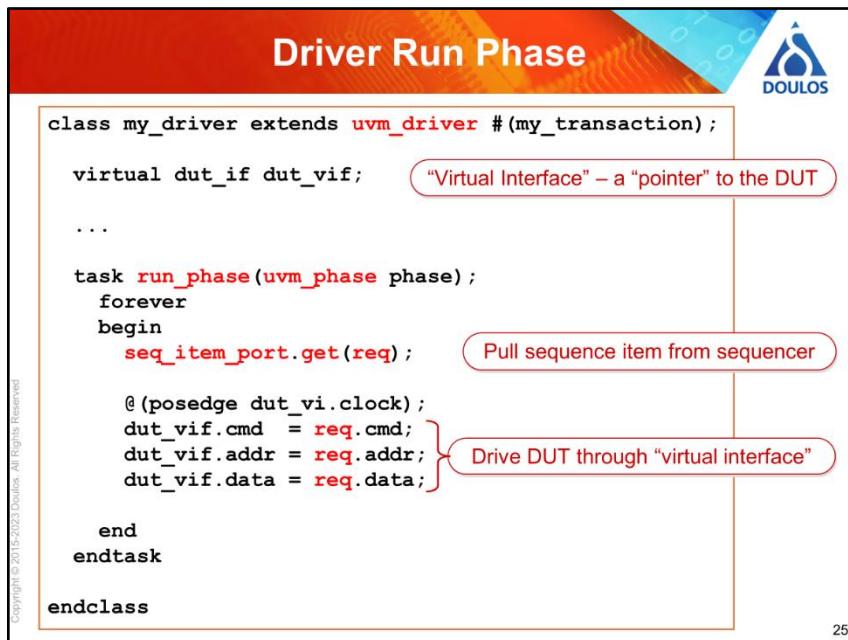

25

## Sequencer-Driver Connection

```

class my_env extends uvm_env;

`uvm_component_utils(my_env)

my_sequencer m_seqr;

my_driver    m_driv;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

m_seqr = my_sequencer::type_id::create("m_seqr", this);

m_driv = my_driver    ::type_id::create("m_driv", this);

endfunction

function void connect_phase(uvm_phase phase);

m_driv.seq_item_port.connect( m_seqr.seq_item_export );

endfunction

endclass

```

Copyright © 2015-2024 Doulos. All Rights Reserved

26

## Starting the Sequence

```

class my_test extends uvm_test;

...

my_env m_env;

...

task run_phase(uvm_phase phase);

my_sequence seq;

seq = my_sequence::type_id::create("seq");

if( !seq.randomize() )

`uvm_error("", "Randomize failed")

seq.set_starting_phase(phase);

seq.set_automatic_phase_objection(1);

seq.start( m_env.m_seqr );

endtask

endclass

```

Run phase ends when all objections have been dropped

Copyright © 2015-2024 Doulos. All Rights Reserved

27

## Should I use Formal Instead?

## **Formal is Not Hard to Use**

### **Introduction to Formal Verification**

- Formal is Not Hard to Use!

- Understanding Formal

- Under-constraining versus Over-constraining

- Using Formal

30

### **Why Formal Property Checking?**

- Bug hunting

- Assurance, particularly of complex control logic

- Checking simple things like RTL linting, connectivity, coverage waivers

- Forces you to understand the spec

- Post-silicon debug

Copyright © 2015-2024 Doulos. All Rights Reserved

31

Copyright © 2015-2024 Doulos. All Rights Reserved

## Learning to Use Formal

DOULOS

- Formal is not hard to use!

Give it your RTL code

Write some properties

32

Copyright © 2015-2024 Doulos. All Rights Reserved

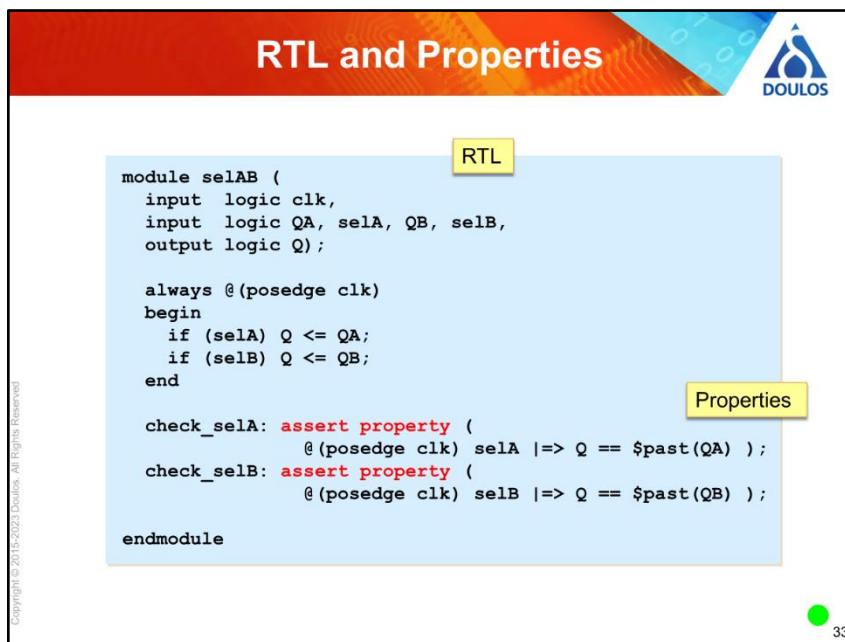

## RTL and Properties

DOULOS

RTL

```

module selAB (

input logic clk,

input logic QA, selA, QB, selB,

output logic Q);

always @ (posedge clk)

begin

if (selA) Q <= QA;

if (selB) Q <= QB;

end

check_selA: assert property (

@ (posedge clk) selA |=> Q == $past(QA) );

check_selB: assert property (

@ (posedge clk) selB |=> Q == $past(QB) );

endmodule

```

Properties

33

**Learning to Use Formal**

Give it your RTL code

Write some properties

Push the Go button

Wait for some results

Proof

Counter-example

Inconclusive

Copyright © 2015-2024 Doulos. All Rights Reserved

34

**Log Window**

| SUMMARY                      |            |

|------------------------------|------------|

| Properties Considered        | :          |

| assertions                   | : 2        |

| - proven                     | : 1 (50%)  |

| - bounded_proven (user)      | : 0 (0%)   |

| - bounded_proven (auto)      | : 0 (0%)   |

| - marked_proven              | : 0 (0%)   |

| - cex                        | : 1 (50%)  |

| - ar_cex                     | : 0 (0%)   |

| - undetermined               | : 0 (0%)   |

| - unknown                    | : 0 (0%)   |

| - error                      | : 0 (0%)   |

| covers                       | : 2        |

| - unreachable                | : 0 (0%)   |

| - bounded_unreachable (user) | : 0 (0%)   |

| - covered                    | : 2 (100%) |

| - ar_covered                 | : 0 (0%)   |

| - undetermined               | : 0 (0%)   |

| - unknown                    | : 0 (0%)   |

| - error                      | : 0 (0%)   |

Copyright © 2015-2024 Doulos. All Rights Reserved

35

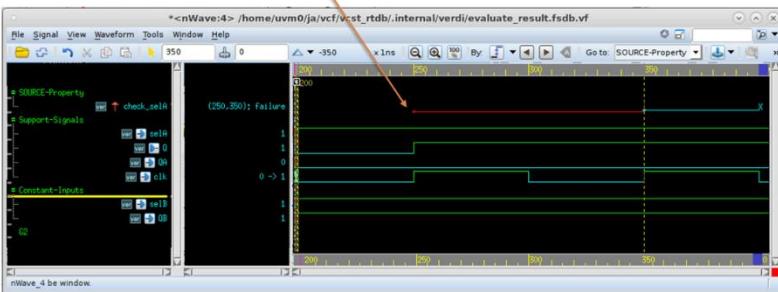

## Counter-Example (CEX)

Property fails when SelA = SelB = 1 and QA != QB

Copyright © 2015-2024 Doulos. All Rights Reserved

36

## Learning to Use Formal

- Formal is not hard to use!

Give it your RTL code

Write some properties

Push the Go button

Wait for some results

Decide what to do next

|                 |

|-----------------|

| Proof           |

| Counter-example |

| Inconclusive    |

- The problem is understanding what formal can and cannot do

Copyright © 2015-2024 Doulos. All Rights Reserved

37

## ***Understanding Formal***

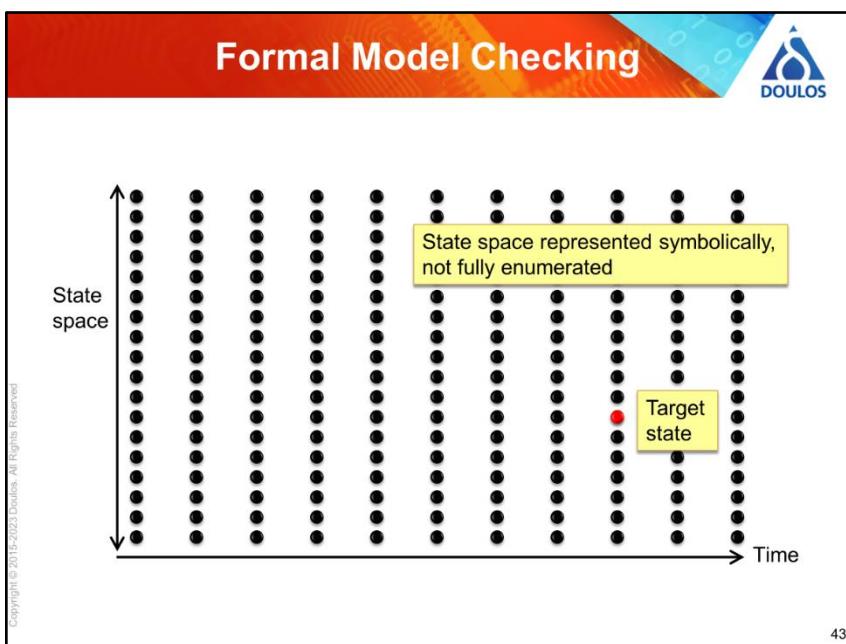

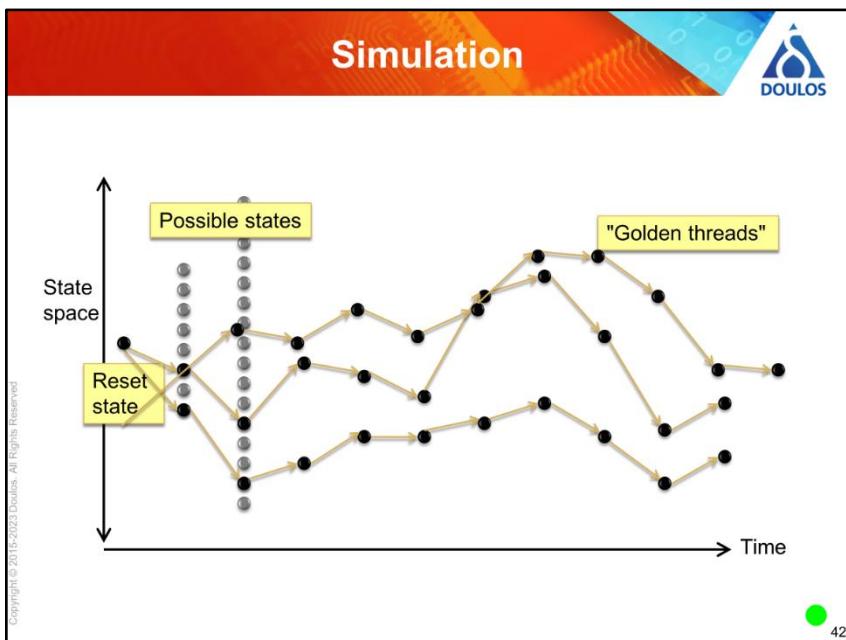

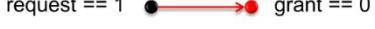

## Target State

DOULOS

```

assert property ( @(posedge clk) request |=> grant );

```

request     grant

Try to find a sequence of states that would make the assertion "fire"

request == 1     grant == 0

44

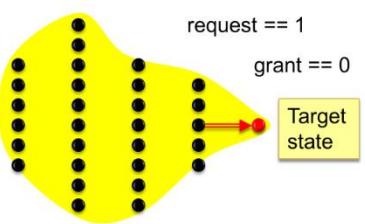

## Find a Trace that Breaks the Assert

DOULOS

State space

Time

request == 1

grant == 0

Target state

45

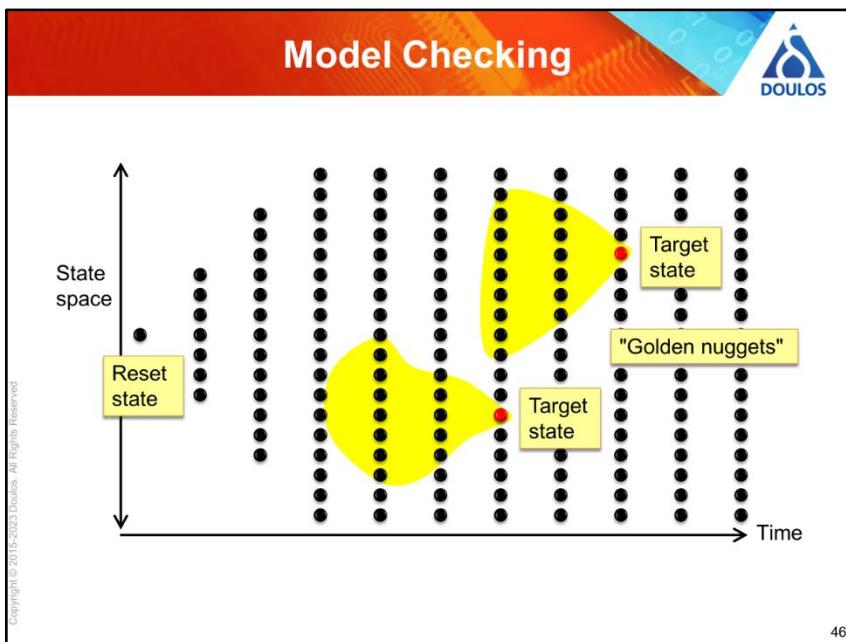

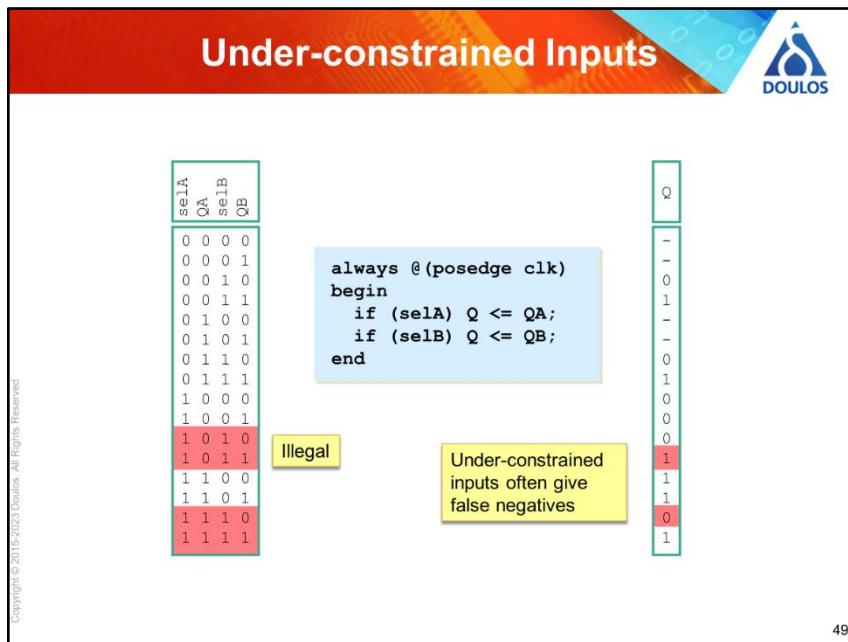

### ***Under-constraining versus Over-constraining***

**The Failing Example**

Source Pane - visualize.5

```

1 module selAB (

2   input logic clk,

3   input logic 1'b1:0

4   output logic Q;

5

6   always @ (posedge clk)

7   begin

8     if (selA) Q <= QA;

9     if (selB) Q <= QB;

10    end

11

12  check_selA: assert property (

13    @ (posedge clk) selA |>> 0 == $past(QA));

14  check_selB: assert property (

15    @ (posedge clk) selB |>> 0 == $past(QB));

16

17 endmodule

```

Inputs are under-constrained

Copyright © 2015-2024 by Doulos. All Rights Reserved

48

## Input Assume Statement

```

module selAB (

input logic clk,

input logic QA, selA, QB, selB,

output logic Q);

always @ (posedge clk)

begin

if (selA) Q <= QA;

if (selB) Q <= QB;

end

check_selA: assert property (

@ (posedge clk) selA |=> Q == $past(QA) );

check_selB: assert property (

@ (posedge clk) selB |=> Q == $past(QB) );

assume_not_11: assume property (

@ (posedge clk) !(selA & selB) );

endmodule

```

50

## Results

```

=====

SUMMARY

=====

Properties Considered      : 4

assertions                 : 2

- proven                  : 2 (100%) ←

- bounded_proven (user)   : 0 (0%)

- bounded_proven (auto)   : 0 (0%)

- marked_proven           : 0 (0%)

- cex                      : 0 (0%)

- ar_cex                  : 0 (0%)

- undetermined            : 0 (0%)

- unknown                  : 0 (0%)

- error                    : 0 (0%)

covers                     : 2

- unreachable             : 0 (0%)

- bounded_unreachable (user): 0 (0%)

- covered                  : 2 (100%)

- ar_covered              : 0 (0%)

- undetermined            : 0 (0%)

- unknown                  : 0 (0%)

- error                    : 0 (0%)

```

51

## Over-constrained Inputs

Copyright © 2015-2024 Doulos. All Rights Reserved

| selA | selB | QA | QB |

|------|------|----|----|

| 0    | 0    | 1  | 0  |

| 0    | 0    | 1  | 1  |

| 0    | 1    | 1  | 0  |

| 0    | 1    | 1  | 1  |

| 1    | 0    | 0  | 0  |

| 1    | 0    | 0  | 1  |

| 1    | 1    | 0  | 0  |

| 1    | 1    | 0  | 1  |

|   |   |   |   |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 0 | X | 1 |

| 0 | X | 0 | 0 |

| 0 | 1 | 0 | 1 |

```

always @(posedge clk)

begin

if (selA) Q <= QA;

if (selB) Q <= QB;

end

assume property (

@(posedge clk) selA != selB );

```

| Q |

|---|

| 0 |

| 1 |

| 0 |

| 1 |

| 0 |

| 0 |

| 1 |

| 1 |

Overconstrained inputs can give false positives

52

## Verifying Assumptions with Cover

Copyright © 2015-2024 Doulos. All Rights Reserved

```

always @(posedge clk)

begin

if (selA) Q <= QA;

if (selB) Q <= QB;

end

check_selA: assert property (

@(posedge clk) selA |=> Q == $past(QA) );

check_selB: assert property (

@(posedge clk) selB |=> Q == $past(QB) );

assume_not_11: assume property (

@(posedge clk) selA != selB );

cover_00: cover property (

@(posedge clk) !selA & !selB );

```

Check input not over-constrained

53

Copyright © 2015-2024 Doulos. All Rights Reserved

## Results

**SUMMARY**

| Properties Considered        | Value          |

|------------------------------|----------------|

| assertions                   | : 2            |

| - proven                     | : 2 (100%)     |

| - bounded_proven (user)      | : 0 (0%)       |

| - bounded_proven (auto)      | : 0 (0%)       |

| - marked_proven              | : 0 (0%)       |

| - cex                        | : 0 (0%)       |

| - ar_cex                     | : 0 (0%)       |

| - undetermined               | : 0 (0%)       |

| - unknown                    | : 0 (0%)       |

| - error                      | : 0 (0%)       |

| covers                       | : 3            |

| - unreachable                | : 1 (33.3333%) |

| - bounded_unreachable (user) | : 0 (0%)       |

| - covered                    | : 2 (66.6667%) |

| - ar_covered                 | : 0 (0%)       |

| - undetermined               | : 0 (0%)       |

| - unknown                    | : 0 (0%)       |

| - error                      | : 0 (0%)       |

54

Copyright © 2015-2024 Doulos. All Rights Reserved

## Verifying Assumptions with Cover

```

always @ (posedge clk)

begin

if (selA) Q <= QA;

if (selB) Q <= QB;

end

check_selA: assert property (

@ (posedge clk) selA |=> Q == $past(QA) );

check_selB: assert property (

@ (posedge clk) selB |=> Q == $past(QB) );

assume_not_11: assume property (

@ (posedge clk) !(selA & selB)); Fix the assumption

cover_00: cover property (

@ (posedge clk) !selA & !selB );

```

55

## When things go wrong

Copyright © 2015-2024 by Doulos. All Rights Reserved

- False negatives due to assertion bugs – debug CEX

- False negatives due to under-constrained inputs – debug CEX

- False positives due to over-constrained inputs – covers or simulation

- False positives due to insufficient assertions – assertion coverage

- False positives due to loose assertions – a challenge!

56

## Using Formal

### Introduction to Formal Verification

- Formal is Not Hard to Use!

- Understanding Formal

- Underconstraining versus Overconstraining

- Using Formal

57

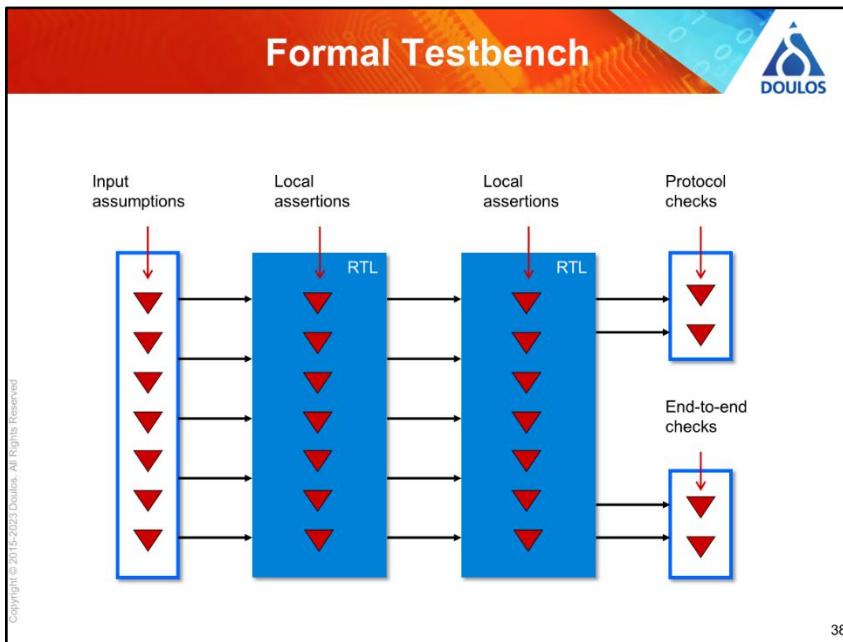

## Formal Use Model

- Use formal at block level, even before simulation

- Find bugs before simulation

- Forced to think about the spec

- Properties carried around with the RTL

- Distinguish between local (simple) and end-to-end assertions

- Simple assertions are easy to write / understand / prove / debug

- End-to-end assertions are sometimes the most valuable

58

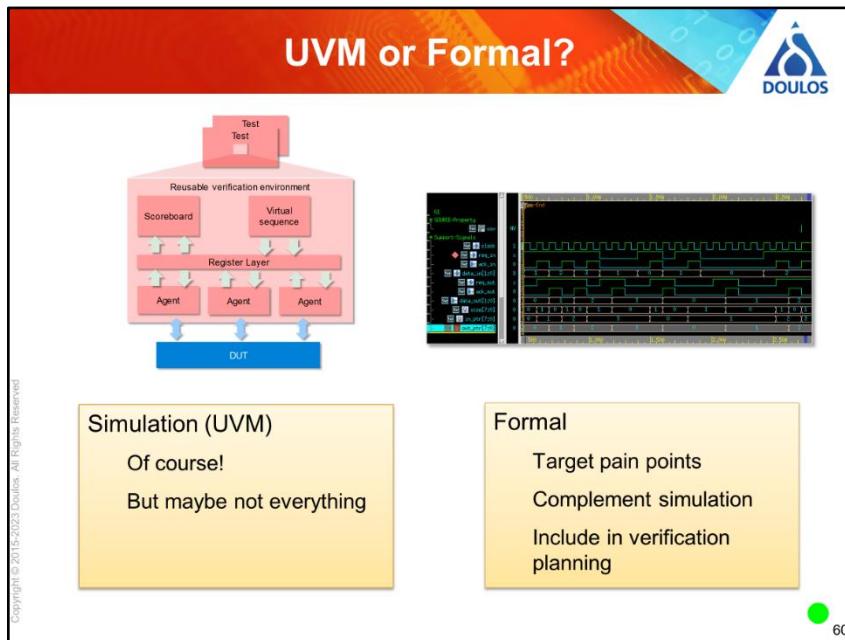

## Formal Complements Simulation

- Formal and simulation have different strengths and blind spots

- Formal will find bugs missed by simulation, and vice versa

- Formal encourages a different mindset from simulation

59

[www.doulos.com](http://www.doulos.com)