## Auto-Generation of Verification Infrastructure for IP / SoC

Presenter : Nikita Gulliya Product Engineer- Agnisys

## The State of Verification in 2023

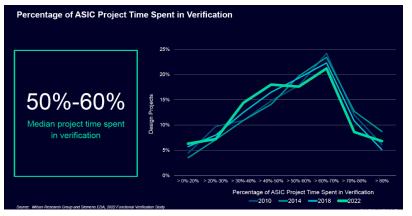

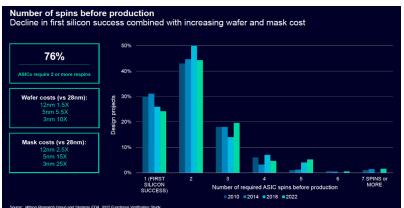

- Most development time spent in verification 60%-70%

- However, respins per project still increasing

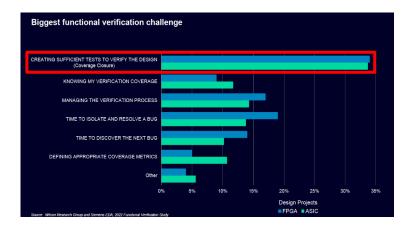

- Greatest verification challenge (by far)...

creating sufficient tests

Source: Wilson Research Group 2022, courtesy Siemens EDA

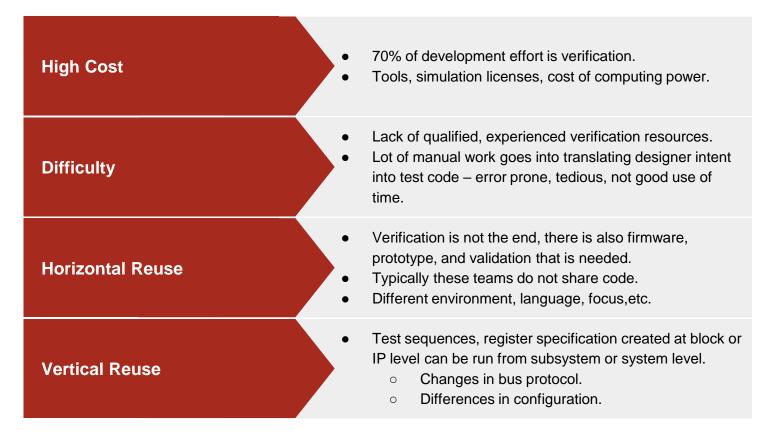

## **Verification Challenges**

Solution : Auto Generation of Verification infrastructure

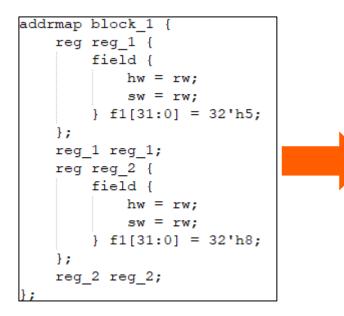

## **Generate Verification Infra from what?**

Single Golden Specification

Register Specification SystemRDL, IP-XACT, ... Sequences Specification PSS, ... Design Specification FSM, Datapath, ... Connection Specification Tcl, Excel, ...

# **Register Specification** Automation

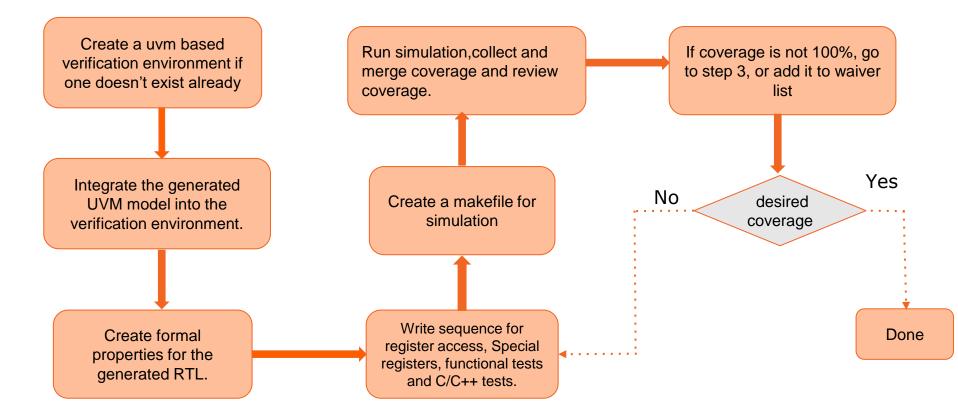

# What's next after UVM RAL Model generation?

# **Outputs from Register specification**

## Test Generation for registers

- Register model corresponding to the DUT specification with register focused cover groups

- Positive Test Sequences including tests for special registers and wide variety of register accesses.

- Reset Sequences

- Negative Test Sequences

- UVM Verification Env

Gets you close to 100% coverage

## Assertion Generation for registers

- SV Properties and Assertions for register access policies and compliance to bus protocols

- Top-level file to bind the DUT RTL as well as thirdparty design IP with the assertions.

- Makefile or Tcl command scripts

Independent Verification required by Functional Safety

### **Verification Env for registers**

- Generates the design components and corresponding RAL

- Generates standard sequences for registers

- Generates custom test sequence and user checker events

- Complete and fully-connected UVM test environment including components, hdl\_paths, covergroups, constraints and illegal bins

- "Makefile" for various simulators

High-level test creation which runs in the UVM environment

## **More Features and Capabilities**

- A complete solution for

- Complete UVM test bench environment

- Automatic tests sequence for registers

- Custom test sequences and checker events for user tests

- Formal assertions based on design intent and registers

- Generate complete UVM infrastructure for a push-button verification with integrated RAL model and DUT

- Support for **multiple buses** such as AXI4Full, AXILite, AHB, APB etc.

- Out-of-the box ~100% coverage with register focused cover groups

- Automatic test sequences for special registers and wide variety of register accesses

- Automatic assertions for registers (including special registers), register access policies and bus compliance

- Generate "**Makefile**" (for Cadence Xcelium, Mentor Questa, and Aldec Riviera Pro) to run simulations and collect results from the database for different widely used simulators

- Provide **auto mirroring** of registers to continuously monitor the hardware events occurring on the registers

- Reduce the required verification effort by automatically generating ~30% of the verification code making it an efficient and error free flow

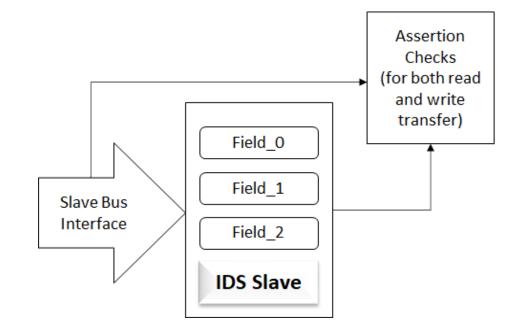

# **Automatic Assertion Generation**

### What type of assertions are generated?

Assertions based on specification for different RTL behavior

- Assertions for register accesses

- Assertions for external RTL interface

- Assertions for special registers

- Assertions for special IDS associated UDPs

- Assertions for clock domain crossing (CDC)

- Assertions for functional safety RTL design

- System level assertions

- Assertions to check RTL ports connections

- Topology assertions

- Multi-master design assertions

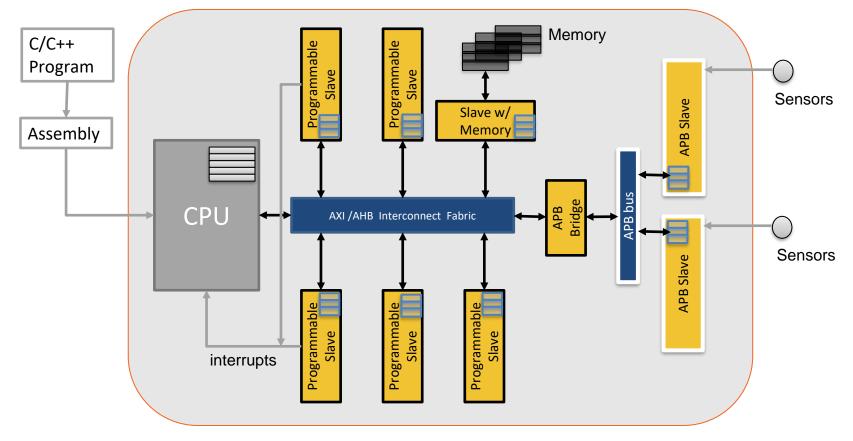

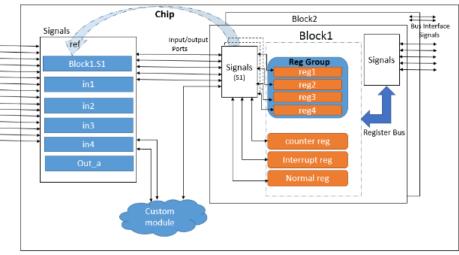

# Design & Connection Specification Automation

## **A Typical SoC**

## **Assertions for IDS generated Register RTL**

### Input RDL to generate assertions

### Generated RTL for Input RDL

```

input reg 2 wr valid;

input reg 2 rd valid;

// HW WRITE-ABLE SIGNAL FOR EACH FIELD

input reg 2 fl in enb ;

// FIELD : F1

// BUFFER SIGNAL FOR EACH FIELD

input [31 : 0] reg 2 fl q ; // FIELD : Fl

// READ DATA SIGNAL FOR EACH FIELD

input [31 : 0] reg 2 fl r ;

// FIELD : F1

// HW WRITE DATA SIGNAL FOR EACH FIELD

input [31 : 0] reg_2_fl_in ;

// FIELD : F1

input pclk;

input presetn;

input psel;

input penable;

input pwrite;

input [2 : 0] pprot;

input [bus width/8-1 : 0] pstrb;

input [bus width-1 : 0] pwdata;

input [addr width-1 : 0] paddr;

input pready;

input [bus width-1 : 0] prdata;

input pslverr;

// Sequences

sequence apb read(bit [addr width-1 : 0] addr ,bit [bus width/8-1:0] psizein);

( paddr == addr && pwrite == 0 && pstrb == psizein && psel == 1 && penable == 1 && pready == 1 );

endsequence

sequence apb write(bit [addr width-1 : 0] addr ,bit [bus width/8-1:0] psizein);

( paddr == addr && pwrite == 1 && pstrb == psizein && psel == 1 && pready == 1 );

endsequence

```

### **Assertion Generation from Connectivity Spec**

### Input python script to generate assertions

##....To clean IDS-Integrate workspace off previous blocks and instances......##

soc\_clean()

##.....To display of output messages to avoid cluttering in IDS-Integrate......##

soc\_set("debug")

##.....soc\_add Api to add instances of blocks in the container/wrapper block...##

soc\_add(parent="chip", name="block", inst="B\_inst")

##.....soc\_library Api to show the hierarchy of the Design textually......##

soc\_library("all")

##...soc\_connect Api is to connect blocks by using a bus/ports/Bus interface....##

soc\_connect(source="chip", dest="B\_inst",bus="apb" )

##...soc\_generate api to generate different outputs(arv\_formal(assertions),SV)..##

soc\_generate("compact",out=["sv","arv\_formal"],dir="ids")

Generated output assertions by IDS-Integrate

clocking cb @(posedge pclk);

property block\_connection\_checkl; B\_inst.pclk |-> pclk; endproperty

property block\_connection\_check2; B\_inst.paddr |-> paddr; endproperty

property block\_connection\_check3; disable iff (!presetn) B\_inst.prdata |-> prdata; endproperty

property block\_connection\_check4; B\_inst.psel |-> psel; endproperty

property block\_connection\_check5; B\_inst.penable |-> penable; endproperty

property block\_connection\_check6; B\_inst.pwdata |-> pwdata; endproperty

property block\_connection\_check7; B\_inst.pwrite |-> pwrite; endproperty

property block\_connection\_check8; B\_inst.pprot |-> pprot; endproperty

property block\_connection\_check9; B\_inst.pready |-> pready; endproperty property block\_connection\_check10; B\_inst.pstrb |-> pstrb; endproperty

property block\_connection\_checkll; B\_inst.presetn |-> presetn; endproperty

property block\_connection\_checkl2; B\_inst.pslverr |-> pslverr; endproperty

#### endclocking

endmodule

block\_connection\_checkl\_assert : assert property(cb.block\_connection\_checkl); block\_connection\_check2\_assert : assert property(cb.block\_connection\_check2); block\_connection\_check3\_assert : assert property(cb.block\_connection\_check3); block\_connection\_check4\_assert : assert property(cb.block\_connection\_check4); block\_connection\_check5\_assert : assert property(cb.block\_connection\_check5); block\_connection\_check6\_assert : assert property(cb.block\_connection\_check6); block\_connection\_check8\_assert : assert property(cb.block\_connection\_check6); block\_connection\_check8\_assert : assert property(cb.block\_connection\_check6); block\_connection\_check8\_assert : assert property(cb.block\_connection\_check8); block\_connection\_check8\_assert : assert property(cb.block\_connection\_check8); block\_connection\_check10\_assert : assert property(cb.block\_connection\_check10) block\_connection\_check11\_assert : assert property(cb.block\_connection\_check12)

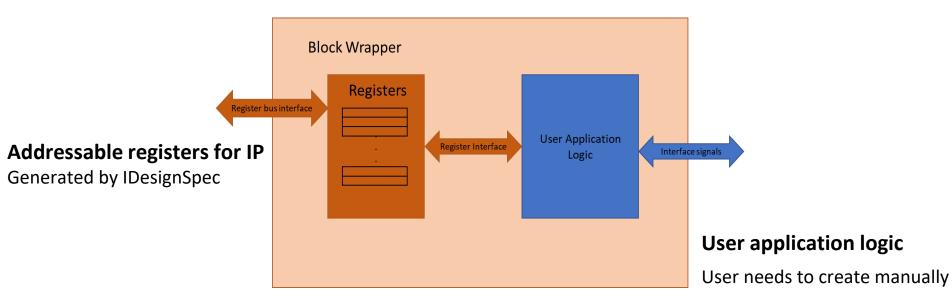

# User application logic connected to register map

# **User Application Logic Constructs**

- User logic constitutes mainly of:

- State Machine

- Assigns with combinatorial logic

- Signals input/output

- Sequential Elements/Data Path

DAIA\_FIELD

# **Additional User Specification in form of Templates**

- Create a formal specification of the requirements

- Automatically generates:

- UVM prediction model

- UVM test sequences for complete coverage

- Other collaterals are possible

- Deadlock detection

- Documentation

- In addition, RTL and SystemC models can be generated

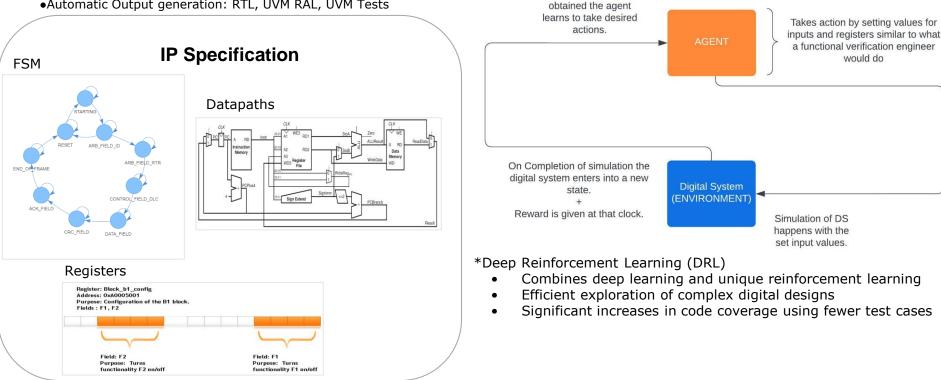

# **Tackling Verification using Al**

- •Alleviates significant verification burden: automatic test generation using \*DRL (uniquely enabled by Agnisys reward

- function) for registers, FSM, datapath & interconnect

- •100% Code / Functional Coverage based on Coverage Goals

- •Automatic Output generation: RTL, UVM RAL, UVM Tests

Based on the reward

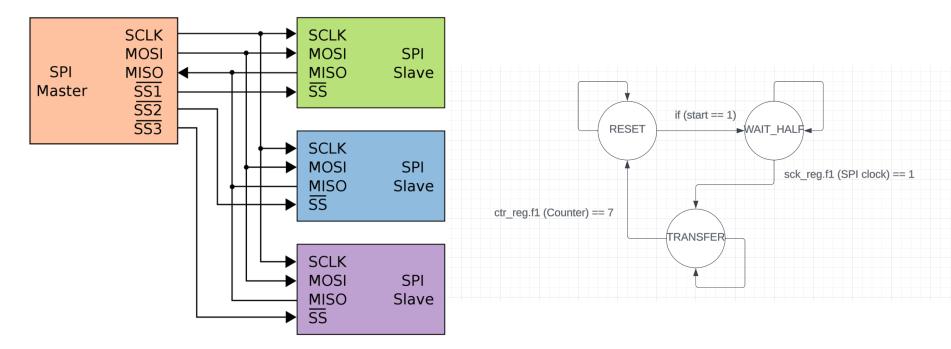

# **SPI Design FSM and Block Diagram**

# **SPI Design Coverage Results**

### **Coverage Summary By Instance:**

| Scope ∢    | TOTAL 🖣 | Statement | Branch ୶ | FEC Expression < | Toggle 🛛 | FSM State ୶ | FSM Trans ୶ |

|------------|---------|-----------|----------|------------------|----------|-------------|-------------|

| TOTAL      | 77.59   | 97.08     | 97.43    | 88.09            | 42.87    | 100.00      | 25.00       |

| spi_latest | 79.14   | 96.77     | 97.29    | 93.93            | 45.22    | 100.00      | 25.00       |

| apb        | 67.38   | 100.00    | 100.00   | 66.66            | 2.85     |             |             |

### Local Instance Coverage Details:

#### **Recursive Hierarchical Coverage Details:**

| Total Coverage:           |      |      |          |          | 52.60%  | 79.14%     | Total Coverage:    |        |      |          |          | 50.80%  |

|---------------------------|------|------|----------|----------|---------|------------|--------------------|--------|------|----------|----------|---------|

| Coverage<br>Type ∢        | Bins | Hits | Misses 🛛 | Weight ୶ | % Hit ∢ | Coverage 🛛 | Coverage<br>Type ∢ | Bins ୶ | Hits | Misses 🛛 | Weight ୶ | % Hit   |

| <u>Statements</u>         | 93   | 90   | 3        | 1        | 96.77%  | 96.77%     | Statements         | 103    | 100  | 3        | 1        | 97.08%  |

| <b>Branches</b>           | 74   | 72   | 2        | 1        | 97.29%  | 97.29%     | Branches           | 78     | 76   | 2        | 1        | 97.43%  |

| <u>FEC</u><br>Expressions | 33   | 31   | 2        | 1        | 93.93%  | 93.93%     | FEC<br>Expressions | 42     | 37   | 5        | 1        | 88.09%  |

| <u>Toggles</u>            | 1194 | 540  | 654      | 1        | 45.22%  | 45.22%     | Toggles            | 1264   | 542  | 722      | 1        | 42.87%  |

| <u>FSMs</u>               | 7    | 4    | 3        | 1        | 57.14%  | 62.50%     | FSMs               | 7      | 4    | 3        | 1        | 57.14%  |

| <u>States</u>             | 3    | 3    | 0        | 1        | 100.00% | 100.00%    | States             | 3      | 3    | 0        | 1        | 100.00% |

# Sequence Specification Automation

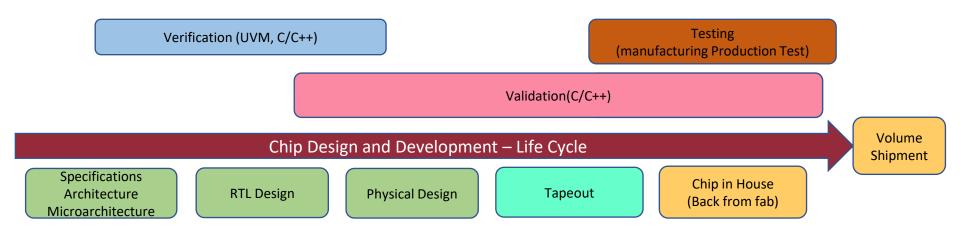

# What is Verification?

# What is Validation?

- A process to test a design is against a given specification to ensure its functional correctness

- Functional coverage using coverpoints, constraints and randomization

- Includes Simulation along with Formal, Emulation and Prototyping

- A typical SV-UVM based environment is needed

- A process in which the manufactured design (chip) is tested for all functional correctness in a lab setup

- Bare-Metal Environment with emulation of real processor and IP's

- Software test mainly c-tests including :

- Automated C-tests

- Custom C-tests

# **SoC Verification and Validation**

- Is the testing/ verification of a Design against a given specification before actual tape-out to ensure functional correctness

- Can be during Design development or start from early Design architecture/ microarchitecture definition

- Involves validating the Chip-in-a-System level environment with real software running on the hardware

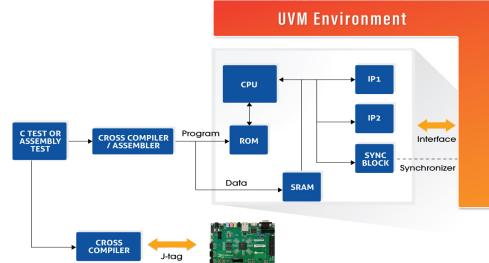

## **Bare-Metal Verification**

- The "bare metal environment" include not only the IPs but also the CPU in the simulation

- Bare-metal programming means writing an application directly on your hardware without using an external application programming interface or any operating system

- The tests are written in C language and are compiled and run on the CPU

- Salient features

- System level UVM-C mixed verification environment built around RISC-V VeeR core

- Automatic generation of C based tests from Register Layer

- C tests synced with UVM tests

- Custom C/UVM tests

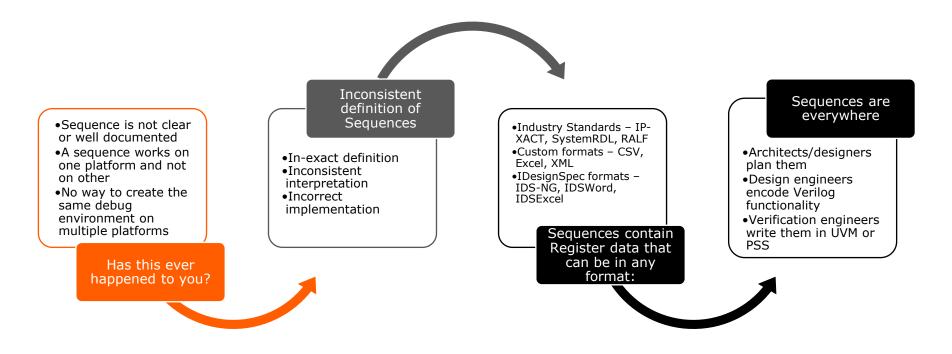

# **Challenges Development Teams face with Sequences**

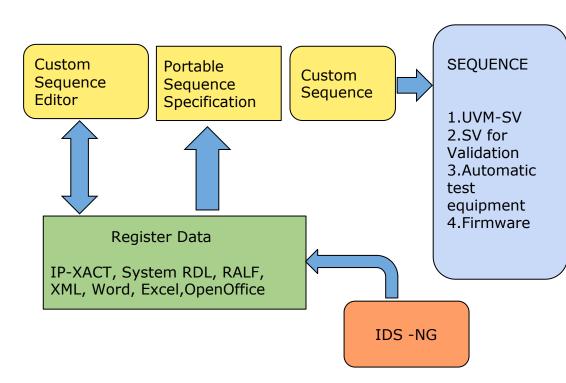

# **Custom Sequence Generation**

- IDS-Validate<sup>™</sup> enables users to describe the programming and test sequences of a device and automatically generate sequences ready to use from an early design and verification stage to post silicon validation

- Centralize creation of sequences from a single specification and generate various output formats for multiple SoC teams.

- UVM, System Verilog, C, TCL, CSV or MATLAB

- HTML

- Platform

- Specify portable sequences for multiple IPs at a higher level in-sync with the register specification.

- Use register descriptions in standard formats such as IP-XACT, SystemRDL, RALF or leverage IDesignSpec integrated flow to use the register data.

# **PSS Support**

- PSS 2.0 is a new\* industry standard created by Accellera

- Agnisys has been a member and contributed to it

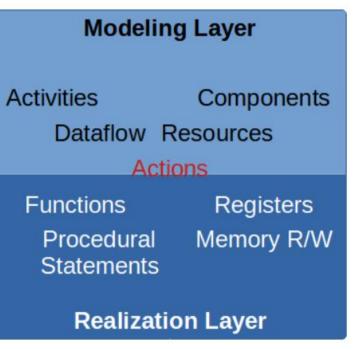

We are an expert in creating the Realization layer Widest/Most comprehensive Register/Memory definition Pioneer in Sequence/Functions for IP/SoC

What we offer

- Use PSS (or Excel, Python, GUI (NG)) to create Golden Spec for Sequences

- Generate C functions and UVM Sequences

Benefits

• Single Golden Source for Registers and Sequences reduces Time to Market, improves quality

Copyright 2014-2023 Matthew Ballance. All Rights Reserved

### **Conclusion:**

Auto Generation of 50%-60% of Verification Collateral is possible today. This number will only grow with Specification Automation and Al.