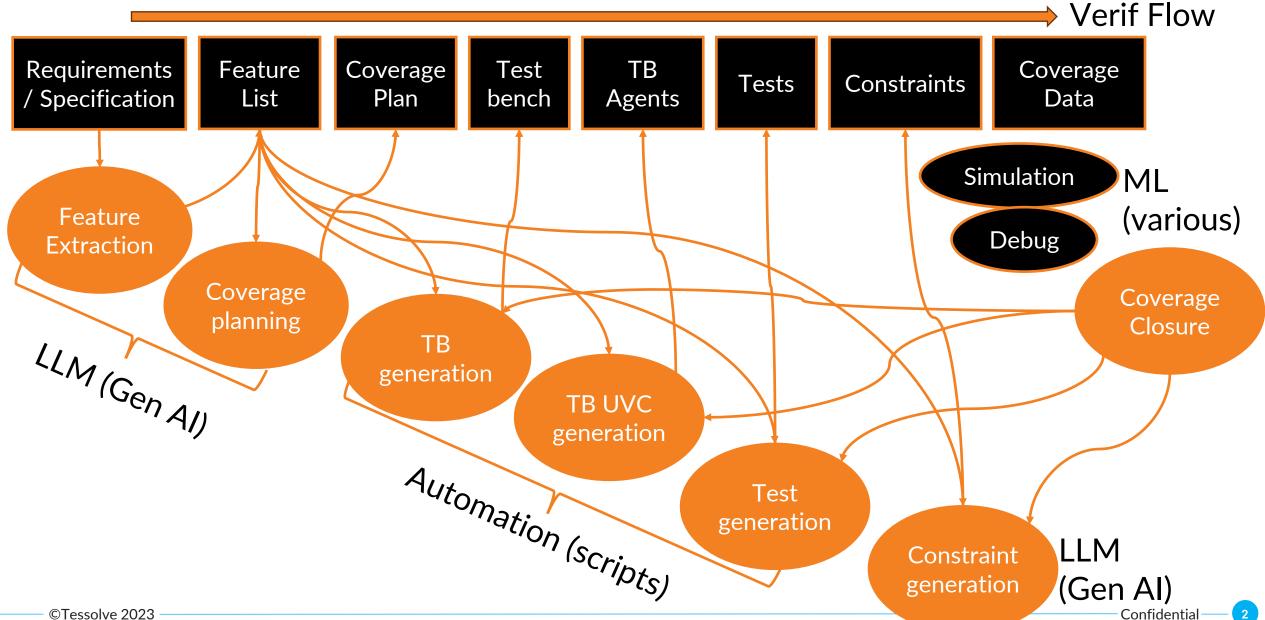

# Automation/Al Efficiencies in Verification

# Marmik Soni and Mike Bartley, Tessolve

Chip Design

**Test Engineering**

Hardware Design

**Embedded Systems**

## AI/ML Experiments in IP Verification

# Ex: Xilinx Synchronous FIFO V3.0

Using LLM to Specification for Feature Extractio

## Input = PDF<sup>1</sup> Specification

## output = table of I/O

| Signal Name     | I/O    | Description                                                              |  |  |  |

|-----------------|--------|--------------------------------------------------------------------------|--|--|--|

| DIN[N:0]        | Input  | Data Input                                                               |  |  |  |

| WR_EN           | Input  | Write Enable (request)                                                   |  |  |  |

| WR_ACK          | Output | Write Acknowledge: Handshake signal indicates successful write operation |  |  |  |

| WR_ERR          | Output | Write Error: Handshake signal indicates unsuccessful write operation     |  |  |  |

| RD_EN           | Input  | Read Enable (request)                                                    |  |  |  |

| RD_ACK          | Output | Read Acknowledge: Handshake signal indicates successful read operation   |  |  |  |

| RD_ERR          | Output | Read Error: Handshake signal indicates unsuccessful read operation       |  |  |  |

| CLK             | Input  | Clock for read and write operations                                      |  |  |  |

| SINIT           | Input  | Synchronous initialization of all FIFO functions, flags, and pointers    |  |  |  |

| DOUT[N:0]       | Output | Data Output                                                              |  |  |  |

| FULL            | Output | Full Flag: Indicates that no additional writes can be performed          |  |  |  |

| EMPTY           | Output | Empty Flag: Indicates that no data is present                            |  |  |  |

| DATA_COUNT[C:0] | Output | Data Count: Vector                                                       |  |  |  |

### output = list of features

#### **Features to be Verified:**

#### **Data Read and Write Operations:**

Verify that data presented at the data-input port (DIN) is correctly written into the FIFO on a rising clock edge when the write-enable input (WR\_EN) is high.

Verify that data can be read out of the FIFO via the data-output port (DOUT) in the order it was written by asserting read-enable (RD\_EN) prior to a rising clock edge.

### **Status Flags:**

Verify the behavior of the memory-full status output (FULL) to indicate when no more empty locations are available in the internal memory.

Verify the behavior of the memory-empty status output (EMPTY) to indicate when no more data resides in the internal memory.

### **Invalid Request Handling:**

Verify that the FIFO status is not corrupted by invalid read or write requests.

.....

## Input = PDF<sup>1</sup> Specification

# Output = Simple directed TB

```

Output = Coverage

```

```

module tb fifo;

V/ Declare signals and variables for the testbench

logic clock; logic reset;

logic wr_en; logic rd_en;

logic [DATA_WIDTH-1:0] data_in;

logic [DATA_WIDTH-1:0] data_out;

// Instantiate the FIFO module

fifo #(DATA WIDTH, FIFO DEPTH) dut (.clock(clock), .....)

always #5 clock = ~clock; // Initialize signals and variables

initial begin clock = 0;

reset = 1;

wr en = 0;

rd\ en=0;

data in = 0; // Reset the FIFO

#10 reset = 0; // Write data into the FIFO

#20; wr en = 1;

data in = 8'hFF; // Example data value

#10; wr en = 0; // Read data from the FIFO

#30; rd en = 1;

#10; rd en = 0;

#10; $finish;

end // Display the output data

always @(posedge clock)

beain

$display("Data Out: %h", data_out);

end

endmodule

```

# **Assertion for FIFO empty and full signals** *assert property (fifo\_inst.EMPTY* |-> !fifo\_inst.FULL);

```

covergroup fifo coverage @(posedge clk);

// Declare coverpoints for different events

coverpoint data count {

bins empty = \{0\};

bins non empty = [1:\$];

coverpoint write enable;

coverpoint read enable;

coverpoint full;

coverpoint almost full;

coverpoint almost empty;

// Declare cross coverage

cross data count, write enable;

cross data count, read_enable;

cross full, write enable;

cross almost full, write_enable;

cross almost empty, read enable;

endgroup

```

# **CPU Register Extraction -Gen Al**

Input = PDF |

Specification

# Output = Register Details

| Sr. No. | Register Name           | Addres<br>s | Reg Size | Access | Importance | Functionality                                                            |  |

|---------|-------------------------|-------------|----------|--------|------------|--------------------------------------------------------------------------|--|

| 1       | ,                       | 0x3XX       | 32 bits  | R/W    | High       | Stores the 32-bit secret key value used for secure operations.           |  |

| 2       |                         | 0x3XX       | 32 bits  | R/W    | High       | Stores the 32-bit decryption key value used for secure operations.       |  |

| 3       | Register                | 0x3XX       | 32 bits  | R/W    | Medium     | Contains interrupt and debug-related information for host communication. |  |

| 4       |                         | 0x3XX       | 1 bit    | R      | Medium     | Indicates the presence of an interrupt condition.                        |  |

| 5       |                         | 0x7XX       | 1 bit    | R/W    | Medium     | Enables or disables interrupts.                                          |  |

| 6       | No,                     | 0x8XX       | 1 bit    | R/W    | Medium     | Selects the key size (128-bit or 256-bit).                               |  |

| 7       | nted                    | 0x7XX       | 1 bit    | R      | Medium     | Indicates whether debug access is granted or not.                        |  |

| 8       | H                       | 0x3XX       | 1 bit    | R/W    | Medium     | Clears the host interrupt.                                               |  |

| 9       | External Ct             | 0x5XX       | 32 bits  | R      | Low        | Connected to the chip top for external status information.               |  |

| 10      | Lanal Status Register 1 | 0x5XX       | 32 bits  | R      | Low        | Connected to the chip top for external status information.               |  |

| 11      | s Register 2            | 0x5XX       | 32 bits  | R      | Low        | Connected to the chip top for external status information.               |  |

| 12      | Lifecycle Register      | 0x5XX       | 32 bits  | R      | Low        | Contains the lifecycle word read from OTP memory.                        |  |

| 13      | C100                    | 0x6XX       | 32 bits  | R/W    | Low        | Controls the reset and enable signals for the subsystem.                 |  |

| 14      | Status<br>Register      | 0x6XX       | 32 bits  | R/W    | Low        | Control and status register with undefined usage.                        |  |

Confidential Confidential

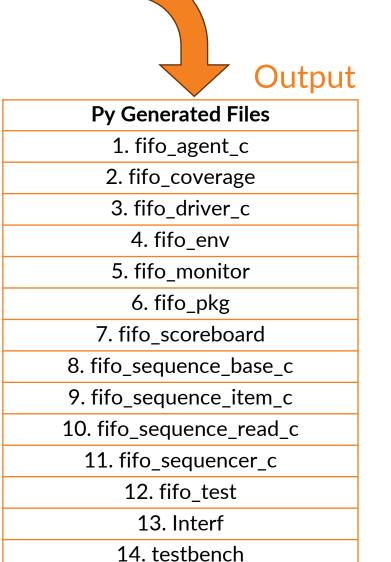

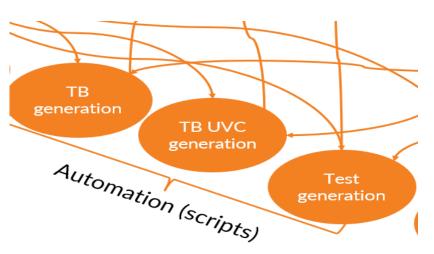

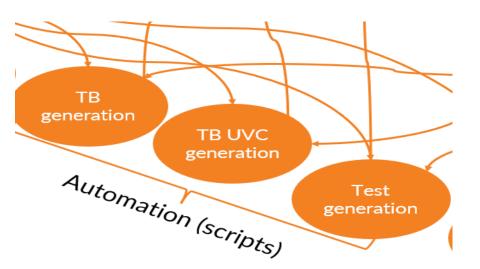

# UVM Automation – list of files generated + sample code

## Input = DUT Details including:

- DUT interface

- Control

- Data

- Interface protocols

80% Effort Reduction

## UVM Automation- sample code

### A HERO ELECTRONIX VENTURE

Input = DUT Details including:

- DUT interface

- Control

- Data

- Interface protocols

### Output = Coverage

```

class fifo subscriber extends uvm subscriber #(fifo sequence item c);

'uvm component utils(fifo subscriber)

uvm analysis imp #(fifo sequence item c, fifo subscriber) mon2c put export;

fifo sequence item c m fifo sequence item c;

bit [7:0] din;

bit [7:0] dout;

bit wr en;

bit rd en:

bit full;

bit empty1;

bit [2:0] wr_ptr;

bit [2:0] rd ptr;

covergroup cg group;

option.per instance = 1;

c1: cross full, wr_en;

c2: cross empty1, rd en;

c3: cross rd en, wr en;

c4: coverpoint wr ptr;

c5: coverpoint rd ptr;

c6: coverpoint wr ptr {bins rollover = (7 => 0);}

c7: coverpoint rd ptr {bins rollover = (7 => 0);}

c8: coverpoint din;

c9: coverpoint dout;

c10: coverpoint wr en;

cl1: coverpoint empty1;

c12: coverpoint full;

c13: coverpoint rd en;

endgroup : cg group

function new(string name = "fifo subscriber", uvm component parent = null);

super.new(name, parent);

cg_group = new();

endfunction

virtual function void build phase(uvm_phase phase);

mon2c put export = new("mon2c put export", this);

endfunction

virtual function void write(fifo sequence item c t);

m fifo sequence item c = t:

cg group.sample();

uvm info("Coverage", "-----Coverage PASSED-----", UVM MEDIUM)

endfunction

endclass

```

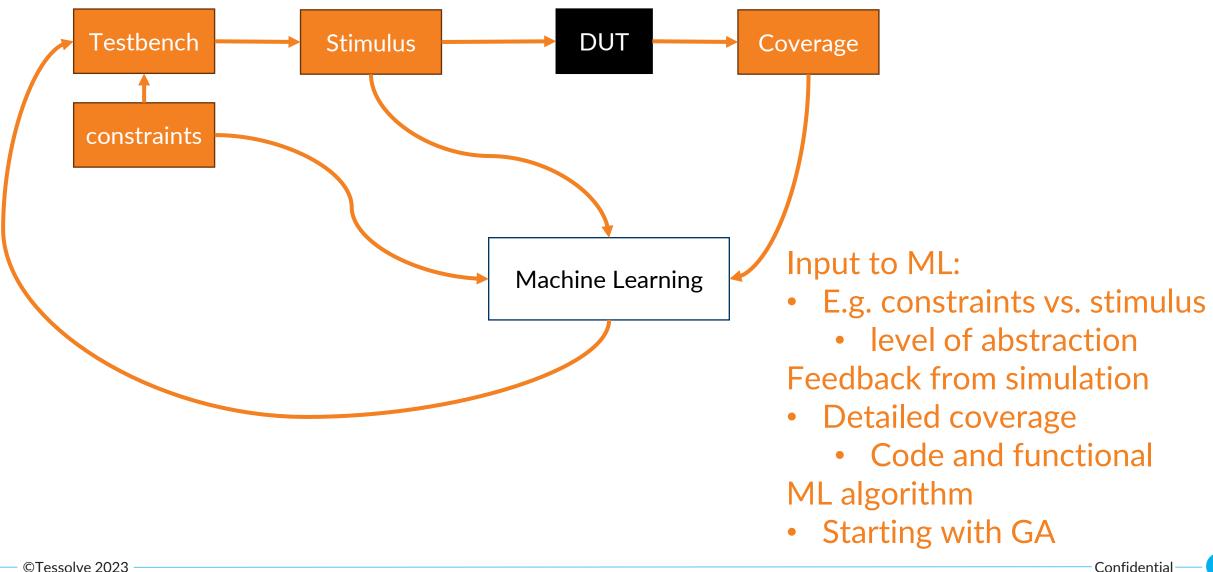

# Applying ML to coverage closure

©Tessolve 2023

# Applying Gen AI on Real Project

| Conventional | Al assisted | % Efforts |  |  |

|--------------|-------------|-----------|--|--|

| (Hrs)        | (Hrs)       | Savings   |  |  |

| 102          | 17          | 85        |  |  |

|                                     |                         |                        | Saving                                 |                      |                    |  |

|-------------------------------------|-------------------------|------------------------|----------------------------------------|----------------------|--------------------|--|

| DV Flow                             | Conventional<br>Efforts | Al Assisted Efforts    | Engineerin<br>g Efforts<br>Saved (Hrs) | % Efforts<br>Savings | Speedup<br>(times) |  |

| Specification<br>Analysis           | 1 Week, 1<br>Engineer   | 2 Hrs, 1 Engineer      | 38                                     | 95                   | 20                 |  |

| Feature Extraction & Test Plan Gen. | 2 Days, 1 Engineer      | 1 Days, 1 Engineer     | 8                                      | 50                   | 2                  |  |

| Constraint<br>Generation            | 1 Day, 1 Engineer       | 2 Hours, 1<br>Engineer | 6                                      | 75                   | 4                  |  |

| Coverage<br>Generation              | 6 Hours, 1<br>Engineer  | 1 Hour, 1 Engineer     | 5                                      | 83                   | 6                  |  |

| Assertion<br>Generation             | 1 Day, 1 Engineer       | 2 Hours, 1<br>Engineer | 6                                      | 75                   | 4                  |  |

| UVM Template<br>Generation          | 3 Days, 1 Engineer      | 2 Hours, 1<br>Engineer | 22                                     | 92                   | 12                 |  |

# Practicalities of applying AI/ML in verification

- Use of LLM

- Knowledge and expertise needed for

- The DUT

- On using LLM

- Use of ML in coverage closure

- Knowledge and expertise needed for

- The DUT

- On using ML

- Data Set size

- Large data sets (of clean, unbiased data) are needed

- Security

- LLMs use the cloud

- Documents are not saved but data is sent and later deleted

### Conclusions

- AI/ML will change the way we do verification

- It is usable now

- The results are already impressive and improving

- Chatbots are a good way to perform some basic tasks

- Spec analysis, Feature extraction, test bench infrastructure

- The quality is reasonable

- Applying ML to more complex tasks (e.g. coverage closure)

- It is being applied on a point-wise problem basis

- Applying it more widely with generalised model is more difficult

- But is coming

- EDA are adding AI/ML under the hood

- Useful but not differentiating

- Applying AI to debug can be done now

- Using EDA or build-your-own