# **Verification Futures** Conference

**Austin Marriott South**

**Thursday 14 September 2023**

## Sponsored by

#### **Participating Companies**

**Media Sponsor**

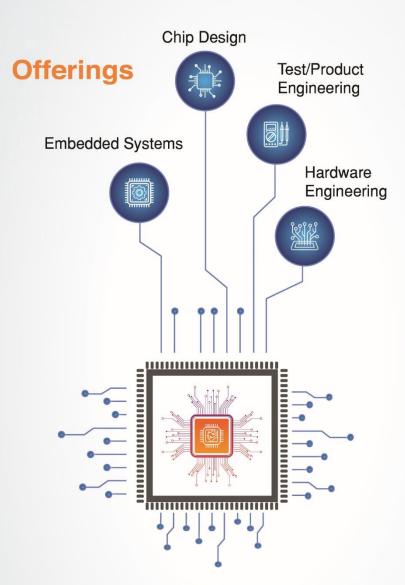

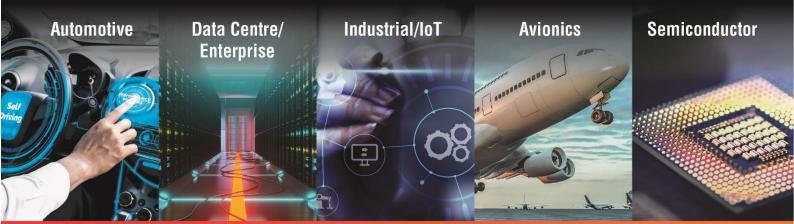

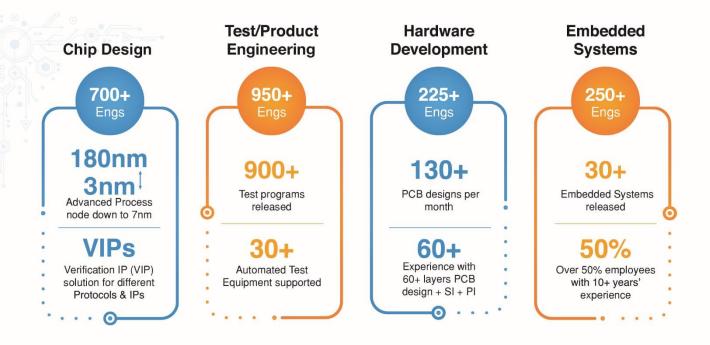

# TESSOLVE A HERO ELECTRONIX VENTURE

# Engineering Tomorrow's Solutions

Your Capable Partner Today

#### Robust Infrastructure

Test Floor | Reliability & STPI Smart Lab

#### **Expert Engineering Team**

90% Technical Staff

#### Quality Processes

Upto 30% Cycle Time Reduction

ARM, RISC-V Subsystem and Analog Block Development

5G and High Frequency RF Solutions

High Performance Compute Solution

Automotive Compliance Solution

## Let's Talk About Engineering New Possibilities

## Agenda (AM)

| 08:30 | Arrival: Breakfast and Networking                                                   |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|

| 09:25 | Welcome: Mike Bartley, Tessolve Semiconductor Ltd                                   |  |  |

| 09:30 | <b>Keynote Speakers</b><br>Vivek Vedula, ARM Ltd                                    |  |  |

| 10:15 | User Top Verification Challenges                                                    |  |  |

|       | 10:15 Alex Duhovich, Ericsson                                                       |  |  |

| 10:30 | Bahadir Erimli, Cadence Design Systems                                              |  |  |

| 11:00 | Refreshments and Networking                                                         |  |  |

| 11.30 | Multi-Track Session                                                                 |  |  |

|       | Track 1 - User Presentations on Formal Verification [Lonestar Ballroom - Salon A+B] |  |  |

|       | 11:30 Mike Bartley, Tessolve Semiconductor Ltd                                      |  |  |

|       | 11:40 Divyang Agrawal, Tenstorrent, Inc                                             |  |  |

|       | 12:10 Suneil Mohan, Intel Corporation                                               |  |  |

|       | Track 2 - Training Session 1 [Lonestar Ballroom – Salon C]                          |  |  |

|       | 11:30 Doug Smith, Doulos                                                            |  |  |

|       | Track 3 - UVM for AMS Verification [Lonestar Ballroom – Salon D]                    |  |  |

|       | 11:30 Peter Grove & Steven Holloway Renesas Remote Presentation                     |  |  |

**Lunch and Networking**

12:30

## Agenda (PM)

| 13:30 | Larry Lapides (Imperas Software Ltd.)       |                                    |  |

|-------|---------------------------------------------|------------------------------------|--|

| 14:00 | Adnan Hamid (Breker Verification Systems)   |                                    |  |

| 14:20 | Balram Naik Meghavath (Broadcom Ltd)        |                                    |  |

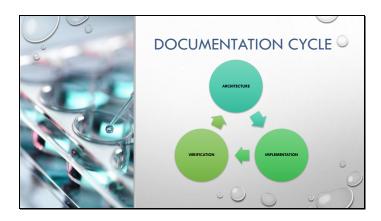

| 14:40 | Hemendra Talesara (Bitstar Technologies)    |                                    |  |

| 15:00 | Refreshments and Networking                 |                                    |  |

| 15:30 | Multi-Track Session                         |                                    |  |

|       | Track 1 – Latest Topics in Verificati       | on [Lonestar Ballroom – Salon A+B] |  |

|       | 15:30 Aditya Devarakonda, NXP Semiconductor |                                    |  |

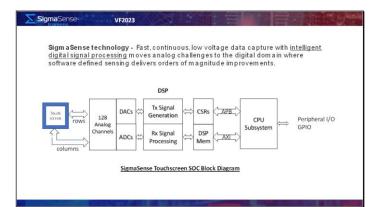

|       | 15:50 Bill Tiffany, SigmaSense LLC          |                                    |  |

|       | 16:10 Benjamin Delsol, UVMGEN               |                                    |  |

|       | Track 2 - Training Session 2                | [Lonestar Ballroom – Salon C]      |  |

|       | 15:30 Doug Smith, Doulos                    |                                    |  |

|       | Track 3 – VHDL Verification                 | [Lonestar Ballroom – Salon D]      |  |

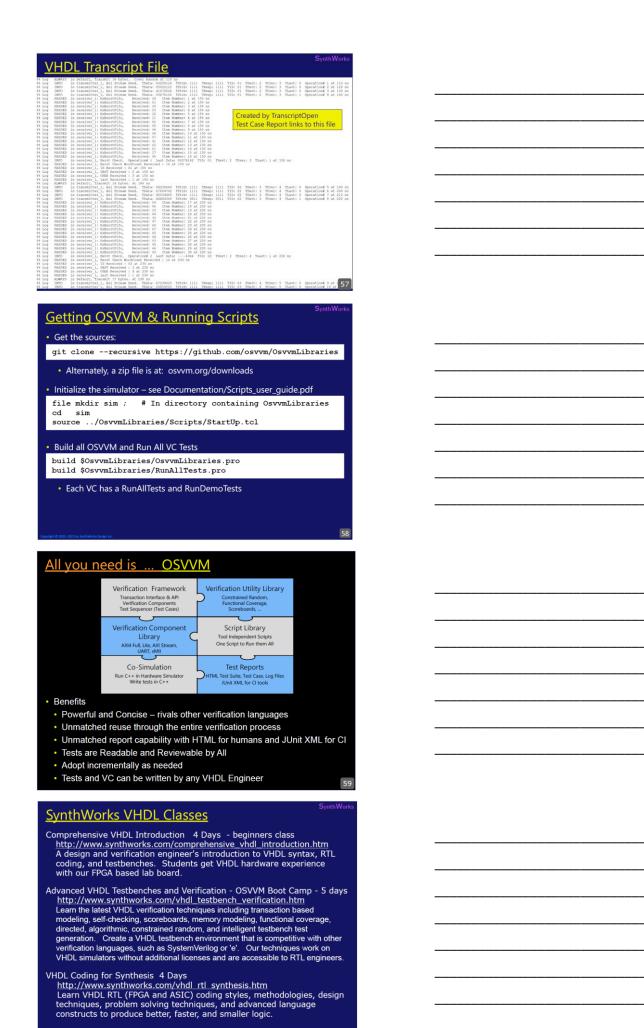

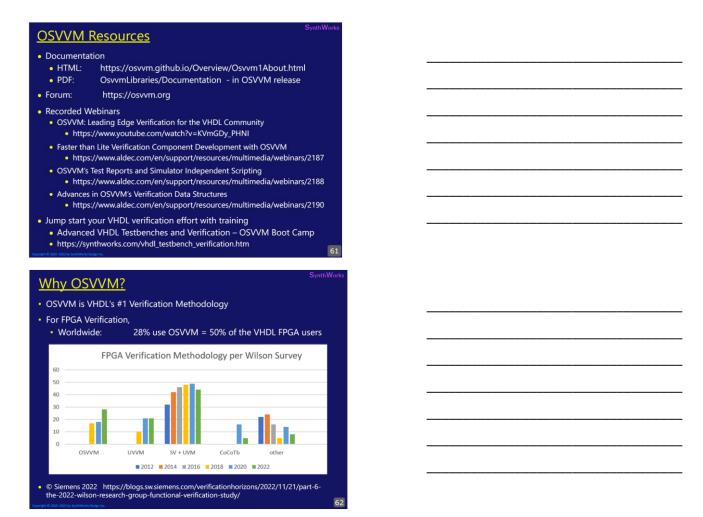

|       | 15:30 Jim Lewis, SynthWorks Design Inc      |                                    |  |

| 16:30 | Event Closes                                |                                    |  |

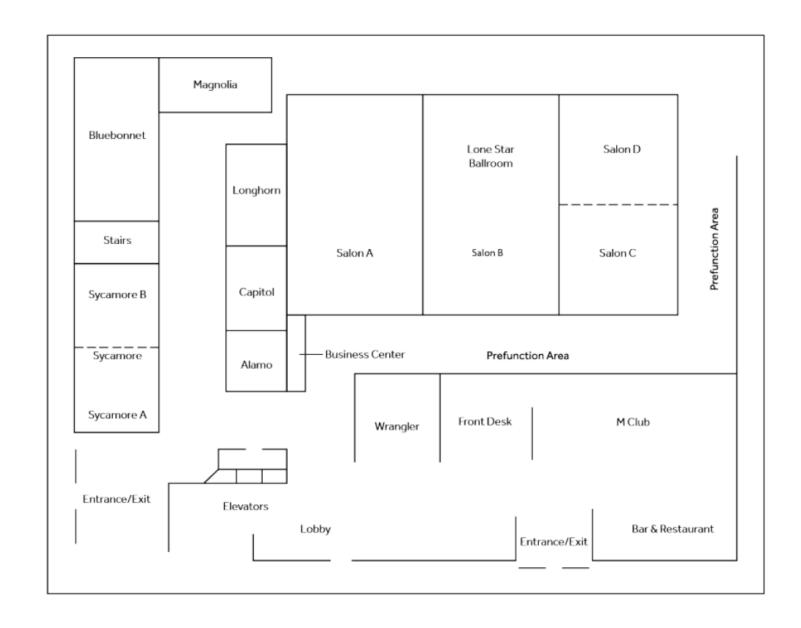

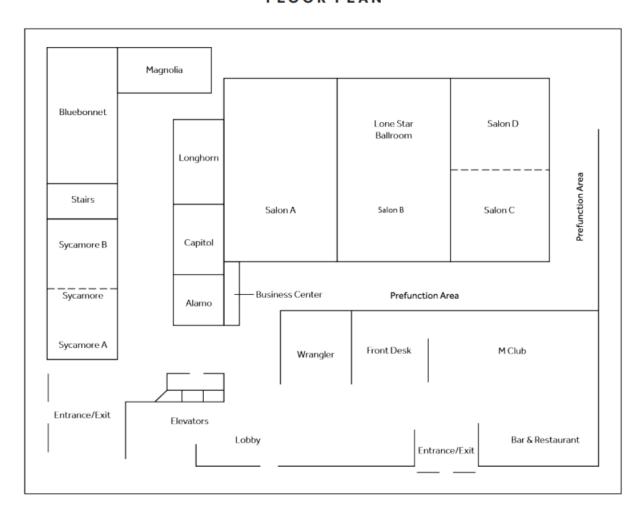

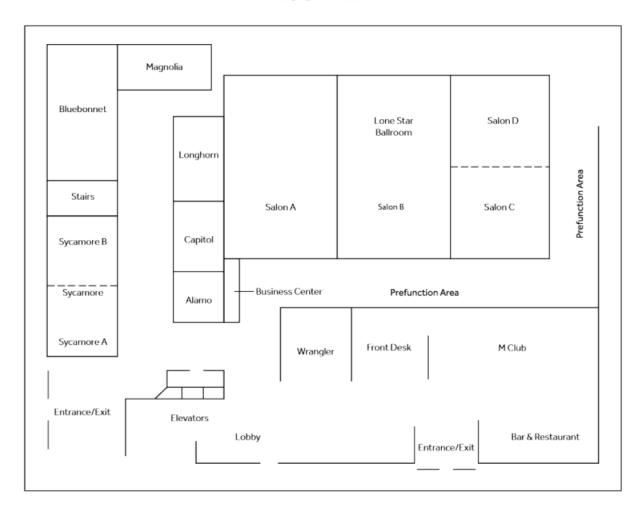

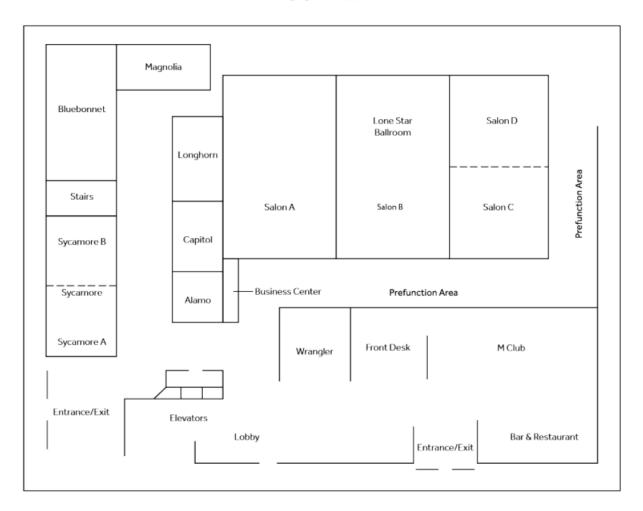

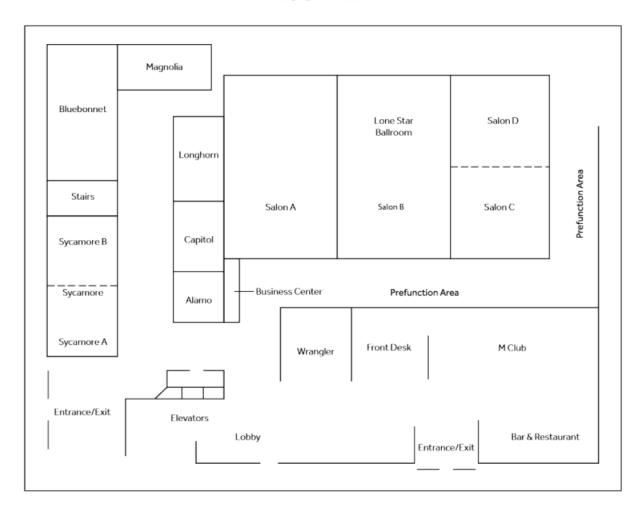

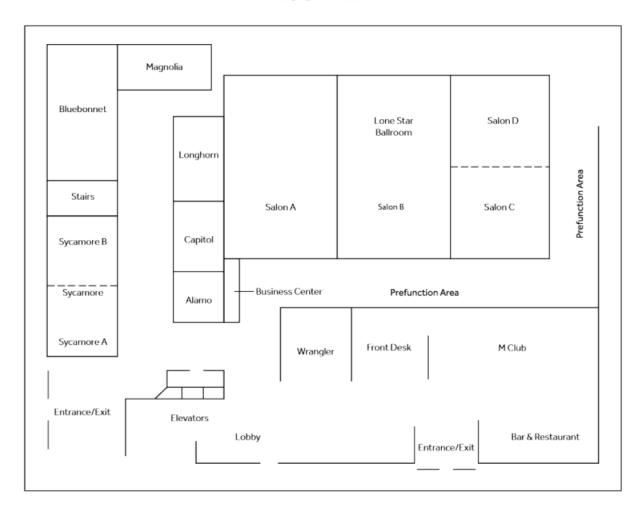

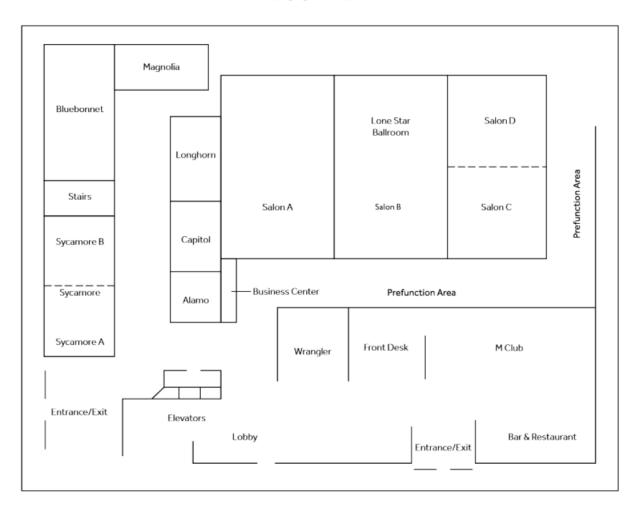

## **Floor Plan**

## Mike Bartley

# **Tessolve Semiconductor Ltd**Senior Vice President – VLSI Design

#### Welcome Message

#### **Biography**

Dr Mike Bartley has over 30 years of experience in software testing and hardware verification. He has built and managed state-of-the-art test and verification teams inside a number of companies (including STMicroelectronics, Infineon, Panasonic and start-up ClearSpeed) and also advised a number of companies on organisational verification strategies (ARM, NXP and multiple start-ups).

Mike successfully founded and grew a software test and hardware verification services company to 450+ engineers globally, delivering services and solutions to over 50+ clients in a wide range of technologies and industries. The company was acquired by Tessolve semiconductors, a global company with 3000+ employees supporting clients in VLSI, silicon test and qualification, PCB and embedded product development in multiple vertical industries.

Mike has a PhD in Mathematics (Bristol University), and 8 MSc's in various subjects including management, software engineering, computer security robotics and AI. He is currently studying (remotely) for an MSc in Blockchain and Digital Currency at the University of Nicosia, Cypress

Tessolve would like to thank the sponsors and participants of the 2023 Verification Futures Conference

## Vivek Vedula

#### **Arm Ltd**

**Technical Director**

# Safety and Security challenges in hardware IP development

#### Keynote Speaker

#### **Abstract**

Ensuring the trustworthiness in computing is increasingly becoming a challenge in the interconnected world relying on electronic systems. Security and safety provide assurance that these systems are resilient to malicious attacks and malfunctioning components, respectively. Given the diverse and rapidly evolving market demands, the requirements for both new features and performance significantly increases the probability of security- and safety-related design flaws to remain undetected. This talk will describe the challenges during IP development in efficient identification of relevant risks, and their effective mitigation for safe and secure computing.

#### **Biography**

Vivek Vedula leads the SDL methodology architecture and development for hardware IPs at Arm. Prior to this, he held several roles at Intel, NXP and Oracle Labs spanning the areas of formal verification, post-silicon validation and HW-SW co-verification. Vivek holds a PhD degree in Electrical and Computer Engineering from the University of Texas at Austin.

Slides will be shared during presentation.

## Alex Duhovich

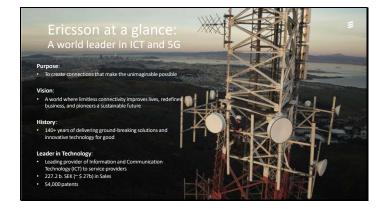

#### **Ericsson**

PEU Silicon - IP Verification Methodology Lead

# Ericsson's Challenges of IP Development and Verification for Products with a Long Shelf Life

#### Challenge Paper

#### **Abstract**

Ericsson develops ASICs for radios which have a long shelf life and an even longer life cycle. It's hard to have IP roadmaps with on-time requirements to allow for IP-centric planning and execution. This presentation will outline some of the challenges Ericsson IP teams have been facing in their quest to IP driven in a product driven market.

#### **Biography**

- 20+ years of ASIC/SoC design and verification experience

- BSEE from Drexel University, MEEE from University of Maryland College Park

- Most of career spent in the telecommunications industry

- Started at Ericsson in 2017

- Methodology lead since 2021

About myself

- 20+ Years, mainly in Telecommunications Industry (Hughes, Ericsson)

- Bachelor's in EE from Drexel in 2000

- Master's in EE from University of Maryland College Park in 2015

- Started in IP verification -> Team Lead -> Verification Methodology Lead

Email: alexei.duhovich@ericsson.com

- LinkedIn: https://www.linkedin.com/in/aduhovich/

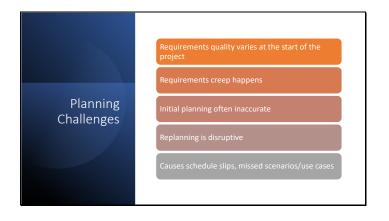

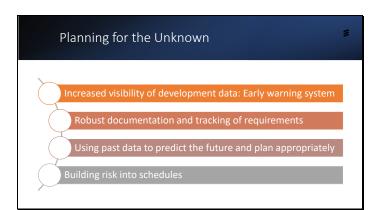

## Solutions take many form factors

Product

Centric

Development

Difficult to deliver to multiple projects at once

Product lives of ~10 years

Customer expects longevity

Products are overdesigned to support future standards

Cannot iterate on fixes between generations. Must be right the first time.

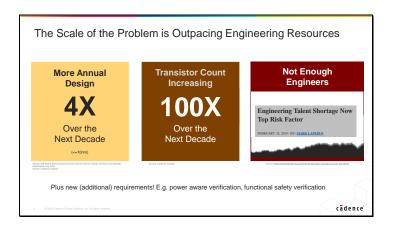

Design complexity increases exponentially

Workforce cannot keep up

Constrained-random verification doesn't scale

Most time spent on debug and coverage closure: These are hard to predict.

Power and Security are becoming extremely important

# Architecture mindset shift: IP Roadmaps with forward looking requirements Methodology and process update for feature-based, agile development Reuse and feature superset mentality for design and verification Infrastructure update to support this way of working

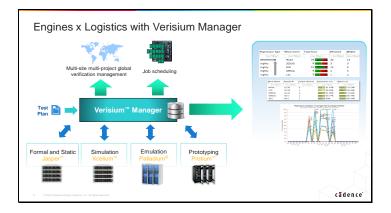

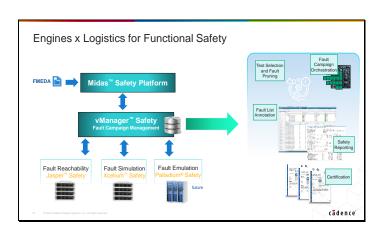

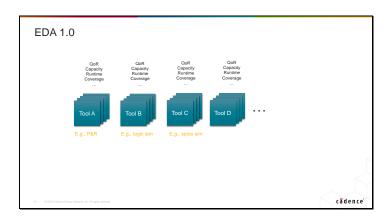

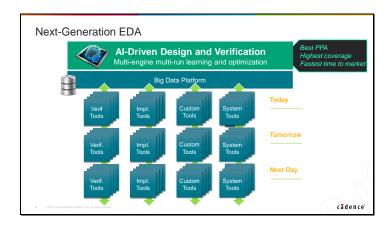

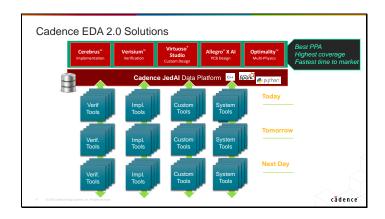

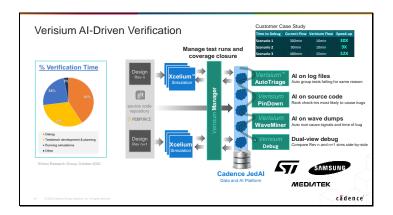

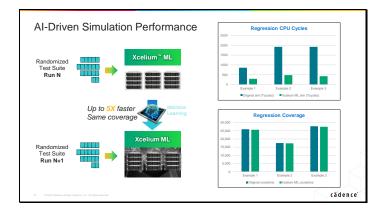

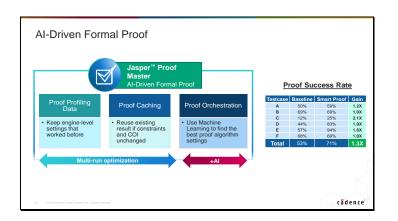

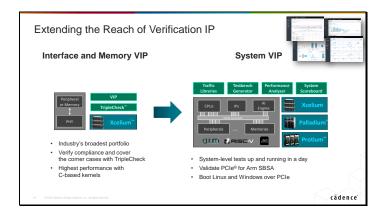

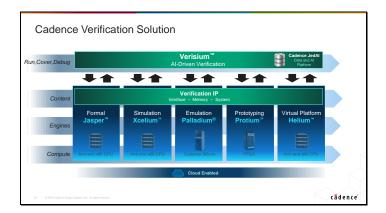

## **Bahadir Erimli**

#### **Cadence Design Systems**

Group Director – Verification Application Engineering

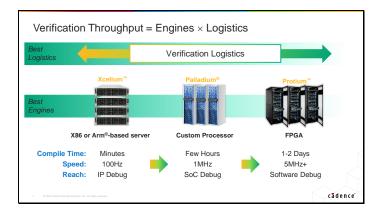

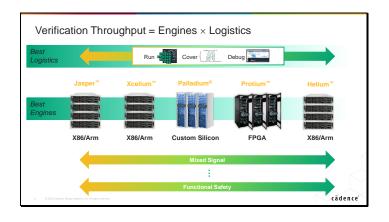

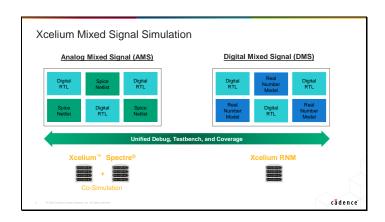

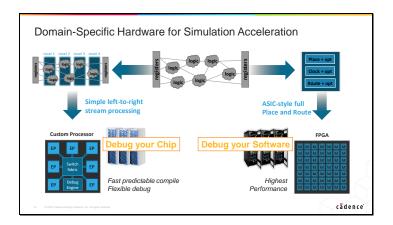

**Engines, Logistics and AI**

#### **Platinum Sponsor**

#### **Abstract**

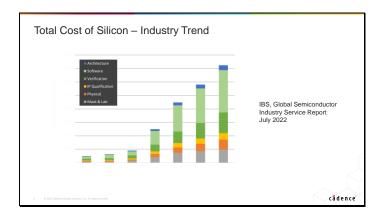

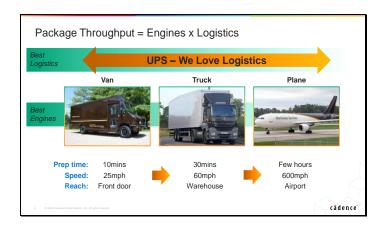

As the verification problem continues to grow, the key metric that many verification teams must closely consider is "Total Verification Throughput." While verification engines like simulation, formal, emulation and so on have a key part to play in total verification throughput, additional concepts like verification logistics and the utilization of AI can have significant impact and potentially benefit as well. This presentation will introduce the concept of verification logistics and how AI is, and will be, applied.

#### **Biography**

Bahadir Erimli is a member of the Cadence Worldwide Field Operations team where, as a Group Director he leads the Verification Applications Engineering team primarily in California including Silicon Valley. Before joining Cadence nearly 12 years ago, Bahadir held a number of senior engineering positions at consume and biotech semiconductor companies. Bahadir is based in San Diego, and holds a Bachelor's degree in Electrical Engineer from Middle East Technical University in Turkey, as well as advanced degrees in electrical engineer from Caltech.

# Thank You

## **Track Session**

# User Presentations Lonestar Ballroom – Salon A+B

#### **FLOOR PLAN**

We would be grateful if you could move to the track session as quickly as possible.

## Mike Bartley

## Tessolve Semiconductor Limited Senior Vice President - VLSI

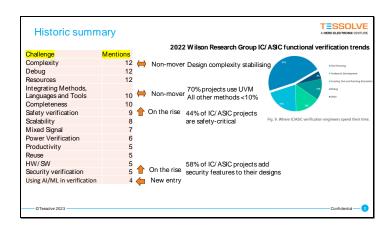

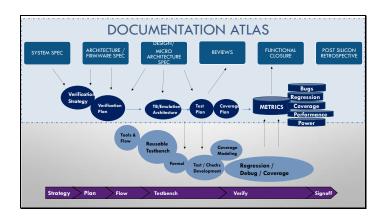

10 years of Verification Challenges

#### **User Paper**

#### **Abstract**

Verification Futures has been running for more than 10 years and in that time more than 25 verification managers have given their views on their main challenges in verification. This talk will summarise those challenges and the main solutions organisations have put in place.

## **Divyang Agrawal**

#### Tenstorrent, Inc

Sr. Director, RISCV Cores

#### **RISCV CPU Verification - Opportunities and Challenges**

#### **User Paper**

#### **Abstract**

The highly configurable nature of RISCV ISA makes it uniquely suited for a hierarchical verification methodology covering both architectural and microarchitectural complexity. This technical talk will focus on how Tenstorrent leveraged on the lessons from x86 and ARM to build a modular and scalable CPU verification framework. It will also preview how design complexity has to be tackled looking at silicon as a starting point. And ultimately why robust open source RISCV verification collateral is essential for broader adoption of the ISA from microcontrollers to high performance datacenter class products

#### **Biography**

Divyang Agrawal is a Senior Director at Tenstorrent where he works on RISCV Cores focusing on design verification, emulation, architectural tools and methodologies. He has previously worked on x86 and ARM architectures. Prior to Tenstorrent, Divyang worked at AMD where he held leadership roles within AMD's CPU Cores team working on several generations of high-performance cores. He also led the CPU Power Management IPs and Silicon Validation for all AMD cores. Divyang has a BTech in EE from Nagpur, India and an MBA from University of California at Berkeley

Slides will be shared during presentation

## Suneil Mohan

# **Intel Corporation**SOC Design Engineer

#### **Validation of Hybrid Architectures**

#### **User Paper**

#### **Abstract**

Intel's 12<sup>th</sup> generation processors (code named Alderlake) introduced a new asymmetrical design that combines a mix of Performance Cores (P-cores) and Efficient Cores (E-cores), delivering scalable, efficient, multi-threaded performance in a single package. The validation challenge for this asymmetrical design spanned both Pre Silicon and Post Silicon phases. To meet the challenge of validating thoroughly the new asymmetrical design, our validation methodology had to be overhauled; this ranged from updating existing test generators all the way to developing new testing methodologies. In this presentation, we will cover key aspects of our asymmetrical design validation methodology in both Pre and Post Silicon phases, the strategies we adopted and the challenges that we had to overcome.

#### **Biography**

Dr. Suneil Mohan received his BE from Anna University in India in 2006 and PhD from Texas A&M University in 2012. He is a senior validation engineer in the Intel E-core team with deep expertise in both Emulation and Post silicon validation. He is currently the Post Silicon debug lead for the E-core team. He has worked on multiple generations of the E-core product line including those that are part of the most recent 13<sup>th</sup> Generation Intel® Core™ processors. In addition, he has experience working on the ISO26262 standard.

#### Agenda

- Introduction to Intel Hybrid architecture

- Pre-Silicon challenges and solutions

- Post Silicon functional validation methodologies

- OS Based Verification

- Functional Validation Sign Off

#### Intel Performance Hybrid Architecture Designed to deliver efficient high-compute performance in a large dynamic power and performance range Efficient-cores Performance-cores • Smaller, with multiple E-cores fitting into the physical space of one P-core. • Larger, high-performance cores designed for speed while maintaining efficiency. • Designed to maximize CPU efficiency, Tuned for high IPC (instructions per cycle) and high turbo frequencies. measured as performance-per-watt. • Ideal for scalable, multi-threaded performance. Does not support hyper-threading • Supports hyper-threading

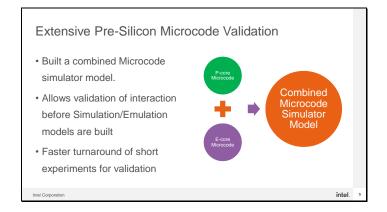

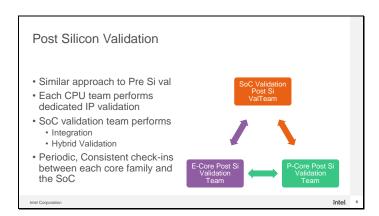

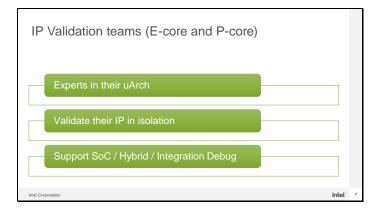

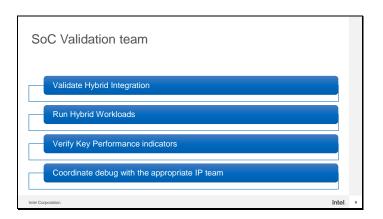

#### Pre-Silicon Verification · 3-prong approach Each CPU team performs dedicated IP validation (Simulation, Emulation & FPGA environments) • SoC validation team performs IntegrationHybrid Validation · Periodic, Consistent check-ins between each Core and the SoC intel.

# OS Based Verification What if Synthetic Workloads are not stressful enough? 1. Analyzed Open-Source OS scheduler • External Software may have corner source code for task switching case behaviors that are not always 2. Ran Task Switching OS Scheduler code modelled. on the combined microcode simulator • External Software may do things that model to understand the behavior are not completely to 'spec' 3. Built a randomized OS task switcher for • Need to see how random task Post Silicon validation switching might behave intel. Functional Validation Sign off Pre-Silicon Post Silicon Pass rates for synthetic test content. Acceptable pass rates for synthetic test content · All failures accounted for, All failures accounted for, understood and dispositioned understood and dispositioned • Coverage data analysis complete. Power and Performance data • Power and Perf data collected, meeting projections analyzed and within expected • 100% pass rate for the OS task ranges. switching tests. • Thread Director working as expected References and Additional Resources [1] E. Rotem et al., "Intel Alder Lake CPU Architectures," in IEEE Micro, vol. 42, no. 3, pp. 13-19, 1 May-June 2022, doi: 10.1109/MM.2022.3164338. [2] How 13th Gen Intel® Core™ Processors Work: https://www.intel.com/content/www/us/en/gaming/resources/how-hybrid-design-works.html S. Khushu and W. Gomes, "Lakefield: Hybrid cores in 3D Package," 2019 IEEE Hot Chips 31 Symposium (HCS), Cupertino, CA, USA, 2019, pp. 1-20, doi: 10.1109/HOTCHIPS.2019.8875641 Lakefield W. Gomes, S. Morgan, B. Phelps, T. Wilson and E. Hallnor, "Meteor Lake and Arrow Lake Intel Next-Gen 3D Client Architecture Platform with Foveros," 2022 IEEE Hot Chips 34 Symposium (HCS), Cupertino, CA, USA, 2022, pp. 1-40, doi: 10.1109/HCS56986.2022.9985532 Meteor Lake "I've never had so much fun - intel development center deep dive," YouTube, 25-May-2022. [Online]. Available: https://youtu.be/BtFdraQWVtM [Accessed: 16-Jul-2023] Intel Validation Lab Intel 12th Gen Validation "I saved the best for Last - Intel Design Center Development Motherboard," YouTube, 06-Jul-2022. [Online]. Available: https://youtu.be/pyVZ05SO0Ic [Accessed: 16-Jul-2023] Q & A

intel.

# **Track Session**

# Training Session - 1 **Lonestar Ballroom – Salon C**

### **FLOOR PLAN**

We would be grateful if you could move to the track session as quickly as possible.

# **Notes**

# **Doug Smith**

## **Doulos**

Engineer / Instructor

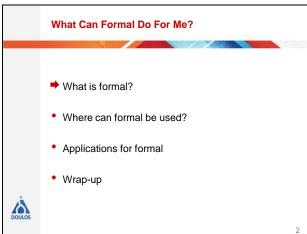

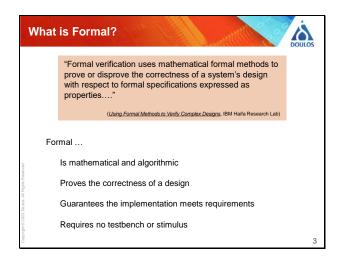

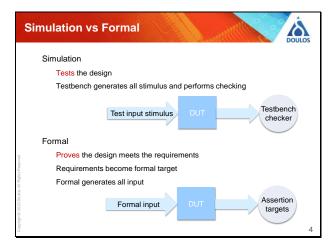

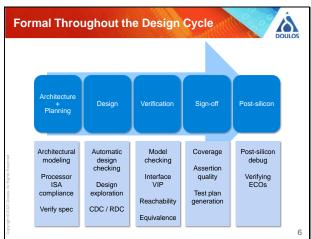

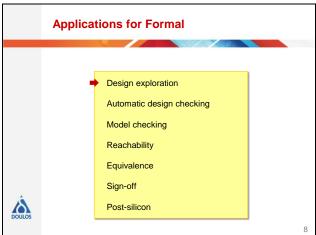

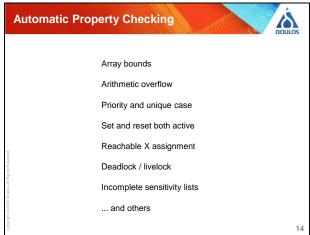

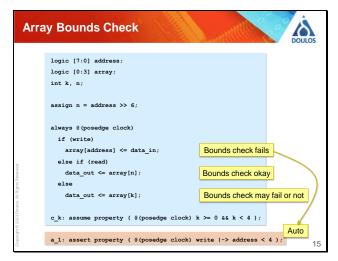

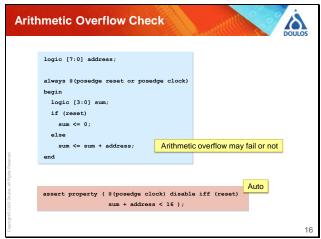

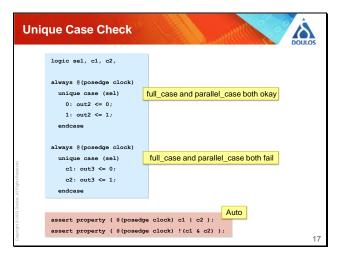

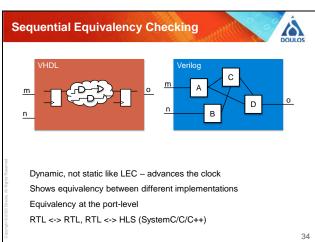

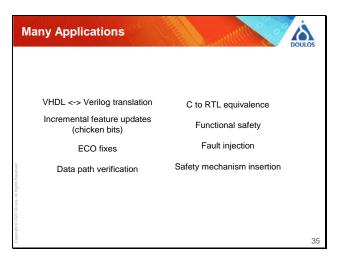

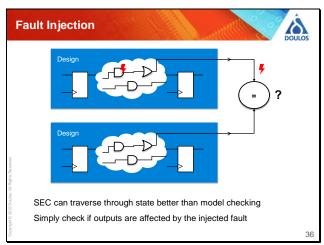

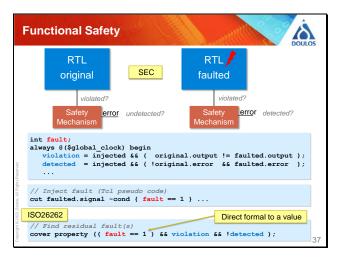

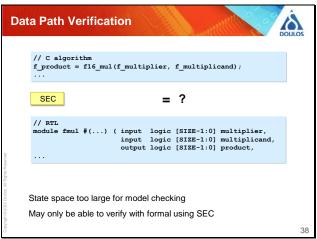

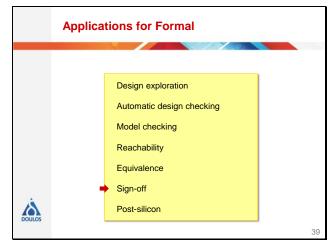

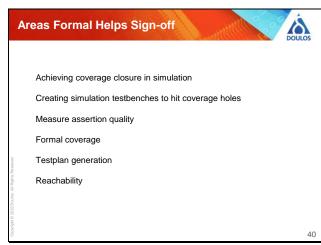

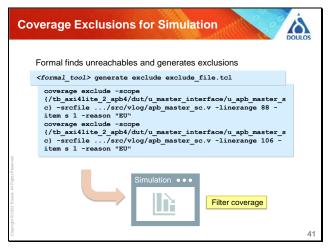

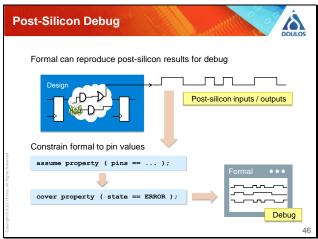

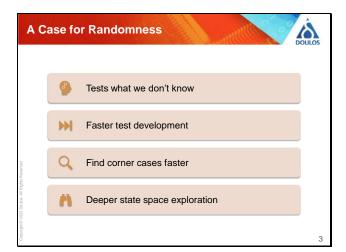

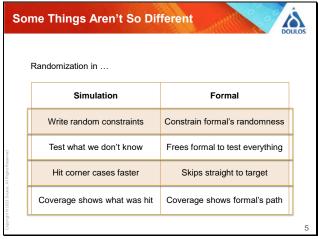

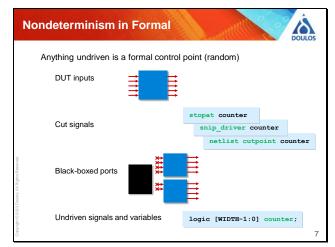

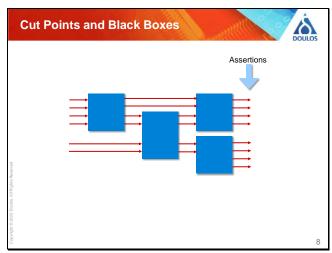

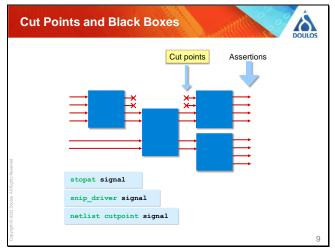

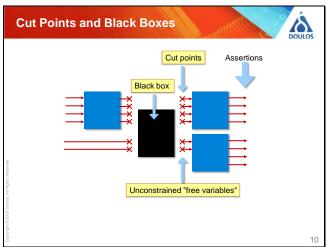

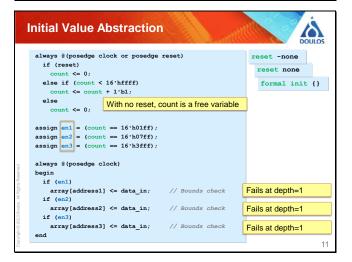

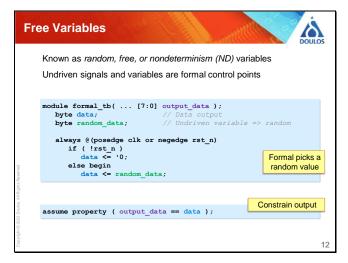

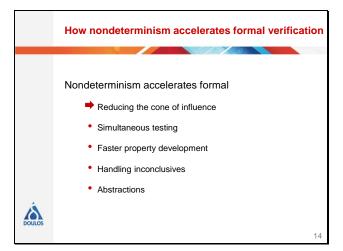

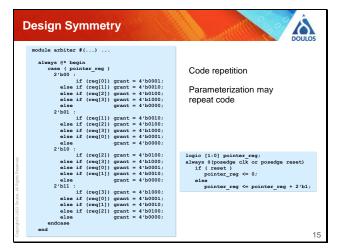

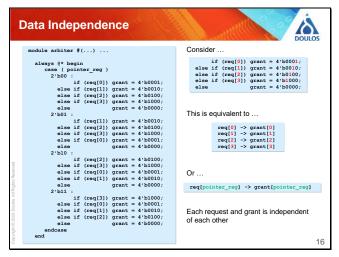

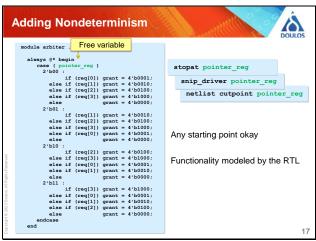

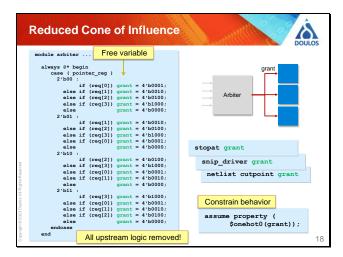

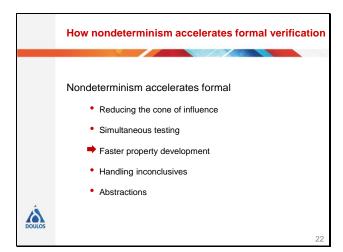

# What Can Formal Do For Me?

# **Gold Sponsor**

### **Abstract**

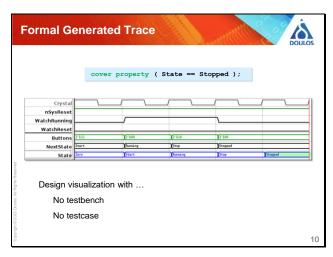

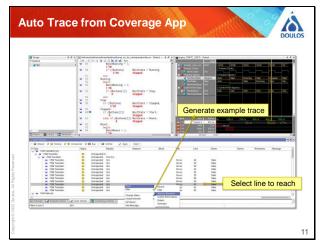

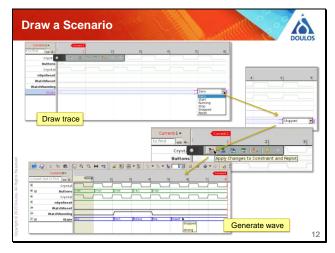

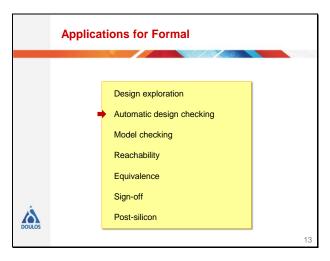

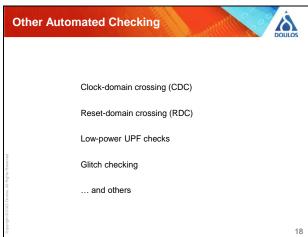

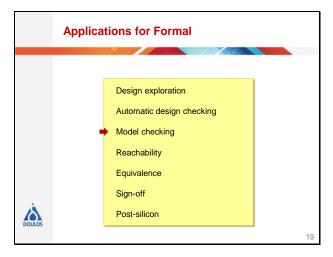

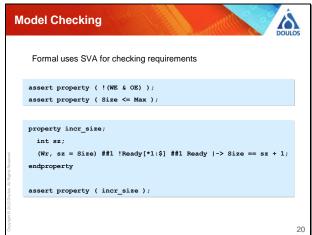

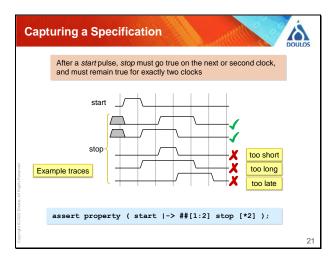

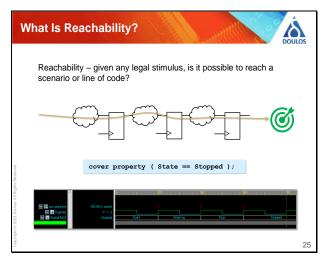

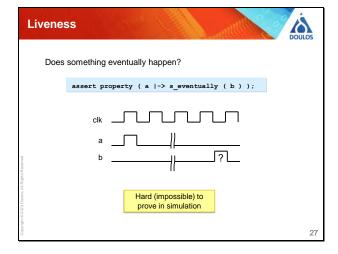

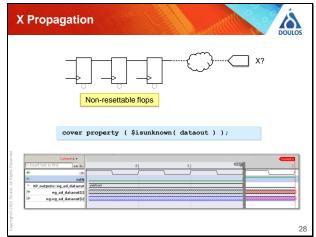

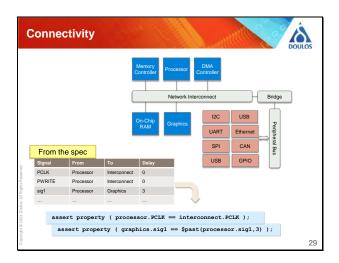

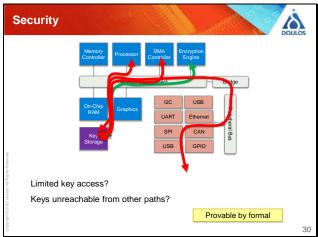

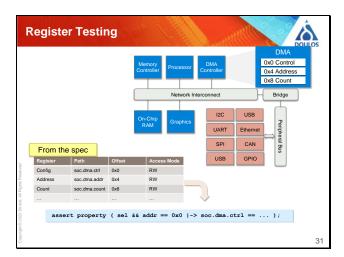

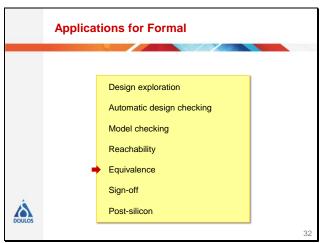

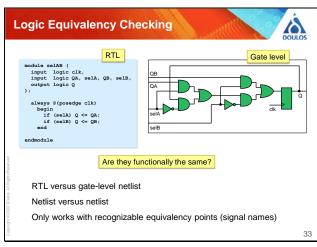

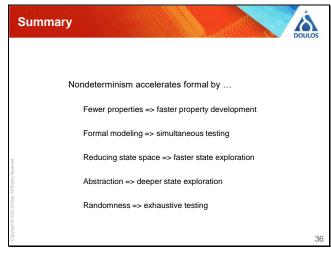

We know formal can prove things, but where do we apply it? Did you know you can use formal to generate simulation testbenches for covering coverage holes or have it visualize your design without writing a single line of testbench code? Formal can be used for identifying metastability, X propagation, fault propagation and detection, equivalence, and so much more. In this tutorial session, we'll have a look at the many ways formal helps out your design verification process.

### **Biography**

Doug Smith is a verification engineer and instructor for Doulos based in the Austin Texas area with expertise in UVM and formal technologies. He has been using formal technology for several decades, performing formal verification on many kinds of designs and formal applications. Likewise, he has provided formal application support at both Jasper and Mentor/Siemens EDA. At Mentor/Siemens EDA, he served as a formal specialist and verification consultant, where he provided both formal consulting and developed an automotive functional safety formal app for performing formal fault campaigns. At Doulos, he delivers training in verification methodologies like UVM, SystemVerilog, and formal technology.

Doug holds a masters degree in Computer Engineering from the University of Cincinnati and a bachelors degree in Physics and Biology from Northern Kentucky University. Currently, he resides in Paige Texas with his wife and family on a small farm where he raises bees, cows, horses, chickens, and pigs and loves driving a tractor.

# **ESL & Verification Methodology**

- » SystemVerilog » UVM

- » SystemC » TLM-2.0 » Formal

# Hardware Design (ASIC / FPGA)

- » VHDL » Verilog » SystemVerilog

- » Tcl » AMD » Intel FPGA

# **Arm & Embedded Design**

- » Arm Cortex A/R/M Series » C » C++

- » RTOS » Linux » Yocto » Security

# Al & Deep Learning

- » Edge AI » Deep Learning

- » Python

# **Practice – Share – Learn**

Simulate your hardware description code in a web browser for free

Call +1-888-GO-DOULOS to discuss your training needs

```

unique case (State)

Zero: if (Buttons[1]) NextState = Start;

Start: begin

WatchRunning = 1;

if (!Buttons) NextState = Running;

end

Running: begin

WatchRunning = 1;

if (Buttons[1]) NextState = Stop;

end

Stop: if (!Buttons) NextState = Stopped;

Stopped: if (Buttons[1]) NextState = Start;

else if (Buttons[2]) NextState = Reset;

Reset: begin

WatchReset = 1;

if (!Buttons) NextState = Zero;

end

endcase

cover property ( State == Stopped );

```

|      |      | _           |

|------|------|-------------|

| <br> | <br> | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

|      | <br> | _           |

|      | <br> | _           |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

|      |      | _           |

| <br> |      | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

| <br> | <br> | _           |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

| <br> |      | _           |

| <br> | <br> | _           |

|      |      | _           |

|      |      | _           |

|      |      | _           |

|      |      |             |

|      |      |             |

|      |      | _<br>_<br>_ |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

|      |      |             |

| <br> |

|------|

|      |

| <br> |

|      |

| <br> |

|      |

| <br> |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| <br> |

|      |

|      |

|      |

|      |

| <br> |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| <br> |

| <br> |

|      |

| <br> |

| <br> |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|       | <br> |  |

|-------|------|--|

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       | <br> |  |

| <br>  | <br> |  |

|       |      |  |

| <br>  | <br> |  |

| <br>  | <br> |  |

|       |      |  |

|       | <br> |  |

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

| <br>  | <br> |  |

|       | <br> |  |

|       |      |  |

| <br>  | <br> |  |

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

| <br>  | <br> |  |

|       |      |  |

|       |      |  |

|       |      |  |

|       |      |  |

| <br>  | <br> |  |

|       | <br> |  |

| <br>- |      |  |

| <br>  | <br> |  |

| <br>  | <br> |  |

|       |      |  |

| <br>  | <br> |  |

| <br>  | <br> |  |

|       |      |  |

| <br>  | <br> |  |

| <br> | <br> |

|------|------|

| <br> |      |

|      |      |

|      | <br> |

| <br> |      |

|      |      |

|      |      |

| <br> | <br> |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

| <br> | <br> |

|      |      |

|      |      |

| <br> | <br> |

| <br> |      |

|      |      |

|      | <br> |

| <br> |      |

|      |      |

|      |      |

|      |      |

|      |      |

| <br> | <br> |

| <br> | <br> |

|      |      |

|      |      |

| <br> | <br> |

|      |      |

|      |      |

| <br> | <br> |

| <br> |      |

|      |      |

|      |      |

|      |      |

|      |      |

| <br> | <br> |

|      |      |

|      |      |

| <br> | <br> |

| <br> |      |

|      |      |

| <br> | <br> |

| <br> | <br> |

|      |      |

|      |      |

|      |      |

# Formal complements your simulation flow Formal verifies scenarios hard or tedious in simulation Formal can be part of any verification planning and effort Why would you not take advantage of what formal can do?

# **Notes**

# **Track Session**

# UVM for AMS Verification **Lonestar Ballroom – Salon D**

### **FLOOR PLAN**

We would be grateful if you could move to the track session as quickly as possible.

# **Notes**

# **Peter Grove & Steven Holloway**

## Renesas

Distinguished Member of Technical Staff & Member of Technical Staff

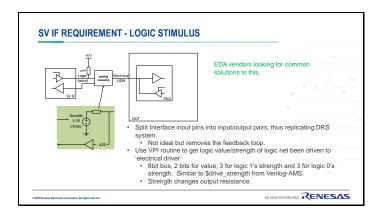

# Renesas's Submission to the UVM-(A)MS working group

# **User Paper**

### **Abstract**

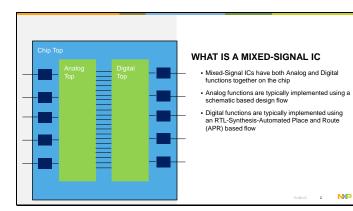

Explanation on how UVM can be applied to DMS/AMS using a concept of a MS Bridge module. The focus will be on an AMS Device-Under-Test, but the concepts work for DMS. The audience will be guided over subtleties of AMS simulators and a known limitation with the proposal and possible solutions. There will be a walk though of how this was applied to a Mixed signal block. The audience should not take way the current implementation until an official release of UVM-AMS has been made. The current contents of the presentation and example code has been shared to the EDA community to feed into a white paper on the topic. Steven will cover the UVM aspects and Peter will go over mixed signal parts.

DMS – Digital-Mixed-Signal also referred to as Real-Number-Modelling

AMS – Analog-Mixed-Signal

MS - Mixed Signal

### Biography

### **Peter Grove**

Peter has worked in the industry starting back in 2001 when he joined a small company called Wolfson MicroElectronics, where he was project lead for more than 15 production devices. Since then Peter has only worked at one other company, Nujira, before joining Dialog (now Renesas) at their Edinburgh office. Peter has been with Dialog since 2014. Peter's background has been main digital design, but has over the years taken charge of many large mixed signal devices that are in volume production and been exposed to enough analogue design work to appreciate the issues they face in verification. Peter has an eye for looking for ways in which techniques can be done to improve chip level coverage, simulation runtime improvement to name a few.

Peter is also in a unique position that during his days at Wolfson he was a key player in defining their schematic/Layout tool set with integrated revision control. This has allowed Peter to gather a large number of skills not just in design work but in all the backend flows and EDA tools, understanding different netlist types and how the tools work.

Peter's technical interests are mixed signal and analogue verification methodologies, design flows. Peter also is an Acellera SystemVerilog-AMS committee chair, UVM-AMS member/key contributor making sure the 'users' feedback on the language is considered and not what the vendors just want to support.

### **Steven Holloway**

Steve has 20+ years' experience of digital verification including eRM, OVM, UVM and formal property checking. He has led the verification of large-scale consumer SoC projects. He joined Dialog Semiconductor in 2011 and previously worked for Doulos, NXP and Trident Microsystems. He joined the Technical Ladder in 2015.

Steve has presented at multiple external conferences including a panel session at DVCon US. He participates in industry standards bodies and has contributed code to the Accellera UVM-AMS working group

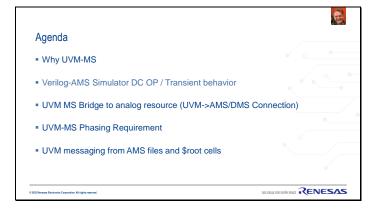

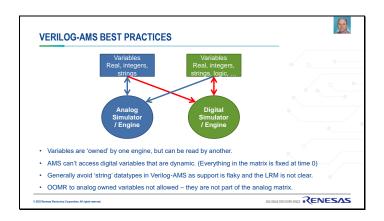

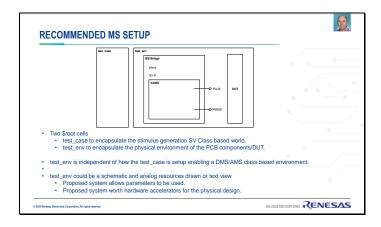

### Agenda

- Why UVM-MS

- Verilog-AMS Simulator DC OP / Transient behavior

- UVM MS Bridge to analog resource (UVM->AMS/DMS Connection)

- UVM-MS Phasing Requirement

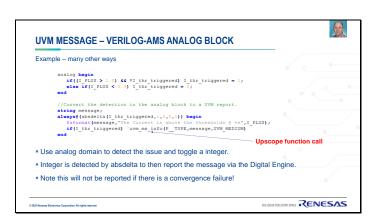

- UVM messaging from AMS files and \$root cells

© 2023 Renesas Electronics Corporation. All rights reserved.

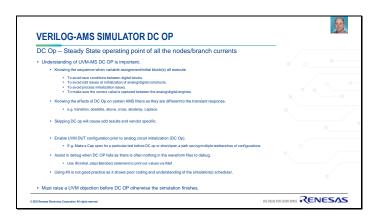

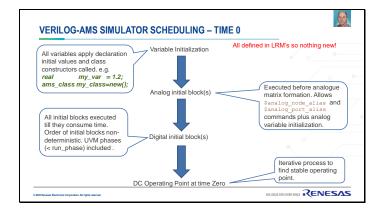

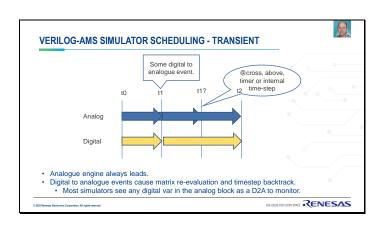

### WHY UVM-MS

- UVM is the industry standard methodology for reusable metric driven verification

- UVM-MS is the standardisation of analogue/mixed signal extensions for UVM

- Allows UVM to be more mixed-signal aware

Improved verification of analogue/mixed-signal designs

- Same degree of thoroughness for both analogue and digital parts

- Originally named UVM-AMS but focus is to support any MS system; DMS, RNM, Spice or a mixture

- Metric-driven verification suits following objectives due to verification space size

- . Verifying analogue performance under large set of digital configurations Digital control system transitions interacting with analogue functions

- Dynamic control between analogue & digital circuits under wide range of conditions

- Finding problems with A/D interaction in unexpected corner cases

- Randomisation is not mandatory and benefits are gained even when using directed tests

- Plug & play reuse of existing UVM components

- Rich debug & messaging scheme integrated with simulator

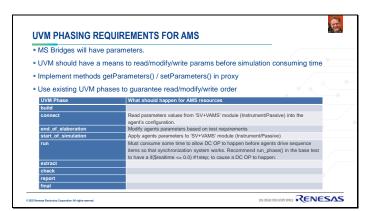

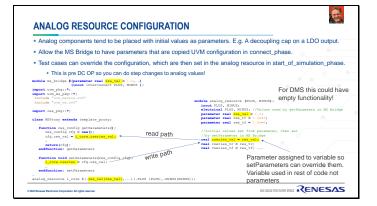

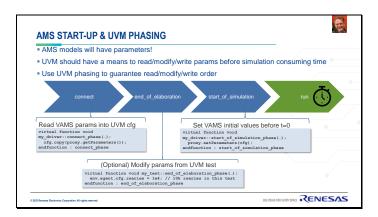

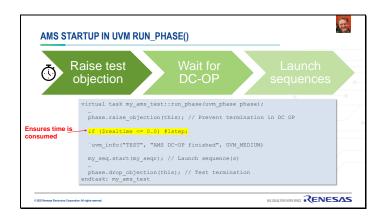

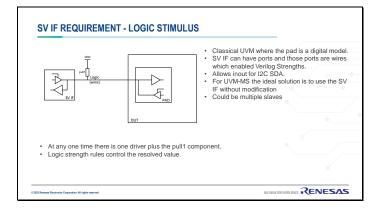

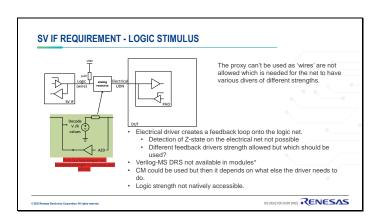

### **UVM-MS REQUIREMENTS**

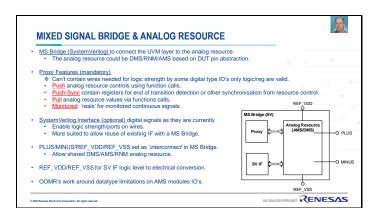

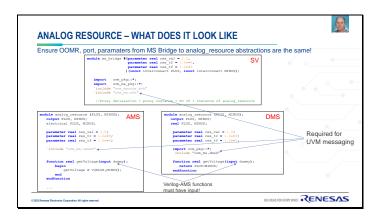

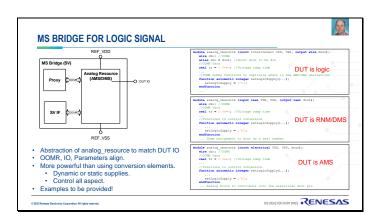

- Apply UVM methods and techniques to AMS circuits and systems while allowing DMS/RNM.

- Enable a single environment to work whether it is DMS/RNM or AMS by changing the abstraction of the DUT.

- Extend the use of UVM components, and extensions thereof, into the physical layer enabling AMS verification.

- Allow predictable coordination of stimulating/measuring a signal

- Adhere to the sequence/sequence-item mechanism used by UVM

- Independent of the abstraction level of the AMS signals (electrical, RNM, UDT, etc.)

- Eliminate the need to rely on conversion elements to change the abstraction level of the DUT signals.

- Use existing language standards; SV and Verilog-AMSChanges take years to get agreement.

BIG IDEAS FOR EVERY SPACE RENESAS

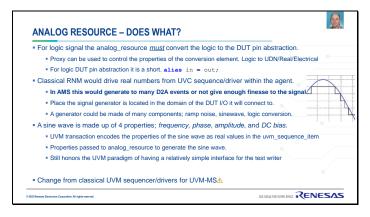

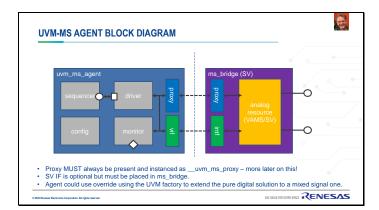

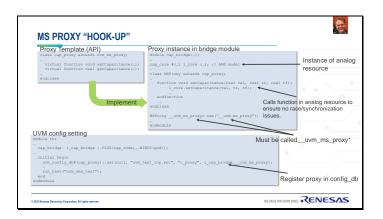

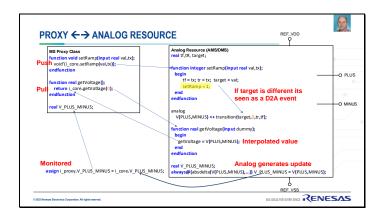

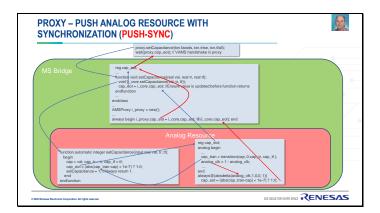

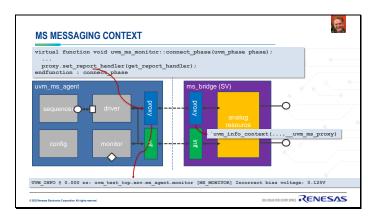

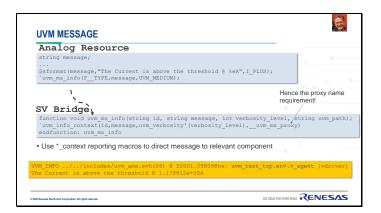

# PROXY CLASS Proxy is designed to be a "thin layer" between UVM and the analog resource implementation Alternative style of connection between UVM classes and SV static hierarchy Proxy class derived from uvm\_ms\_proxy which is derived from uvm\_report\_object Embedded class definition placed inside SV bridge module – called "MSProxy" – concrete class Class instance must be called \_uvm\_ms\_proxy for messaging to work. A handle to the embedded proxy class is obtained by hierarchical reference and placed in the uvm\_config\_db for access by UVM components. Same as SV Virtual IF! Implementation of proxy API methods in bridge module in turn execute analog resource "core" methods – hence "proxy" pattern.

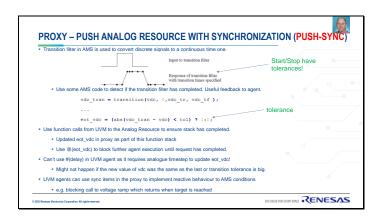

# Agenda Why UV

- Why UVM-MS

- Verilog-AMS Simulator DC OP / Transient behavior

- UVM MS Bridge to analog resource (UVM->AMS/DMS Connection)

- UVM-MS Phasing Requirement

- UVM messaging from AMS files and \$root cells

© 2023 Renesse Electronics Corporation. All rights reserved.

BIG IDEAS FOR EVERY SPACE RENESAS

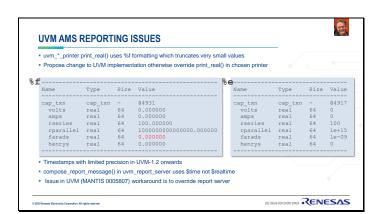

### **UVM MESSAGING REQUIREMENT**

E

- Need to filter and control generation of messages from analog resource

- UVM offers this control for components in UVM hierarchy

- But analog resource is not part of the UVM component hierarchy. It's a module!

- However, if we extend the MS proxy from *uvm\_report\_object*

- set\_report\_handler() can redirect handling to the enclosing UVM MS monitor

- messages from MS bridge (and below) can use the proxy context

- $\verb""ivm_info_context"(.\ , .\ , .\ , \textit{ro})$  takes reporting object to provide context

- Messaging macros called from analog resource can use upscoping (see later)

- Recommend to include %m in the UVM message body to get a physical path.

0 2023 Renesse Electronics Corporation, All rights reserve

BIG IDEAS FOR EVERY SPACE RENESAS

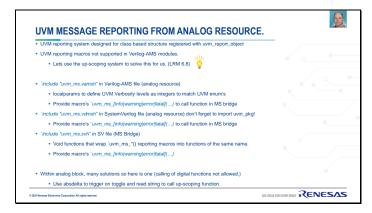

| Statement               | Usage                                                                                                                                                                                  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| import uvm_ms_pkg::*;   | Within the MS Bridge and uvm_ms_agent.                                                                                                                                                 |  |

| `include "uvm_ms.vamsh" | For Verilog-AMS modules defined as the analog_resource or hierarchy.                                                                                                                   |  |

| `include "uvm_ms.dmsh"  | For SV modules defined as the analog_resource or hierarchy, E.g. The Verilog-AMS file instance in SV module, this 'include would allow the SV module to use the same messaging system. |  |

| `include "uvm_ms.svh"   | For inclusion in the MS Bridge to enable the commincation from the analog_resources. It requires the MS Proxy instance is nameduvm_ms_proxy.                                           |  |

| Logic Conversion needs reference VDD/VSS levels.                                                                                                                                                                                                                                                               |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Dynamic tracking                                                                                                                                                                                                                                                                                               |                   |

| Dedicated pins REF_VDD/REF_VSS in MS_BRIDGE/Analog Resource.     OOMR using analog_node_alias() and parameters for AMS only.     Can only be parameters as this is setup pre DC OP.                                                                                                                            |                   |

| <ul> <li>Ideally it would use ref_vdd/vss but alias to port is not allowed. (Veril</li> </ul>                                                                                                                                                                                                                  | og-AMS LRM 9.20)  |

| 2. real values set like other controls in the MS Bridge to the analog resource.                                                                                                                                                                                                                                |                   |

| analog initial begin  if(f" VUD RATH != "NOT VALID") 46 (Sanalog node alias(REF VUD INT, P_ VUD PATH)  Serror("Omable to resolve power supply: %s", P_ VUD PATH);  if(f" VSE RATH != "NOT VALID") 46 (Sanalog node alias(REF VSE INT, P_ VSE PATH)  Serror("Omable to resolve ground supply: %s", P_ VSE PATH) | OOMR Paths        |

| end                                                                                                                                                                                                                                                                                                            |                   |

| <pre>analog begin if(use fixed supply) logic_supply = a2d_supply * logic_tran; else if(E _VDD PATH != "NOT VALIO") logic_supply = V(REF_VDD_INT,REF_VSS_INT); else logic_supply = V(REF_VDD,REF_VSS).</pre>                                                                                                    | Voltage Selection |

| end                                                                                                                                                                                                                                                                                                            |                   |

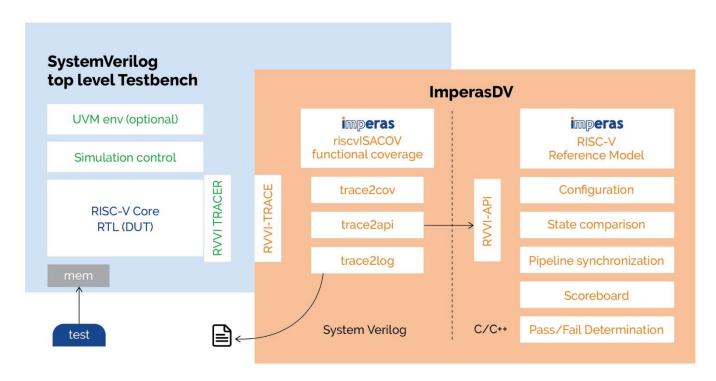

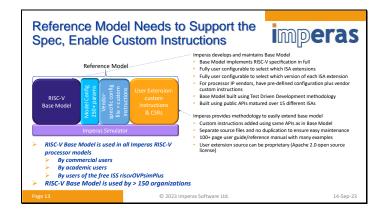

# **Larry Lapides**

# **Imperas Software Ltd**

**VP Worldwide Sales**

A Modern Fable: The Lost Art of Processor Verification

# **Platinum Sponsor**

### **Abstract**

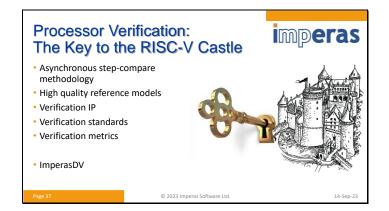

The open standard Instruction Set Architecture (ISA) of RISC-V offers new design flexibilities and opportunities, and is having a significant impact on the design side of many SoC projects. An optimized processor enables developers to unlock hidden value in performance, power savings, security, differentiated features, and an enduring market advantage.

While every SoC design team now has a free architecture license to build a custom RISC-V processor or extend an existing core with custom instructions, this also represents a surge in verification work and a step-change in verification complexity. With other ISAs, verification methodologies have largely been kept proprietary. Now within the RISC-V community, the art and science of processor verification is resurfacing. This represents a massive migration in verification responsibility, and the creation of a new verification ecosystem.

This talk outlines the various methodologies for RISC-V processor verification, which leverage established SoC verification technologies with UVM and SystemVerilog. The individual components of a step-compare methodology will be discussed, including reference model, verification IP, functional coverage and test generation. Detailed examples of successful, complex processor verification projects will be presented, including flows to support verification of complex events and architectures such as interrupts, Debug and privilege modes, multi-hart processors and multi-issue and out-of-order pipelines.

# **Biography**

Larry is currently VP Worldwide Sales at Imperas Software Ltd., and previously ran worldwide sales at EDA companies including Verisity Design (the top performing IPO of 2001 in the U.S.). Larry has about 30 years in software tools and EDA, plus time spent in infrared sensors and systems engineering. Larry holds a BA in Physics from the University of California Berkeley, a MS in Applied and Engineering Physics from Cornell University and a MBA from Clark University where he was an Entrepreneur-in-Residence during Fall 2006, when he developed and taught the course on Entrepreneurial Communication and Influence

## **Notes**

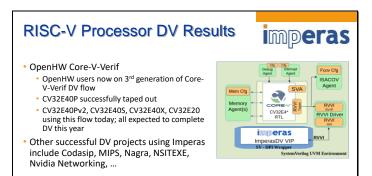

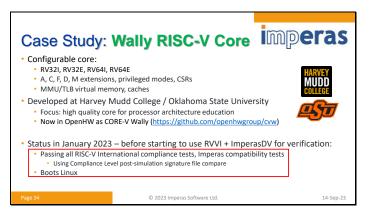

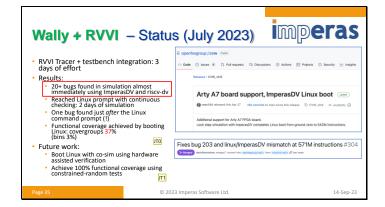

#### ImperasDV™ RISC-V Processor Verification Solutions

RISC-V is an open standard ISA (Instruction Set Architecture) that allows any developer to design and extend a custom processor, while remaining compatible with the growing ecosystem of supporting tools and software. The innovation and impact of RISC-V on the design side is driving new developments across all market segments and applications.

Now, with **ImperasDV**, developers have a dependable, reference model-based solution for verification that is compatible with the current UVM SystemVerilog methods for SoC verification.

www.imperas.com/imperasDV

**ImperasDV** and Imperas RISC-V processor verification technology is already in active use with many leading customers, some of which have working silicon prototypes and are now working on 2nd generation designs. These customers, partners, and users span the breadth of RISC-V adopters from open source to commercial; research to industrial; microcontrollers to high-performance computing.

A select sample of these include Codasip, Dolphin Design, EM Microelectronics (Swatch), Frontgrade Gaisler, Intrinsix, NSITEXE (Denso), Nvidia Networking (Mellanox), NXP, OpenHW Group, MIPS, Seagate Technology, Silicon Labs, Valtrix Systems, and Ventana Micro Systems, plus many others yet to be made public.

#### RISC-V Processor Functional Verification with RVVI & ImperasDV

- Verification IP

- Test & Coverage suites

- · RISC-V Reference model

#### A Modern Fable: The Lost Art of Processor Verification

Verification Futures – Austin

Larry Lapides 14 September 2023

#### Agenda

- RISC-V and processor verification

- RISC-V processor models

- RISC-V processor verification methodology

- Processor verification success

- Summary

#### Agenda

- RISC-V and processor verification

- RISC-V processor models

- RISC-V processor verification methodology

- Processor verification success

- Summary

#### RISC-V Is Why We Are All Worried **About Processor Verification**

- RISC-V is taking over the processor world, except for x86 Yes, that includes Arm

- RISC-V processor customization means that every RISC-V developer needs to verify the RISC-V processor

- Lost art? Processor IP vendors guard their verification methodology and details more than the IP itself

- With the verification flow, someone could reverse engineer a

- high quality processor

There are few public details about x86, Arm or Apple processor verification

**imperas**

#### **RISC-V Freedom Enables Domain Specific Processing**

- Who: RISC-V users include traditional semiconductor companies, and embedded systems companies now practicing vertical integration by developing their own SoCs

- What: RISC-V is an open instruction set architecture (ISA), it is not a processor implementation

- Where: RISC-V is growing in market segments where x86 (PCs, data centers) and Arm (mobile) architectures are not dominant

Small microcontrollers for SoC management, replacing proprietary cores

- Verticals such as IoT and automotive

- Horizontal markets such as security and AI/ML Deep embedded applications

- When: RISC-V processors are now used in over 30% of SoCs

- Why: The freedom of the open ISA enables users to develop differentiated domain specific processors and processing systems

#### Keys to RISC-V SoC Success

- 1) Processor IP

- Processor IP vendor

- Open source IP

- Build it yourself

- 2) Processor verification

- 3) Software porting, development, bring up, test

- All 3 areas need to account for the addition of custom features to the processor (because everyone adds custom features to the processor)

© 2023 Imperas Software Ltd.

#### Keys to RISC-V SoC Success

- Processor IP

Processor IP vendor

- Open source IP

- Build it yourself 2) Processor verification

- 3) Software porting, development, bring up, test

- Users of all 3 types of processor IP need to account for the addition of custom features to the processor (because everyone adds custom features to the processor)

- Success in processor verification requires a high-quality model of the processor

- Success in processor verification requires innovative technologies and methodologies *the lost art of processor verification*

© 2023 Imperas Software Ltd

#### **RISC-V Processor Complexity**

- RISC-V is a modular instruction set architecture

- Any extension (functional group of instructions, e.g. atomics, compressed, floating point, vector) can be added to the base processor

- Then add in interrupts, privilege modes, Debug mode, multi-hart (multi-core), etc. and it gets complex

- Then processor DV, tool chain development and other software development is needed

|                         | Andes<br>AX45MPV   |                    |  |  |  |  |

|-------------------------|--------------------|--------------------|--|--|--|--|

| IRQ's                   | Platform-Level Int | terrupt Controller |  |  |  |  |

| JTAG                    | Debug S            | Debug Support      |  |  |  |  |

| Trace Ports             | AX45V <sup>g</sup> | AX45V <sup>7</sup> |  |  |  |  |

| LM Access<br>Ports      | ILM DLM V          | ILM DLM V          |  |  |  |  |

| IO<br>Coherence<br>Port |                    | e Manager          |  |  |  |  |

|                         |                    | ,                  |  |  |  |  |

| <br> | <br>  |      |      |  |

|------|-------|------|------|--|

|      |       |      |      |  |

| <br> |       |      |      |  |

|      |       |      |      |  |

| <br> |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

| <br> | <br>  |      | <br> |  |

|      |       |      |      |  |

| <br> | <br>  |      | <br> |  |

|      |       |      |      |  |

| <br> | <br>  |      | <br> |  |

|      |       |      |      |  |

| <br> | <br>  | <br> | <br> |  |

|      |       |      |      |  |

|      | <br>_ |      | <br> |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

| <br> | <br>  | <br> | <br> |  |

|      |       |      |      |  |

| <br> | <br>  | <br> | <br> |  |

|      |       |      |      |  |

| <br> | <br>  |      | <br> |  |

|      |       |      |      |  |

| <br> | <br>— | <br> | <br> |  |

|      |       |      |      |  |

|      | <br>_ |      | <br> |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

|      |       |      |      |  |

#### **RISC-V Processing Subsystems**

- Multi-processor subsystems are commonly being developed using RISC-V cores

- · Application areas include DSP, AI/ML and packet processing

- This adds complexity to both the DV and software development tasks

TUV ASH, D READY Someon Makes

SMU System Ma DBG Debug Des NSITEXE Data Flow Processor

• RISC-V and processor verification

#### • RISC-V processor models

- RISC-V processor verification methodology

- Processor verification success

- Summary

#### **RISC-V Model Requirements**

- Model the ISA, including all versions of the ratified spec, and stable unratified extensions

- Model other behavioral components, e.g. interrupt controllers

- · Easily update and configure the model(s) for the next project

- User-extendable for custom instructions, registers, ...

- Model actual processor IP, e.g. Andes, MIPS, NSITEXE, OpenHW, SiFive, SweRV, ...

- $\bullet \ \ \text{Well-defined test process} \text{for the model!} \text{including coverage metrics}$

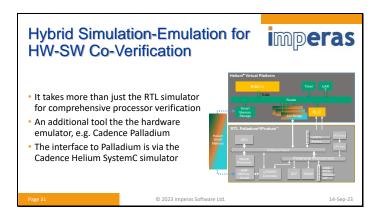

- Interface to other simulators, e.g. SystemVerilog (Xcelium), SystemC (Helium), Imperas virtual platform simulators

- Interface to software debug tools, e.g. GDB/Eclipse, Imperas MPD

- · Interface to software analysis tools including access to processor internal state, etc.

- Most RISC-V ISSs can meet one or two of these requirements

- Imperas models and simulators were built to satisfy these requirements, and matured through usage on non-RISC-V ISAs over the last 15+ years

© 2023 Imperas Software Ltd.

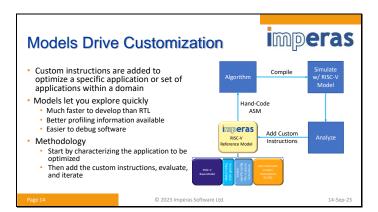

#### Imperas OVP RISC-V Fast **Processor Models**

- Use cases

Architecture analysis, including (especially) custom instructions

Software development, debug and test

Processor and SoC verification

- Existing Imperas Open Virtual Platforms (OVP) Fast Processor Models of ..

- ting iniperas Open witder Frationis (OVP) Fast Processor widels of an adventure of the Committee of the Comm

- Custom instructions easily added by user or by Imperas

New instructions are added in a side file so as not to perturb the verified model

Custom instructions are analyzed for effectiveness

- Models are built using Test Driven Development (TDD) methodology

- Tests are built at the same time as features are added Continuous Integration (CI) test flow used > 15,000 tests for models + simulator

- Additional testing by processor IP vendors to validate models

| J |

|---|

#### imperas Agenda • RISC-V and processor verification • RISC-V processor models RISC-V processor verification methodology • Processor verification success Summary

|                                       | © 2023 Imperas Software Ltd. | 14-Sep-23 | <br> |

|---------------------------------------|------------------------------|-----------|------|

|                                       |                              |           |      |

| OV Methodol                           | ISC-V Processor              | imperas   | <br> |

| B) Post-simulation to Synchronous ste | •                            | pre-2018) | <br> |

| o) Asynchronous co                    | ntinuous compare             |           | <br> |

| age 16                                | © 2023 Imperas Software Ltd. | 14-Sep-23 | <br> |

|                                       |                              |           |      |

#### 5 Levels of RISC-V Processor **DV Methodology**

- 1) Hello World

- 2) Self-checking tests (e.g. Berkeley torture tests pre-2018)

- 3) Post-simulation trace log file compare

- 4) Synchronous step-and-compare

- 5) Asynchronous continuous compare

#### 3) Post-Simulation Trace Log File Compare (Éntry Level DV)

- use random generator (ISG) to create tests

- during simulation of ISS write trace log file during simulation of RTL write trace log file

- at the end of both runs, run logs through compare program to see differences / failures

- ISS: riscvOVPsimPlus includes Trace and

- ISG: riscv-dv from Google Cloud / Chips

- Free ISG: https://github.com/google/riscv-dv

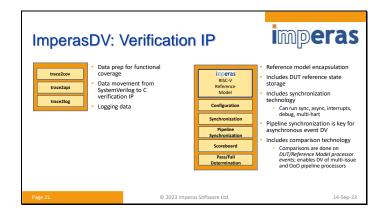

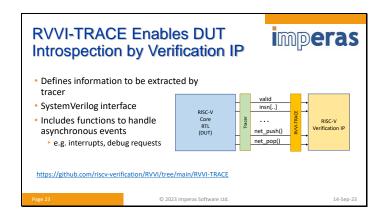

#### 5) Async Continuous Compare (Highest Quality DV Methodology)

- · Asynchronous events are driven into the DUT

- Tracer informs reference model about async events

- Verification IP handles async events, scoreboarding, comparison, pass/fail

- Asynchronous continuous compare methodology is needed to support features such as interrupts, privilege modes, Debug mode, multi-hart, multi-issue and OoO pipeline, ...

© 2023 Imperas Software Ltd

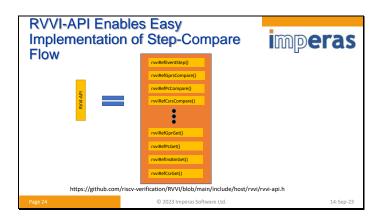

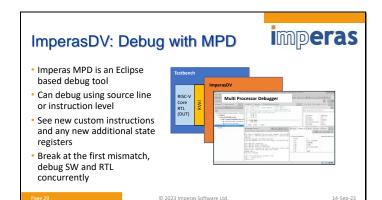

#### ImperasDV Components

- Reference model needed for comparison of correct behavior

- Verification IP provides ease of use, saves time and resources

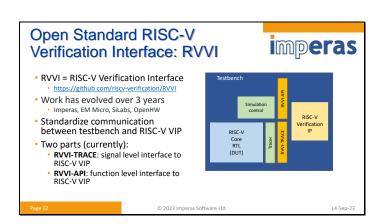

- RVVI standard provides communication between test bench and reference model subsystem

- Test suites: riscvISATESTS, directed test suites for difficult extensions

- MultiProcessor Debugger (MPD) enables RTL-reference model co-debug

- Feature selection and design choices require serious consideration due to implications of every decision Every addition dramatically compounds verification complexity Adds schedule, resources, quality costs == big risks

- · Before 2021, no off-the-shelf toolkit/products available for DV of processors ... then came ImperasDV

- ImperasDV, with async continuous compare methodology, is needed to support features such as interrupts, privilege modes, Debug mode, multi-hart, multi-issue and OoO pipeline, ...

| <br> |

|------|

| <br> |

|      |

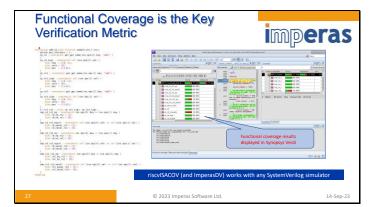

#### Functional Coverage of RISC-V Instructions: Scope

- There are many different instructions in the RV64 extensions:

- Integer: 56, Maths: 13, Compressed: 30, FP-Single: 30, FP-Double: 32

- Bitmanip: 47 Krypto-scalar: 85 Vector: 356,

- For RV64 that is 967 instructions...

- Each instruction needs SystemVerilog covergroups and coverpoints

- 10-40 lines of SystemVerilog for each instruction

- 10,000-40,000++ lines of code to be written

- · Not design or core specific

#### riscvISACOV Is Automatically imperas Generated SystemVerilog Functional Coverage

- riscvISACOV provides functional coverage of Instructions and operands

- Roadmap includes CSRs and data hazards

- Imperas tools can automatically generate functional coverage code for custom instructions

© 2023 Imperas Software Ltd.

#### Test Stimuli

- · Instruction Stream Generator (ISG) and/or directed tests

- · Directed tests

- Imperas have developed a directed RISC-V test generator, instruction coverage verification IP and a mutating fault simulator (for test qualification) to provide high quality test suites

- The generated tests suites are targeting architectural compatibility as defined in the RVIA architectural test working group coverage requirements

- Free Imperas architectural validation test suites (50+), including RV32/64 I, M, C, F, D, B, K, V, P

- https://github.com/riscv-ovpsim/imperas-riscv-tests

Imperas commercial directed test suites for vector extension, protected memory components

- $\label{lem:configuration} \textbf{Can support any RISC-V vector or PMP configuration; the user selects the configuration and Imperas generates the test suite}$

© 2023 Imperas Software Ltd.

|  | <br> |      |  |

|--|------|------|--|

|  | <br> |      |  |

|  | <br> | <br> |  |

|  | <br> |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  | <br> | <br> |  |

|  | <br> |      |  |

|  | <br> |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  | <br> |      |  |

|  |      |      |  |

|  |      |      |  |

|  | <br> | <br> |  |

|  | <br> | <br> |  |

|  | <br> |      |  |

|  | <br> |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

|  |      |      |  |

Software Debug and Analysis Tools

Automatically Work With the

Custom Instructions

\*\*Tools\*\*

\*\*Too

## Agenda RISC-V and processor verification RISC-V processor models RISC-V processor verification methodology Processor verification success Summary

Page 33

2023 Imperas Software Ltr

# Agenda RISC-V and processor verification RISC-V processor models RISC-V processor verification methodology Processor verification success Summary

Thank you

Larry Lapides

LarryL@imperas.com

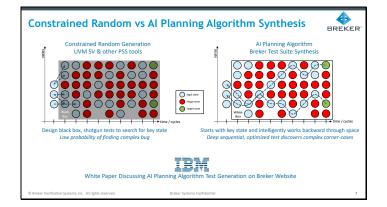

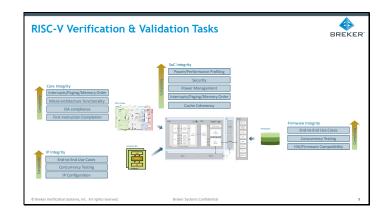

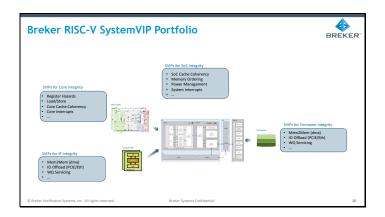

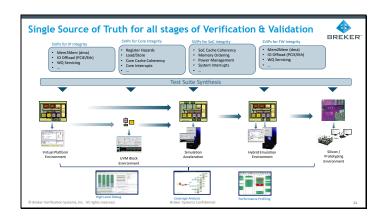

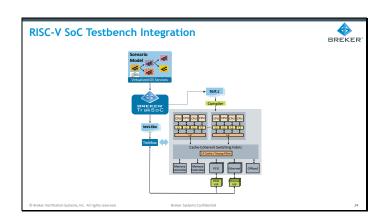

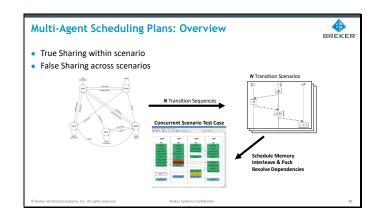

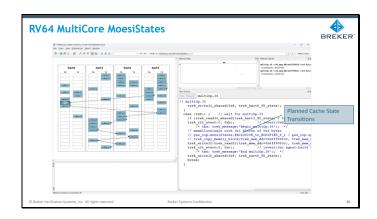

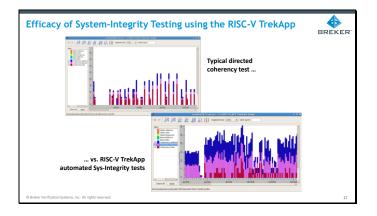

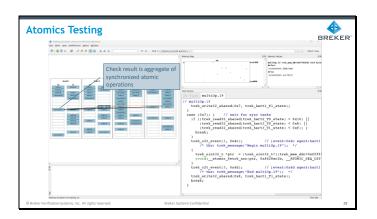

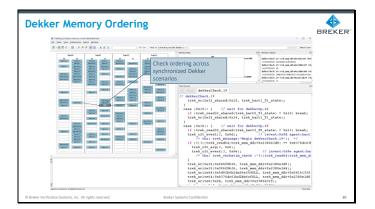

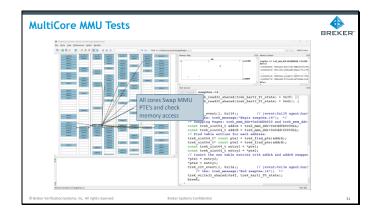

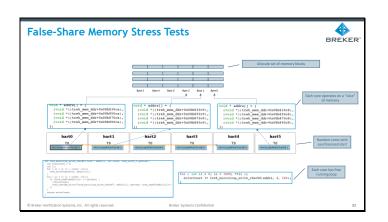

### **Adnan Hamid**

#### **Breker Verification Systems**

Founder and CTO

## Advanced RISC-V Verification Technique Learnings for SoC Validation

#### **Gold Sponsor**

#### **Abstract**

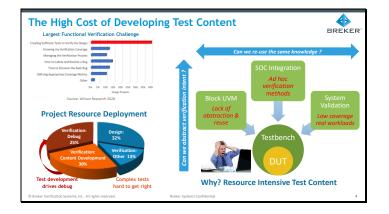

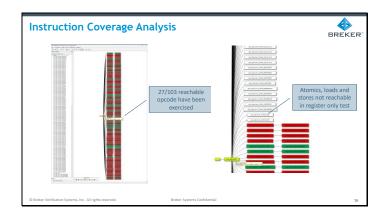

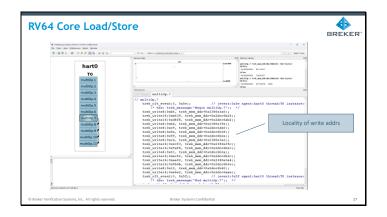

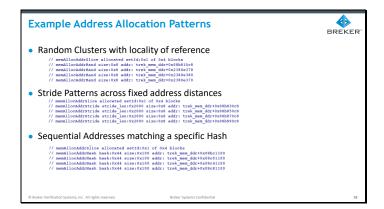

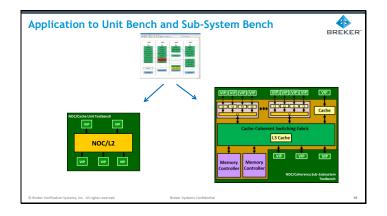

The verification of application-level RISC-V cores require specialized techniques and approaches previously the purview of Arm, Intel and other processor companies. The open and customizable RISC-V cores have led to many new processor development teams with unique microarchitectural approaches that require extensive verification.

Breker has found that a key aspect of RISC-V core verification involves its smooth operation within the larger system. For example, load-store anomalies, asynchronous interrupt mechanisms, and security protocols are just a few of many issues that must be fully analysed. In developing new test approaches for these and other scenarios, their application in more general System-on-Chips has become apparent, and indeed these methods can track complex system corner cases that will never be detected simply by running real workloads or benchmarks. This presentation will describe many techniques useful for RISC-V core verification, and also how they may be applied to the broader SoC at large for high coverage verification.

#### **Biography**

Adnan is the founder and CTO of Breker and the inventor of its core technology. Noted as the father of Portable Stimulus, he has over 20 years of experience in functional verification automation, much of it spent working in this domain.

Prior to Breker, he managed AMD's System Logic Division, and also led their verification team to create the first test case generator providing 100% coverage for an x86-class microprocessor. In addition, Adnan spent several years at Cadence Design Systems and served as the subject matter expert in system-level verification, developing solutions for Texas Instruments, Siemens/Infineon, Motorola/Freescale, and General Motors.

Adnan holds twelve patents in test case generation and synthesis. He received BS degrees in Electrical Engineering and Computer Science from Princeton University, and an MBA from the University of Texas at Austin.

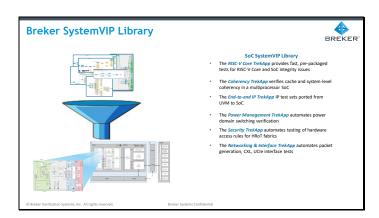

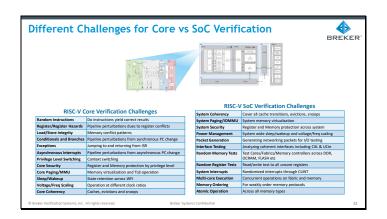

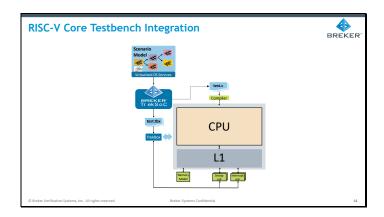

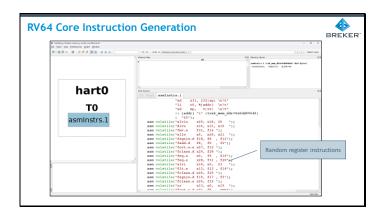

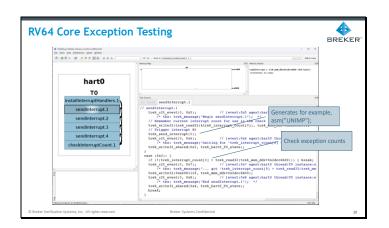

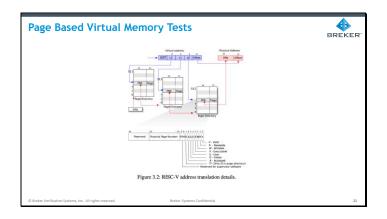

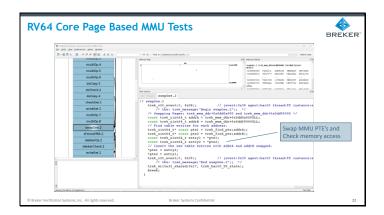

#### RISC-V Core SystemVIP

| Random Instructions       | Do instructions yield correct results              |

|---------------------------|----------------------------------------------------|

| Register/Register Hazards | Pipeline perturbations dues to register conflicts  |

| Load/Store Integrity      | Memory conflict patterns                           |

| Conditionals and Branches | Pipeline perturbations from synchronous PC change  |

| Exceptions                | Jumping to and returning from ISR                  |

| Asynchronous Interrupts   | Pipeline perturbations from asynchronous PC change |

| Privilege Level Switching | Context switching                                  |

| Core Security             | Register and Memory protection by privilege level  |

| Core Paging/MMU           | Memory virtualization and TLB operation            |

| Sleep/Wakeup              | State retention across WFI                         |

| Voltage/Freq Scaling      | Operation at different clock ratios                |

| Core Coherency            | Caches, evictions and snoops                       |

|                           |                                                    |

#### SoC SystemVIP

| Test Cores/Fabrics/Memory controllers                     |

|-----------------------------------------------------------|

| Read/write test to all uncore registers                   |

| Randomized interrupts through CLINT                       |

| Concurrent operations on fabric and memory                |

| For weakly order memory protocols                         |

| Across all memory types                                   |

| Cover all cache transitions, evictions, snoops            |

| System memory virtualization                              |

| Register and Memory protection across system              |

| System wide sleep/wakeup and voltage/freq scaling         |

| Generating networking packets for I/O testing             |

| Analyzing coherent interfaces including CXL & UCIe        |

| Layering concurrent tests to check operation under stress |

| Executing SW on block or sub-system without processor     |

|                                                           |

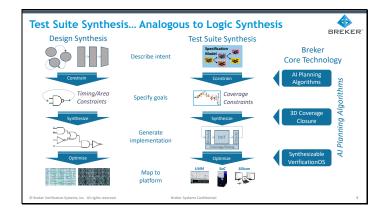

#### **Automated Test Synthesis**

## Fast test availability Quality SystemVIP / easy composition

#### Ultrahigh coverage Auto bug tracking in complex scenarios

#### Portable & Reusable Same tests across platforms and projects

#### Agenda

- Test Suite Synthesis and SystemVIP

- RISC-V Core Verification SystemVIP

- RISC-V SoC Verification SystemVIP

© Breker Verification Systems, Inc. All rights reserved.

Breker Systems Confidentia

#### Agenda

- Test Suite Synthesis and SystemVIP

- RISC-V Core Verification SystemVIP

- RISC-V SoC Verification SystemVIP

© Breker Verification Systems, Inc. All rights reserved

Breker Systems Confidential

#### A Look At RISC-V

- Open Instruction Set Architecture (ISA) creating a discontinuity in the market

- Appears to be gaining significant traction in multiple applications

- Significant verification challenges

- $\circ\,$  Arm spends \$150M per year on  $10^{15}\, verification$  cycles per core

- $\circ\,$  Hard for RISC-V development group to achieve this same quality

- $\circ\,$  Lots of applications expands verification requirements

- o Requires automation, reuse and other new thinking

© Breker Verification Systems, Inc. All rights reserved.

Breker Systems Confidentia

| <br> | <br> |

|------|------|

| <br> | <br> |

| <br> | <br> |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

| <br> |      |

| <br> | <br> |

| <br> | <br> |

| <br> | <br> |

|      |      |

|      |      |

| <br> |      |

|      |      |

|      |      |

|      |      |

|      |      |

| <br> | <br> |

|      |      |

|      |      |

| <br> | <br> |

| <br> | <br> |

|      |      |

|      |      |

## RISC-V SoC Memory Ordering: Dekker Algorithm • Assume initial state A=0, B=0 • The Dekker Algorithm States core 0: ST A, 1; MEM\_BARRIER; LD B core 1: ST B, 1; MEM\_BARRIER; LD A error iff ( A == 0 && B == 0 ) • This is a test for a weakly ordered memory system • Such a system must preserve the property that a LD may not reorder ahead of a previous ST from the same agent

| Thanks for Listening! Any Questions? |  |

|--------------------------------------|--|

|                                      |  |

## **Notes**

## **Balram Naik Meghavath**

#### **Broadcom Ltd**

Sr Staff Engineer

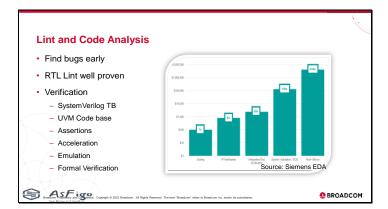

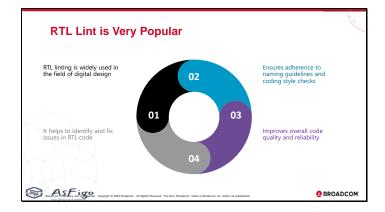

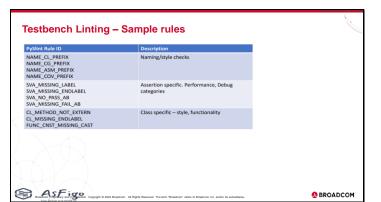

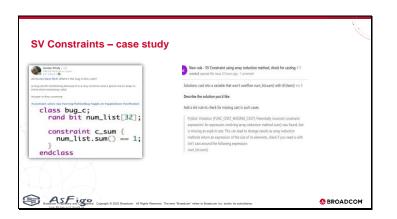

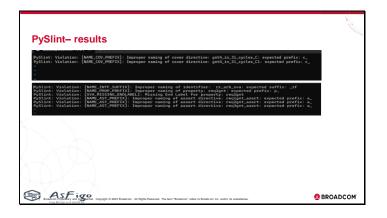

## Improve the Quality of the Testbenches using specialized PySlint solutions

#### **User Paper**

#### **Abstract**

Simulation is the most common RTL verification technique, involving the execution of testbenches are essential for the verification of the designs. SystemVerilog and UVM have been widely adopted over the last two decades. However, the complex nature of these languages/methodologies can make it difficult for junior-level engineers to create maintainable and reusable code.

Static linting checks have been widely used for RTL design, but they have not been used as widely adopted for Testbenches. In this talk, we share our experience in using a popular open-source framework named PySlint to lint-check SystemVerilog UVM Testbeneches.

We show how PySlint can be used to identify potential problems in SV-UVM Testbenches, such as coding style violations, potential bugs, and potential performance bottlenecks. We also show how PySlint can be used to generate reports that can help engineers to improve the quality of their Testbenches buildling a robust verification environment process. Some key components of a robust verification environment includes, Testbenches, coverage matrics, Assertions, regression testing.

We believe that PySlint can be a valuable tool for improving the quality of SystemVerilog UVM testbenches. By using PySlint, engineers can identify and fix potential problems in their testbenches early in the development process, which can help to prevent costly delays and errors.

#### SystemVerilog:

1800-2017 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language

#### UVM Use Guide:

https://www.accellera.org/images/downloads/standards/uvm/uvm\_users\_guide\_1.2.pdf

#### PySlink:

https://github.com/svenka3/pyslint

#### **Biography**

15+ years of Design Verification exp.

Prior to Broadcom, I worked for Microchip, Western Digital.

My Verification expertise from IP level to SOC subsystems

Initially, I worked for VIP development, Net works chips, Mobile chips, and Storage product lines, Last 10 years mainly with Wireless products, **GPS** and **Bluetooth**, **Wifi** SoC's.

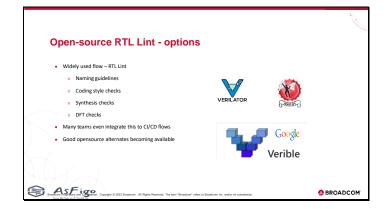

#### **TB Lint - Challenges and Alternatives**

- New Paradigm: Code analysis approaches changing

- Lack of good parsers/tools/API for newer languages

- Slang Verible, Svlint, and PySlint are good opensource alternatives

- Provide flexibility and customization options

Brancon Populary and Senial. Copyright 0.2023 Brandcon. All Rights Reserved. The Item "Brandcon" refers to Brandcon Inc. and/or its subsidiaries

**® BROADCOM**

#### **Testbench Linting**

- New paradigm

- Old/proven concept

- Lack of good parsers/tools/API

- · Verible C++ based rules

- · Svlint Rust based, custom plugin

- UVMLint Python based, custom plugin for UVM TB

- https://github.com/AsFigo/UVMLint

- PySlint Python based, works on top of slang/pyslang pkg

| The same of the sa |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |