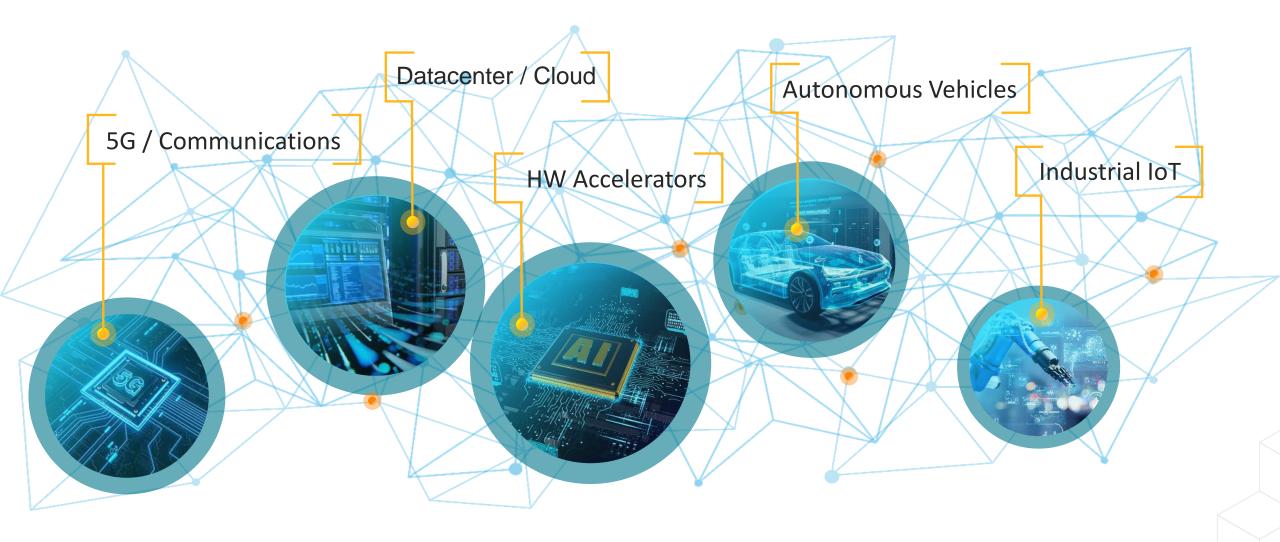

# 5 Generational Trends...All Anchored Around Compute

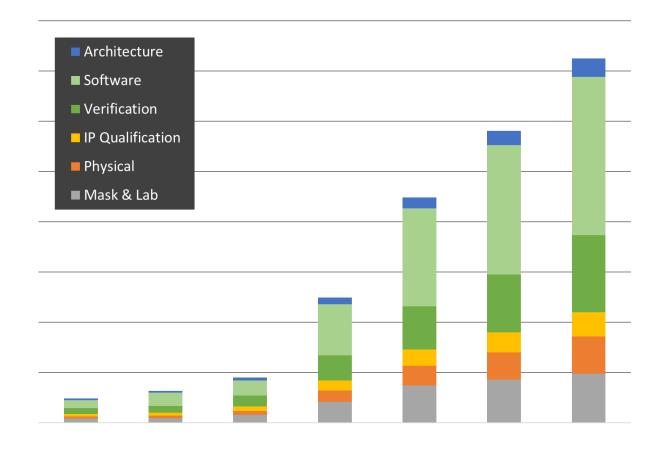

# The Scale of the Problem is Outpacing Engineering Resources

More Annual Design

**4X**

Over the Next Decade

(<=10nm)

Source: IBS Global Semiconductor Industry Service Report: Design Activities and Strategic Implications, July 2022 Source: Cadence analysis

**Transistor Count** Increasing 100X Over the Next Decade

Source: Cadence analysis

Not Enough Engineers

Engineering Talent Shortage Now Top Risk Factor

FEBRUARY 25, 2019 - BY: MARK LAPEDUS

Source: https://semiengineering.com/engineering-talent-shortage-now-top-risk-factor/

Plus new (additional) requirements! E.g. power aware verification, functional safety verification

# Total Cost of Silicon – Industry Trend

IBS, Global Semiconductor Industry Service Report July 2022

# Amateurs talk about strategy... ...professionals talk about logistics.

(most commonly attributed to) **Omar Bradley**General, United States Army

# Package Throughput = Engines x Logistics

Best Logistics

#### **UPS – We Love Logistics**

Van

Truck

**Plane**

Best Engines

Prep time: 10mins

Speed: 25mph

Reach: Front door

30mins 60mph Warehouse

Few hours 600mph Airport

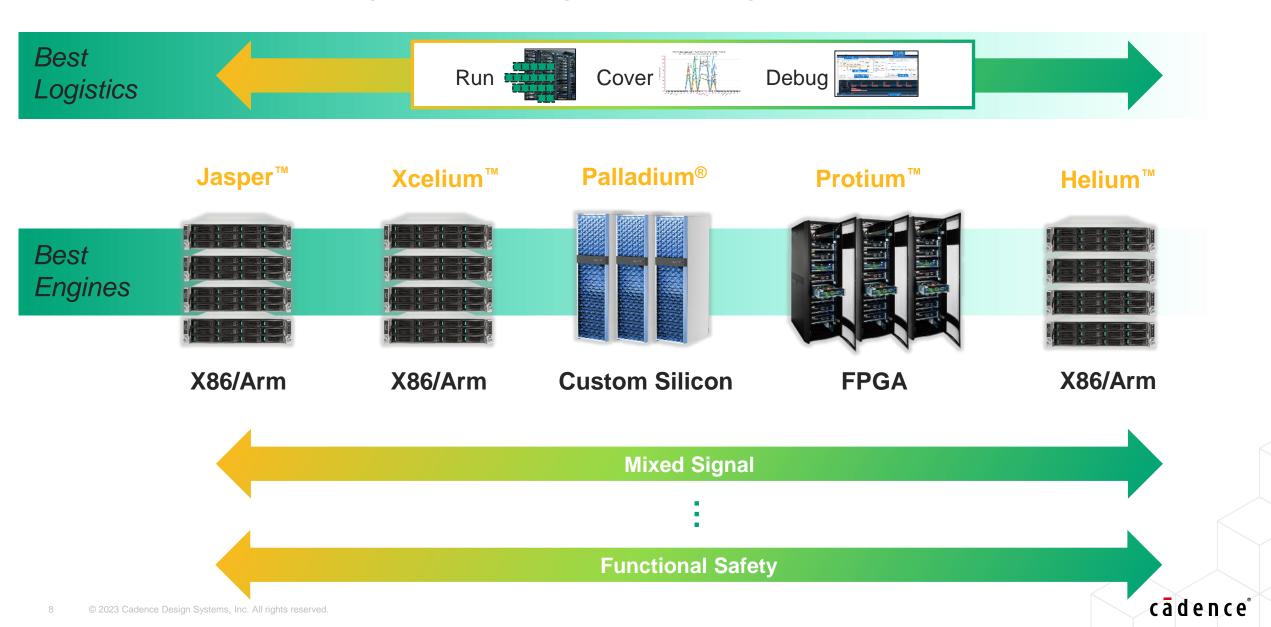

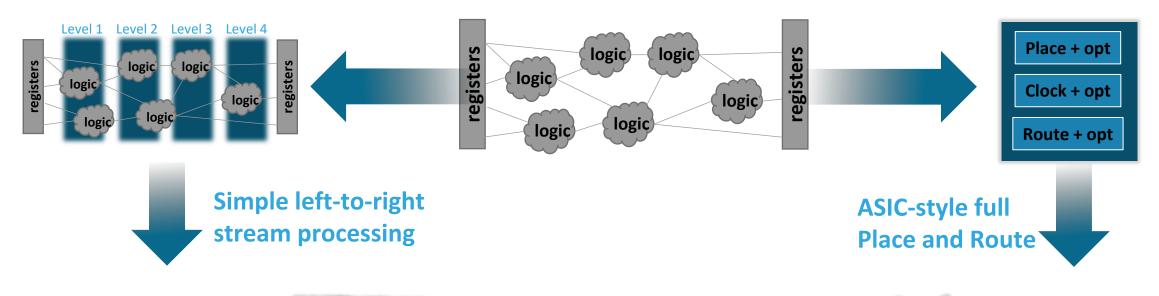

# Verification Throughput = Engines × Logistics

Best Logistics

#### **Verification Logistics**

Best Engines

X86 or Arm®-based server

**Custom Processor**

**FPGA**

**Compile Time:** Minutes

Speed: 100Hz

Reach: IP Debug

Few Hours

1MHz

SoC Debug

1-2 Days

5MHz+

Software Debug

# Verification Throughput = Engines × Logistics

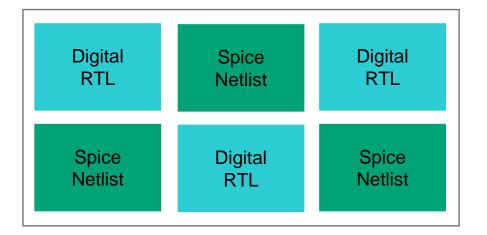

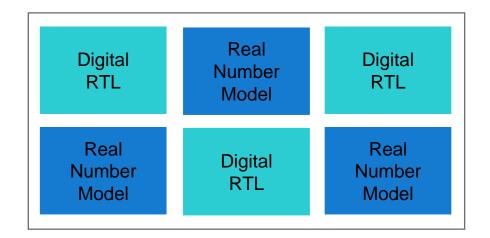

# **Xcelium Mixed Signal Simulation**

#### **Analog Mixed Signal (AMS)**

#### **Digital Mixed Signal (DMS)**

#### **Unified Debug, Testbench, and Coverage**

#### **Xcelium RNM**

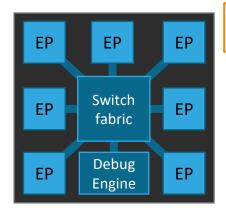

## Domain-Specific Hardware for Simulation Acceleration

Fast predictable compile Flexible debug

Debug your Software

Highest Performance

**FPGA**

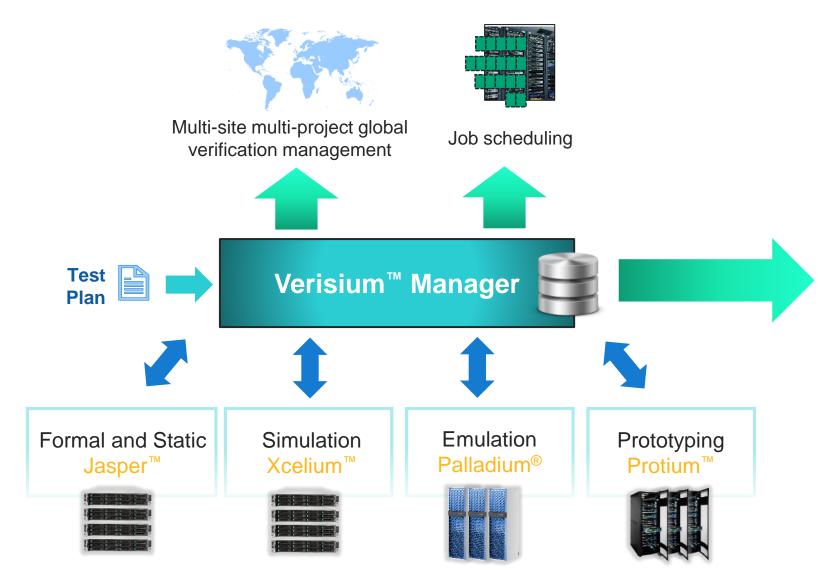

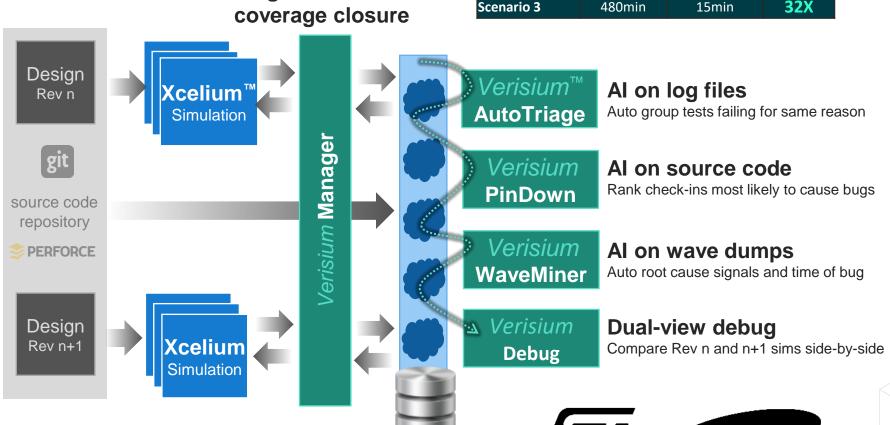

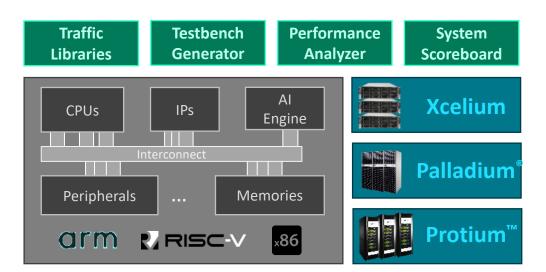

# Engines x Logistics with Verisium Manager

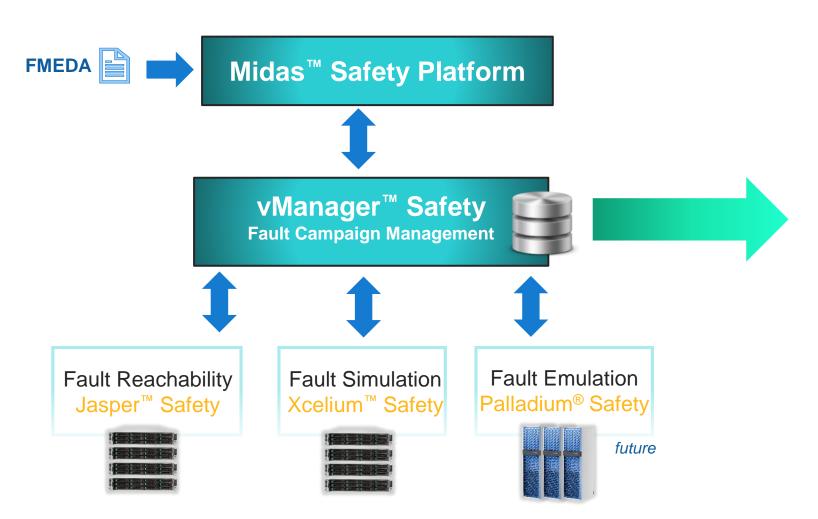

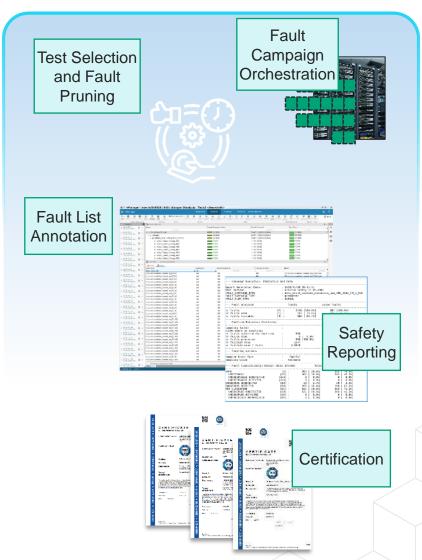

# Engines x Logistics for Functional Safety

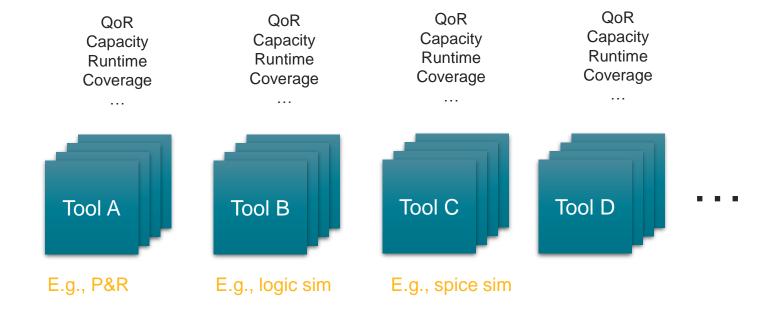

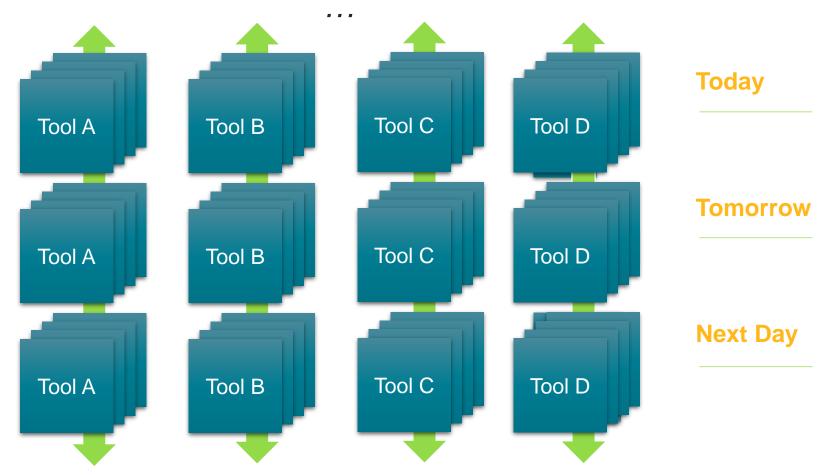

### **EDA 1.0**

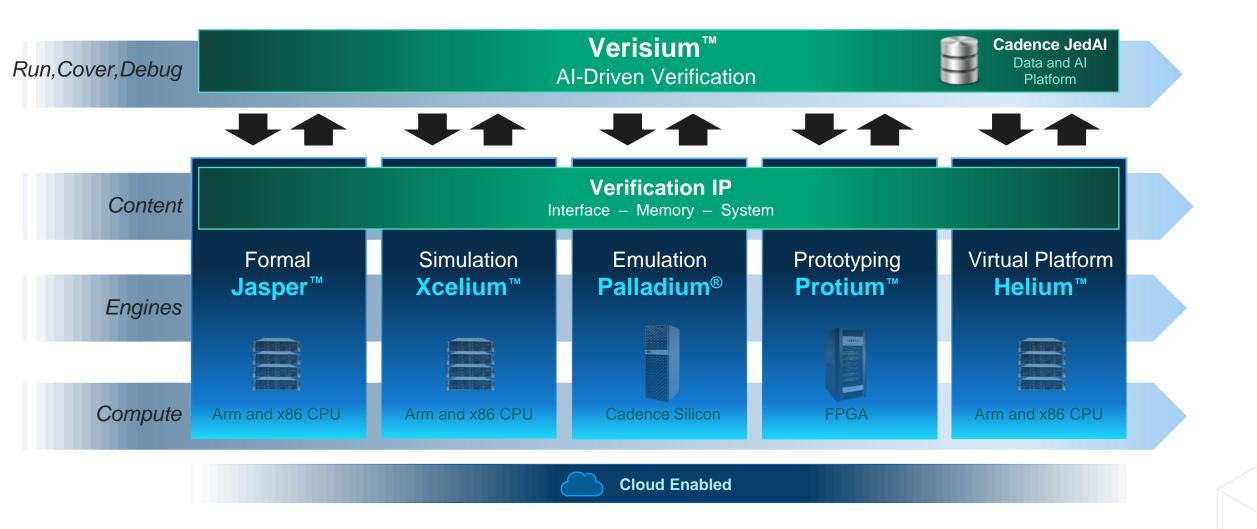

# **User Perspective**

### Meet PPA Goals Meet Coverage Goals

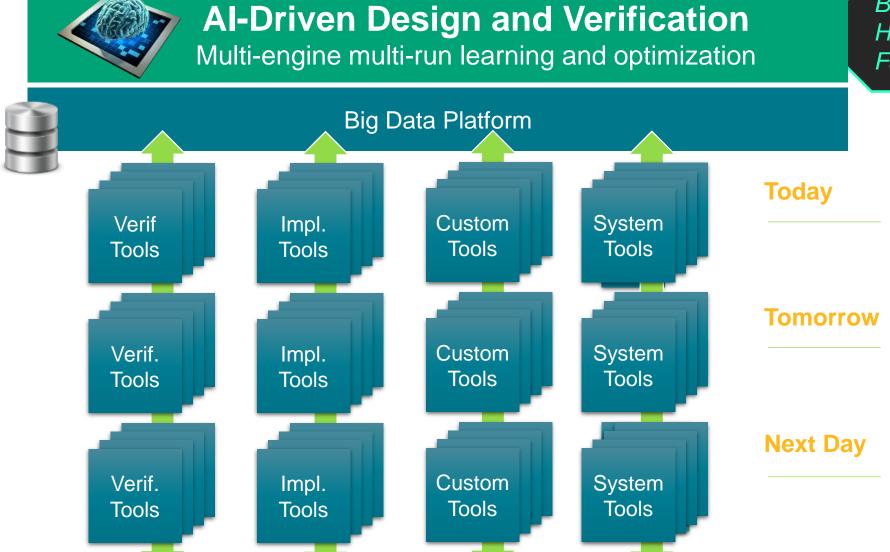

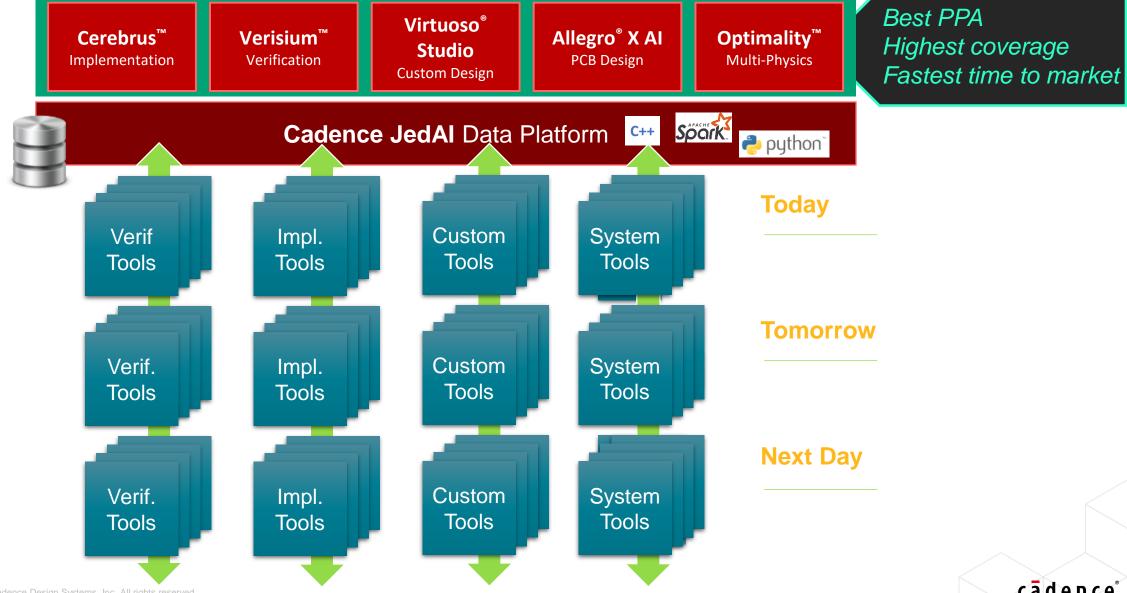

#### **Next-Generation EDA**

Best PPA

Highest coverage

Fastest time to market

#### Cadence EDA 2.0 Solutions

#### Verisium Al-Driven Verification

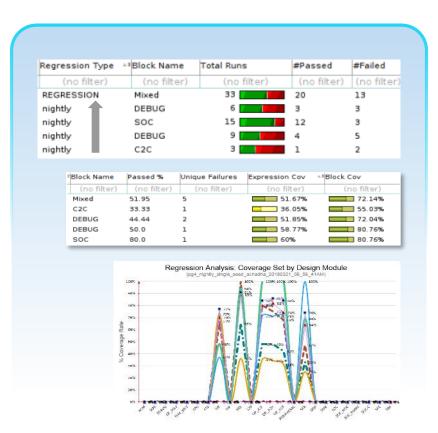

# Manage test runs and

#### **Customer Case Study**

| Time to Debug | <b>Current Flow</b> | Verisium Flow | Speed-up |

|---------------|---------------------|---------------|----------|

| Scenario 1    | 300min              | 10min         | 30X      |

| Scenario 2    | 90min               | 10min         | 9X       |

| Scenario 3    | 480min              | 15min         | 32X      |

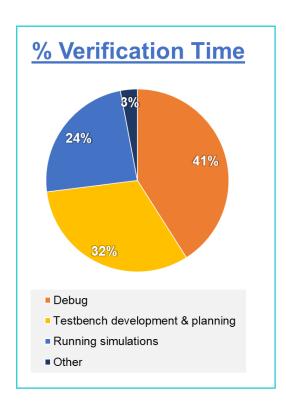

Wilson Research Group, October 2020

Cadence JedAl Data and Al Platform

MEDIATEK

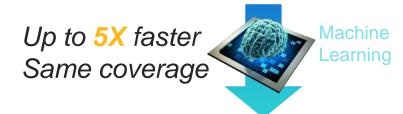

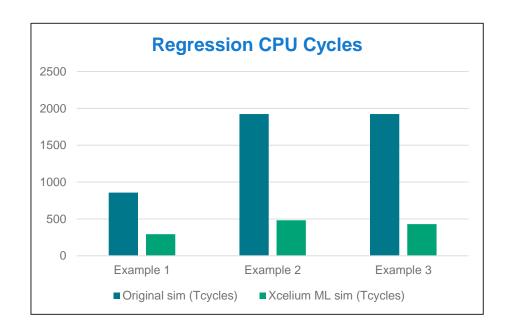

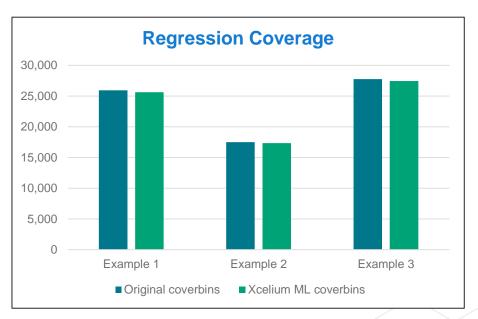

#### Al-Driven Simulation Performance

Randomized

Test Suite

Run N

Xcelium™ ML

Randomized Test Suite Run N+1

#### Al-Driven Formal Proof

# Proof Profiling Data

Keep engine-level settings that worked before

#### **Proof Caching**

Reuse existing result if constraints and COI unchanged

#### **Proof Orchestration**

Use Machine Learning to find the best proof algorithm settings

**Multi-run optimization**

+AI

#### **Proof Success Rate**

| Testcase | Baseline | <b>Smart Proof</b> | Gain |

|----------|----------|--------------------|------|

| Α        | 50%      | 59%                | 1.2X |

| В        | 69%      | 69%                | 1.0X |

| С        | 12%      | 25%                | 2.1X |

| D        | 44%      | 83%                | 1.9X |

| E        | 57%      | 94%                | 1.6X |

| F        | 68%      | 69%                | 1.0X |

| Total    | 53%      | 71%                | 1.3X |

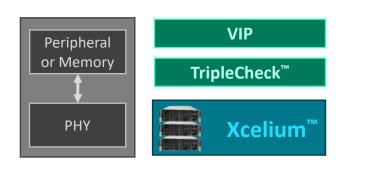

# Extending the Reach of Verification IP

#### **Interface and Memory VIP**

- Industry's broadest portfolio

- Verify compliance and cover the corner cases with TripleCheck

- Highest performance with C-based kernels

- System-level tests up and running in a day

- Validate PCle® for Arm SBSA

- Boot Linux and Windows over PCIe

#### Cadence Verification Solution

# Thank You

# cādence®

© 2023 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or registered trademarks or registered trademarks or trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks or trademarks or trademarks are the property of their respective owners.