# Verification Makeover with RISC-V Processor Designs

Lavanya J | CEO/Founder | Vyoma

#### **IITM SHAKTI RISC-V Efforts**

Vyoma - VaaS Platform for RISC-V Verification

Incubated @ IITM Pravartak

Technologies Foundation

**DIR-V Startup**

12+ years of industry experience (with IBM, ARM & Rambus) and academic with an MS from IIT Madras. Passionate about making design verification fun for the masses!

#### RISC-V Business & Verification

RISC-V Processor Verification as a foundation to provide the next-gen verification methodology and infrastrucure

Makeover Components

SHAKTI Verification

Vyoma's UpTickPro

Quality

Time to Market

RISC-V

Business

Success of the design companies in the growing RISC-V Processor and Subsystem business

Customization

#### **RISC-V Business**

### RISC-V Verification

Quality

Test and Coverage Quality

Time to Market

Methodology and Infrastructure

Customization

Verification IPs

What does it mean for Verification?

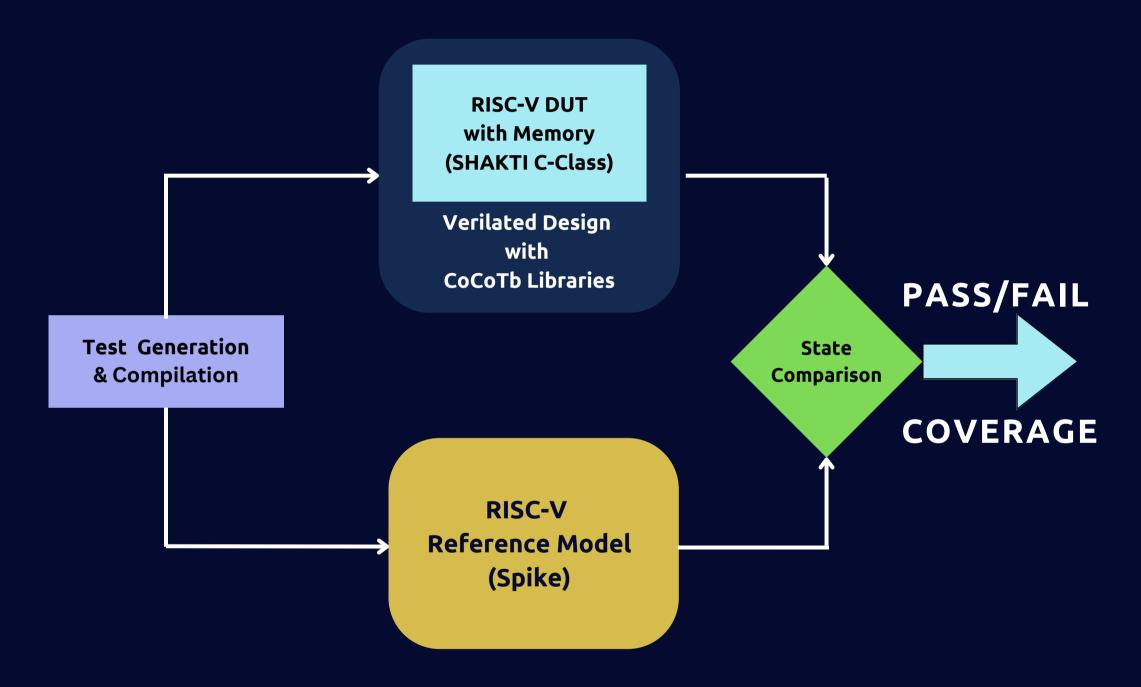

**TEST BENCH**

REFERENCE MODEL

**SCOREBOARD**

**TOOLCHAIN & INFRA**

**COVERAGE**

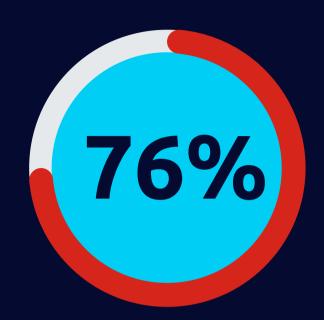

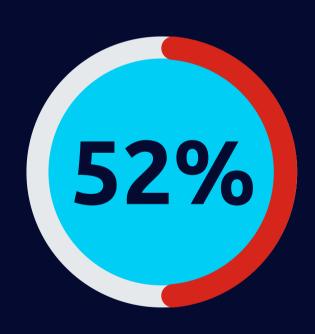

# The Wakeup Call

76% of today's designs **DO NOT** achieve first-silicon success

Logic and functional flaws are the leading cause of re-spins

Source: Wilson Research Group and Siemens EDA, 2022 Functional Verification Study

# Makeover Tests & Coverage

Configurable Test Plugins

Re-use the Python Ecosystem

Generative AI Tests

- One generator does not filt ALL scenarios.

- Leverage open-source RISC-V generators,

customize for RISC-V Designs & <u>Parallelize</u> it!

- Ready to deploy VIPs in the form of test templates or plugins and their quality defined using the ISA coverage metrics

Chatbotting Tests and their Coverage!

#### Makeover Test Bench

Constraint based randomization

```

1 class FinalRandomized(Randomized):

def __init__(self, x):

Randomized.__init__(self)

self.x = x

self.y = 0

self.z = 0

# define y as a random variable taking values from 0 to 9

add_rand("y", list(range(10)))

10

11

# define z as a random variable taking values from 0 to 4

12

add_rand("z", list(range(5)))

13

14

# hard constraint

15

add_constraint(lambda x, y: x !=y)

# multi-dimensional distribution

16

17

add_constraint(lambda y, z: y + z)

19 # create randomized object instance (default values at this point)

20 obj_ = FinalRandomized(5)

21 # randomize object with additional contraint

22 obj_.randomize_with(lambda z : z > 3)

```

#### Pythonize Test Bench

#### Makeover Test Bench

Constraint based randomization

#### Test Bench Components

```

1 class MyScoreboard(Scoreboard):

2   def compare(self, got, exp, log, **_):

3     if got != exp:

4         self.errors += 1

5         log.error("Received transaction differs from expected output.")

6     if self._imm:

7         raise TestFailure("DUT differs from model.")

8     ...

9

10

11 self.scoreboard = MyScoreboard(dut, fail_immediately=True)

12 self.scoreboard.add_interface(self.output_monitor, self.expected_output, srict_type=False)

13

```

#### Pythonize Test Bench

#### Makeover Test Bench

Constraint based randomization

Test Bench Components

Coverage Definition

```

1 import cocotb

2 from cocotb_coverage.coverage import *

3

4 Adder_Coverage = coverage_section (

5   CoverPoint("top.a", vname="a", bins = list(range(0,16))),

6   CoverPoint("top.b", vname="b", bins = list(range(0,16))),

7   CoverCross("top.cross_cover", items = ["top.a", "top.b"])

8 )

9

10 @Adder_Coverage

11 def adder_model(a: int, b: int) -> int:

12   """ model of adder """

13   return a + b

```

#### Pythonize Test Bench!

#### Makeover Tools and Infrastructure

Containerized environment for different designs

Same Infra for Development, Regression and Production release

Reliably Scalable for leveraging the cloud compute

#### Dockerize the Infra!

#### Makeover Verification

VIP Plugins and Generative AI tests

Efficiency

Pythonize

Productivity

Dockerize

Scalability

Ensures High Quality Designs a Reality

# Vyoma

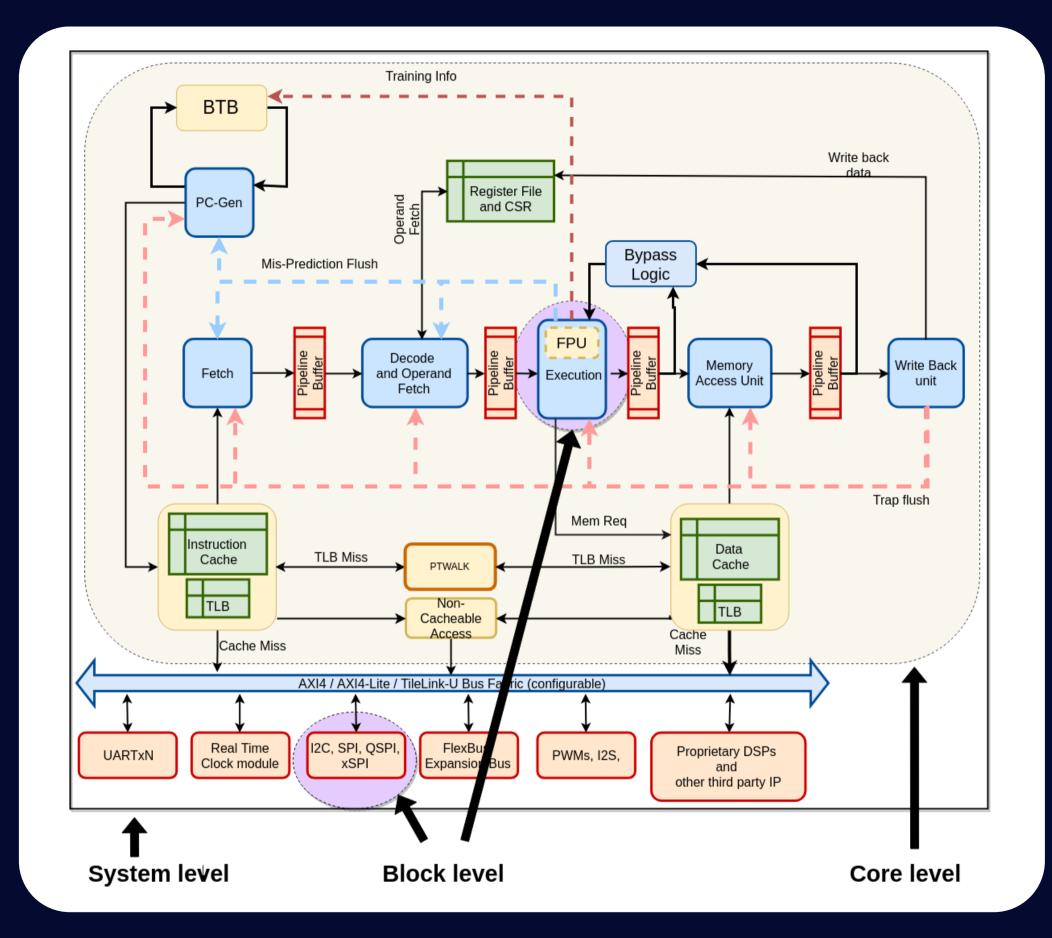

# SHAKTI C-Class

In-Order RISC-V

TOOLCHAIN & INFRA

- RTL Built for different configurations and verification abstractions

- Configurations can be different test memory sizes, simulation and FPGA builds

- Design configurations: with or without debug, microarch configurations

# **Test Templates**

TEST BENCH

REFERENCE MODEL

SCOREBOARD

TOOLCHAIN & INFRA

**COVERAGE**

- One generator does not filt ALL scenarios.

- Leverage open-source RISC-V generators,

customize for SHAKTI Designs & <u>Parallelize</u> it!

- Ready to deploy VIPs in the form of test templates and their quality defined using the ISA coverage metrics

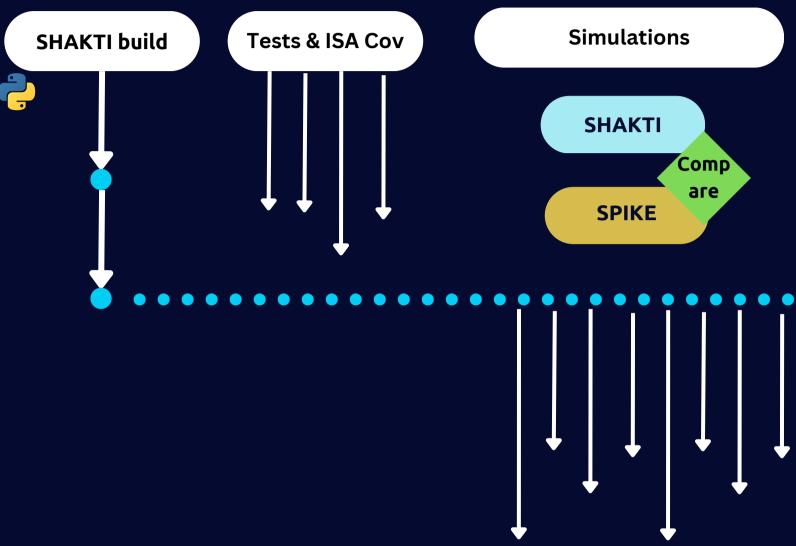

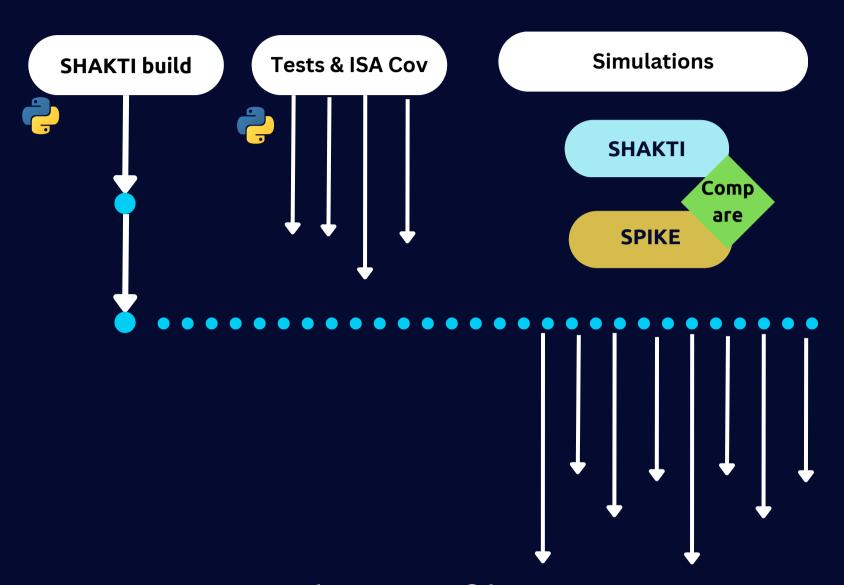

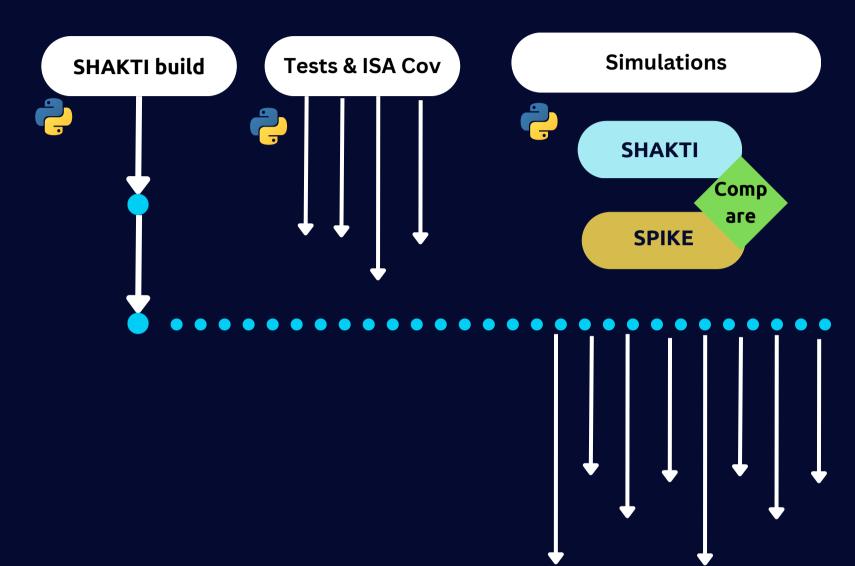

# Test Bench & Simulations

- CoCoTb based Python test benches following UVM methodology

- On-the-fly Processor state comparison

- Utmost care taken to re-use and make it configurable

- Simulations -> Parallelize, Parallelize, Parallelize!

COVERAGE ©

#### **Ground Realities**

- Apple to Apple language or Performance Comparisons

- Assertions, TB debug capability in the waveforms

- Can handle complexity? In-order/OOO Cores/ Multi-core (WIP)

- Open source and Python Ecosystem support

- Productivity: Faster ramp-up, Rapid Verif DevOps

Verification of the Future!

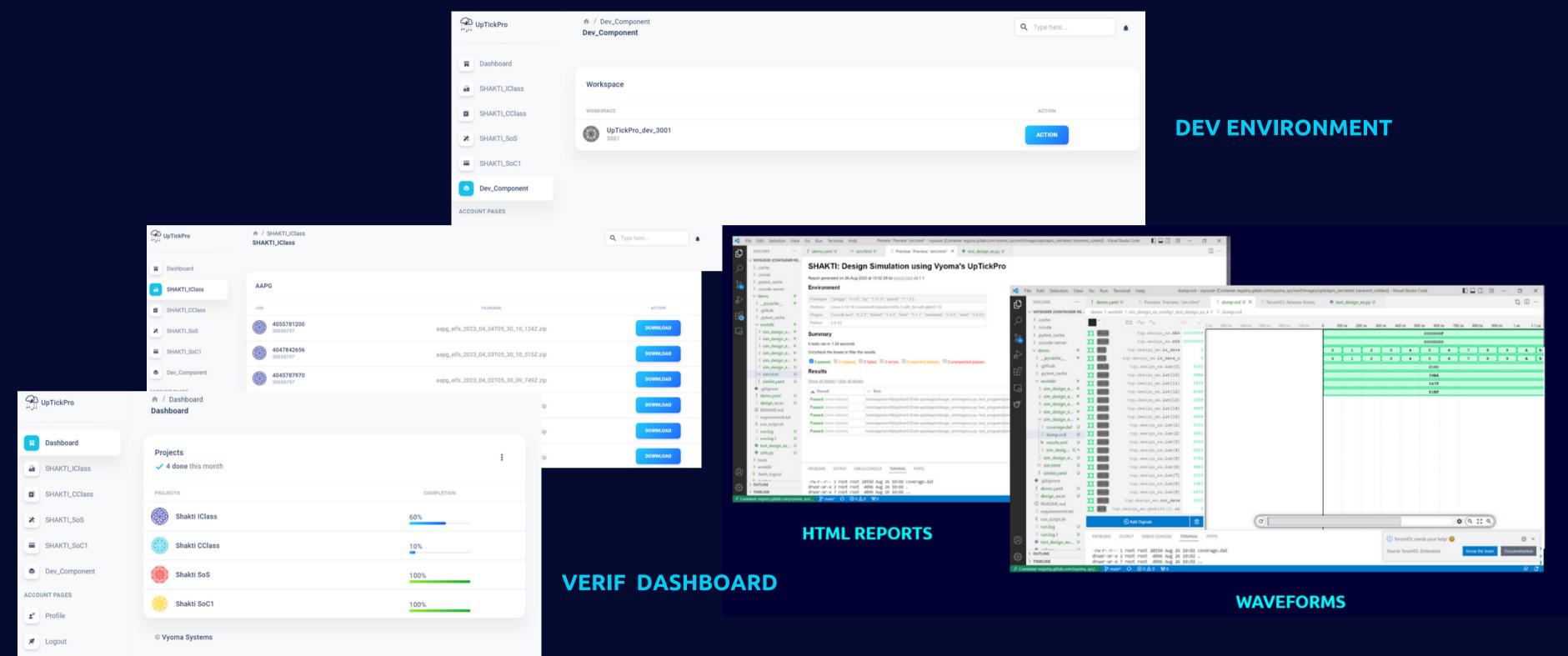

# Vyoma: Verification-as-a-Service Platform

**Ensures RISC-V Design Quality**

Test suites & Generators for end-to-end verification completeness

Scalable Test Infrastructure

# UpTickPro: Verification DevOps

# Team

Lavanya J CEO/Founder 11+ years of industry experience (with IBM, ARM & Rambus) with an MS from IIT Madras. Passionate about making design verification

Rizwana G SaaS Lead Architect 7+ years of professional experience in the software field with an undergrad degree from Anna University. Owns DevSecOps for Vyoma's SaaS Implementation.

Prof. V. Kamakoti Honorary Mentor Director at IIT Madras. Visionary for a semiconductor Atma-Nirbhar Bharat. Pioneering India's first RISC-V processor designs (SHAKTI)

Sundara Nagarajan Scaleup Advisor

An industry veteran in the Computer Systems industry; career technologist, and product development leader. Currently Managing Director of Innovation Scaleup Advisors, a firm that empowers tech founders to build scalable firms.

# Thank You

Contact Us: lavanya@vyomasystems.com