## JUMPING IN THE DEEP END A GRADUATE'S PERSPECTIVE ON VERIFYING AN ADVANCED AI CHIP

## GRAPHCORE

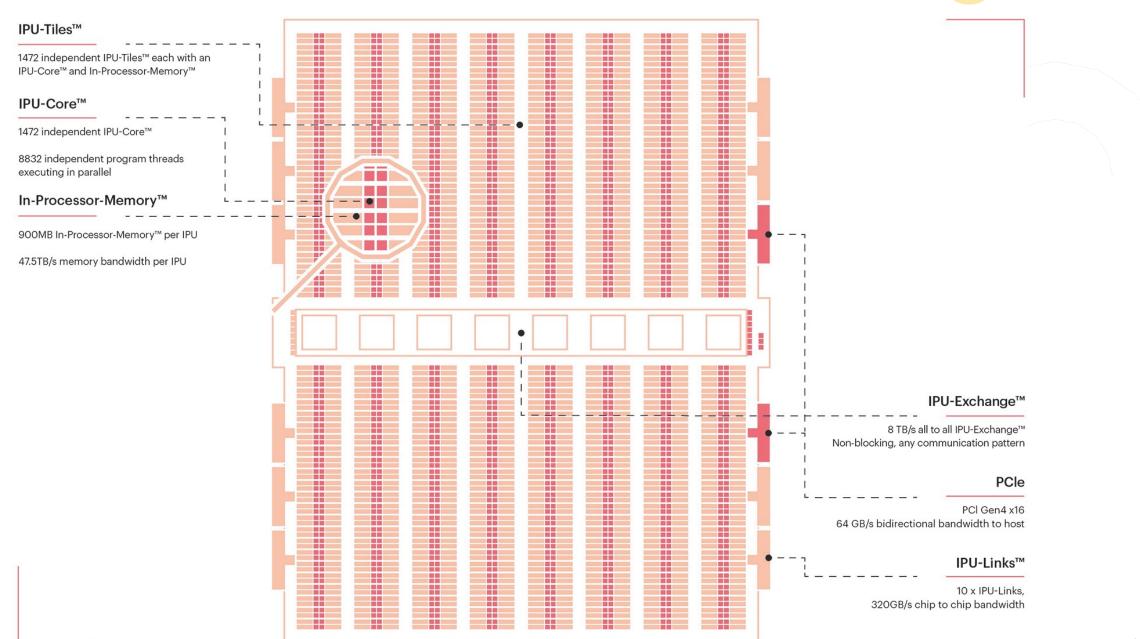

## **GRAPHCORE IPU**

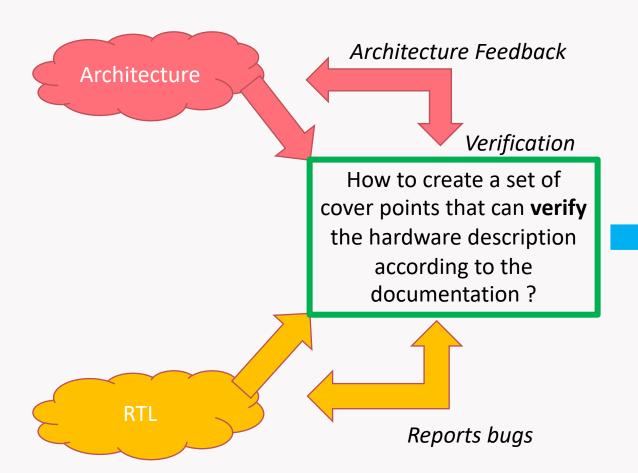

# GRADUATE VERIFICATION EXPERIENCE

## **GRADUATE EXPERIENCE – LOGAN (CORE VERIF)**

- **1.** You will get a full <u>understanding of the</u> <u>architecture</u>. You will be able to find possible improvements and to give some feedback.

- **2.** You will have a good <u>understanding of the</u> <u>hardware design</u> to create specific verification patterns.

- **3.** You will learn to find a subset of the CPU state space that is optimal for verification which means not computationally expensive and that ensures hardware high reliability.

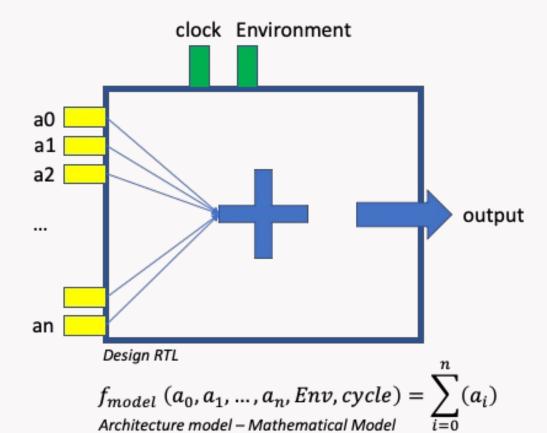

### **VERIFICATION CHALLENGE**

#### What about brute force?

- If n=1 (a0, a1), we have  $2^{64} \sim 10^{19}$  combinations for 32-bits inputs

- AMD RADEON 8 TFLOPS ~ 10<sup>13</sup> op/s

- We would need  $10^6$  sec to compute everything which means 1,7 week

This is a lower bound!

#### What is behind the Environment variable?

#### What about the mathematical model?

· Can we rely on the addition done on the AMD core?

#### Conclusion

We need to find a better way!

### Can we rely on the following property?

$$f_{model}\left(a_0, a_1, \dots, a_n, Env, cycle\right) = f_{model}\left(a_1, a_0, \dots, a_n, Env, cycle\right)$$

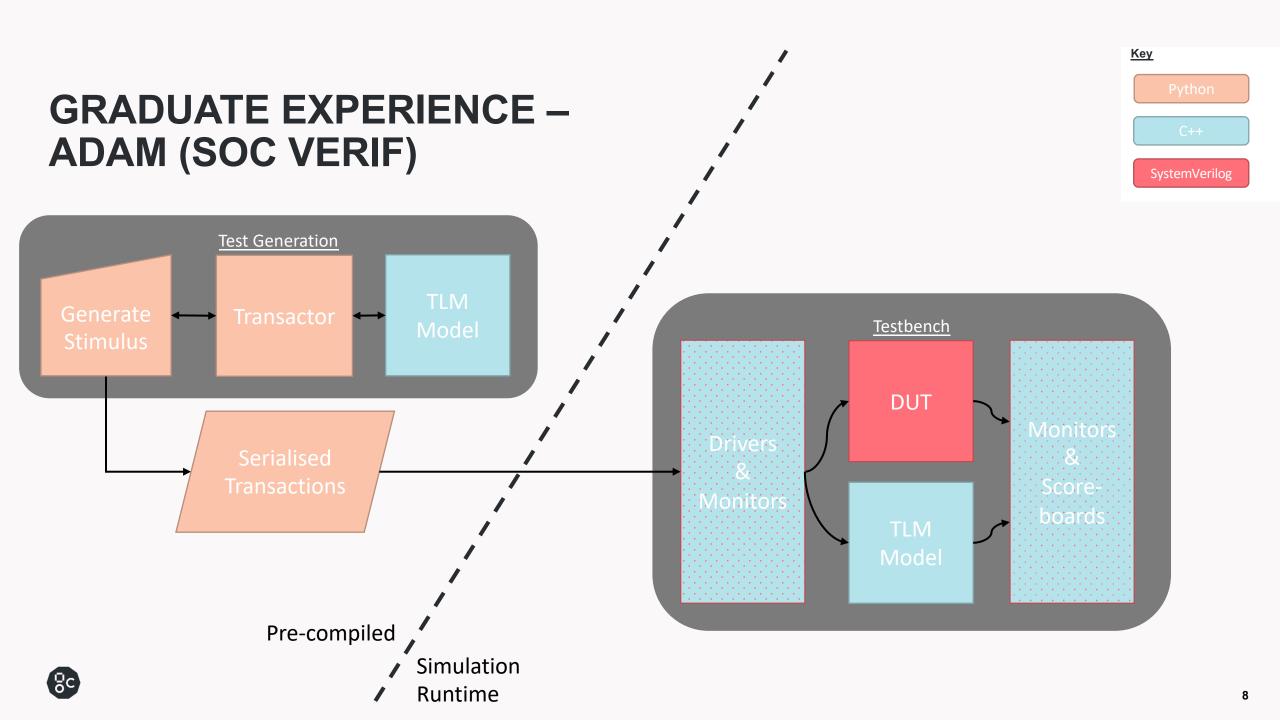

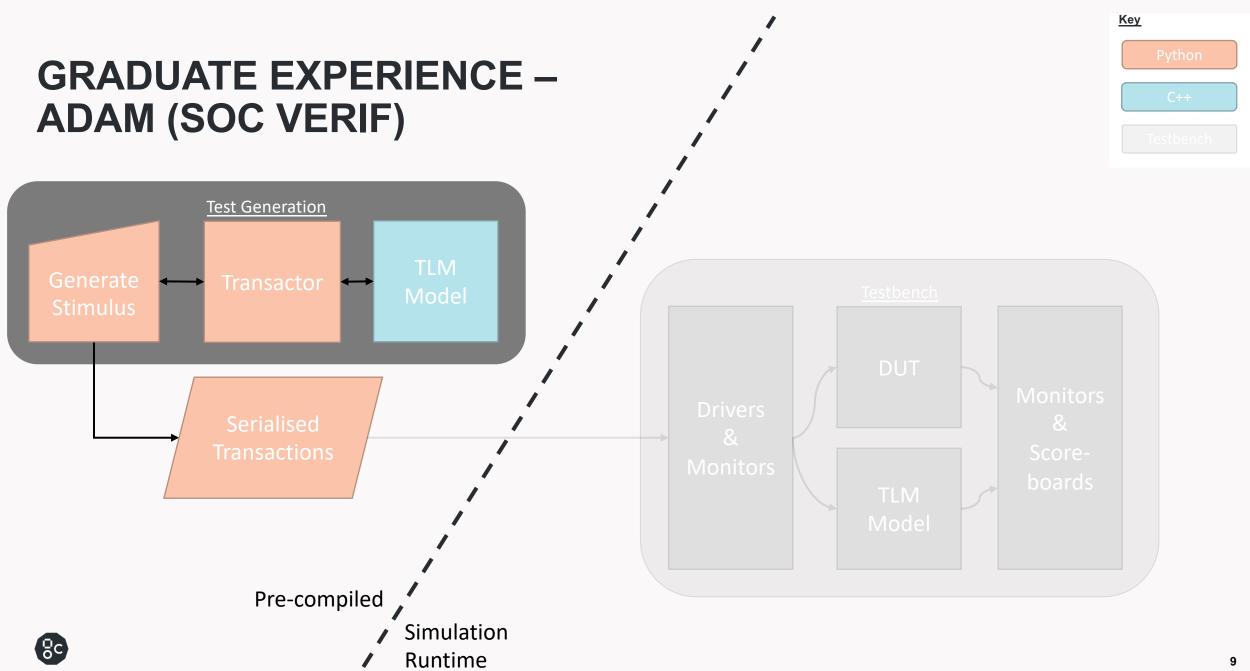

## **GRADUATE EXPERIENCE - ADAM (SOC VERIF)**

- Joined Graphcore's Physical Design team in 2020

- Moved into SoC Verification in 2021

- Enjoying using Graphcore's verification methodology

- The verification work can feel very "software-like"

- Exposure to Python, C++, SystemVerilog, ...

- High-level object-oriented programming

- No more Tcl scripting

## GRADUATE EXPERIENCE – MIHAI (CORE VERIF)

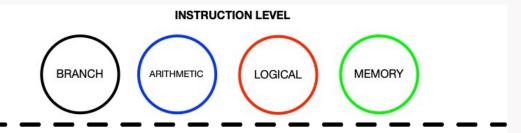

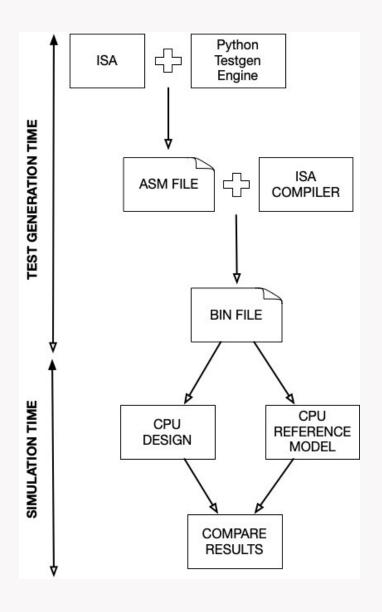

#### **INSTRUCTIONS GENERATOR**

#### SEQUENCE LEVEL

#### PROGRAM LEVEL

INTERLEAVE INSTRUCTIONS FROM SEQUENCES

#### **Randomness**

- operands and immediate values

- different instructions order

- different CSR values, BOOT options, interrupts, debug interface

## GRADUATE EXPERIENCE – MIHAI (CORE VERIF)

Chip roadmap

-> from design spec to product

Exposure to different EDA tools

WHY VERIF AT GRAPHCORE

Expand knowledge in Logical, Physical, DFT

Tasks diversity which requires:

Databases, Regular expressions,

Power Analysis, Design Patterns,

Multithreading Programming

# **GRADUATE SOCIALISING**

## WHERE TO FIND US

Q<sub>C</sub>

https://www.graphcore.ai/early-careers

students@graphcore.ai

https://www.linkedin.com/company/graphcore

https://www.youtube.com/c/Graphcore/videos

## **THANK YOU**

Adam, Logan, Mihai students@graphcore.ai